CTCS3-300T车载设备测速测距单元硬件改进方案研究

2020-04-28贾云光

贾云光

(1.北京全路通信信号研究设计院集团有限公司,北京 100070;2.北京市高速铁路运行控制系统工程技术研究中心,北京 100070)

1 概述

1.1 CTCS3-300T简介

CTCS3-300T 的 测 速 测 距 单 元(SDU)是CTCS3-300T 列控车载设备对列车速度进行监测的重要前端环节,其可靠性和准确性直接影响了整个系统性能指标。

伴随着CTCS3-300T 列控车载设备的大量装备以及长时间运行,列控车载设备在运行过程中出现了许多无法解决的偶发性故障,其中最具代表性的是SDU 表现出的偶发性故障。在我国,高铁运行的可靠性和安全性要求在世界上居于前列,即使故障率较低的偶发性故障,也逐渐成为了人们出行关注的焦点,本着对高铁运输高品质的更高追求,偶发性故障解决也成了技术人员势必攻克的难点。

众所周知,定义为偶发性故障就说明该故障解决难度较高,因其偶发性、不容易复现,故障解决就无从入手。本文介绍了如何解决和查找该问题并提出优化方案,以便为后续解决类似问题提供可借鉴的思路和方法。

1.2 测速测距单元偶发性故障情况

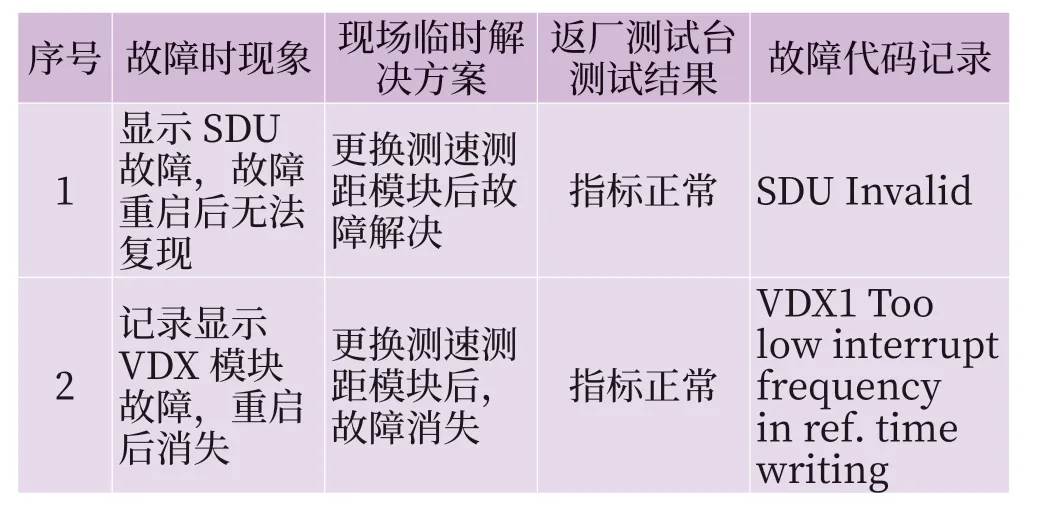

经过运营统计及技术人员初步分析,CTCS3-300T SDU 的偶发故障现象及记录主要如表1 所示。

表1 测速测距单元偶发性故障现象Tab 1 SDU accidental fault phenomenon

表1 中所述两种故障,在设备更换SDU 模块后,故障不再出现。但是设备返厂后,各项测试指标正常,即生产人员和技术人员均无法确定该模块的故障点,判定为偶发性故障或总线干扰所致。

2 存在问题及分析

2.1 问题查找及分析

偶发性故障在现场很难复现,通过对现场故障长时间统计,锁定偶发故障率相对较高的车载设备单元,在室内测试环境中进行长时间拷机测试以及施加各种技术手段,个别模块故障最终得以复现,主要出现以下3 类故障,且涵盖现场故障记录,如表2 所示。

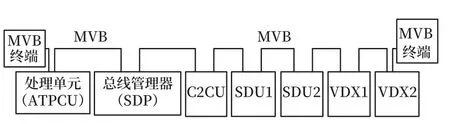

CTCS3-300T 系统中,ATP 通过总线管理单元(SDP)管理各个模块,总线结构如图1 所示,SDU通过MVB 总线与CTCS3-300T 车载设备中的各个单元进行连接。当SDU 需要在总线中发送或者接收数据时,会将自己的MVB 管理芯片MVBC01 设置为不同的电平状态,从而获得总线发送数据的相应权限。

表2 测试测距单元室内测试故障记录Tab 2 Fault record of SDU indoor test

图1 CTCS3-300T MVB总线拓扑图Fig.1 Topology of CTCS 3-300T MVB

上述3 种故障,均由SDU 单元引起,却体现为其他单元的故障记录,因此判定:SDU 的MVBC01 在读取或写入总线时存在异常。在确定问题初步原因时,就需要对SDU 的相关电路进行分析和研究,确定故障根源,找到优化方案。

2.2 原理图分析

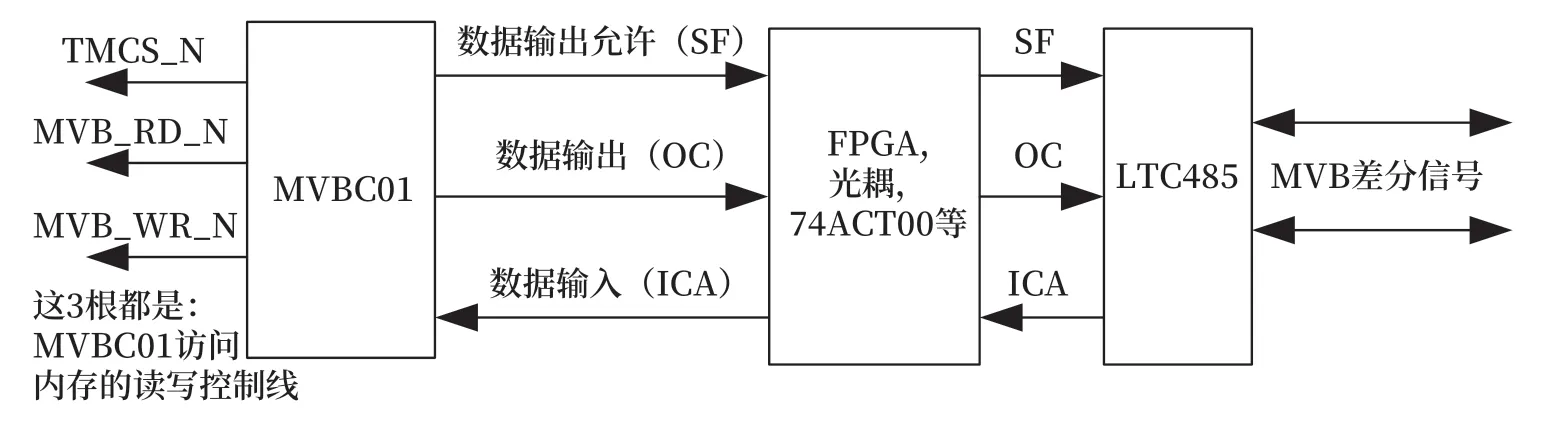

SDU 单元主要由两块电路板组成:IOCPU 板和扩展板,IOCPU 负责MVB 通信及相关逻辑,扩展板用于速度信息的采集。MVB 芯片周边电路如图2 所示, MVBC01 芯片通过FPGA 芯片连接到485 芯片向总线收发数据。

详细电路如图3 所示。

MVBC01 芯片为MVB 控制芯片。有3 根引脚控制信号输入,输出和输出允许。通过示波器连接3 个引脚观察在发现相关故障时其引脚与故障现象对应的关系,经过测试和分析发现存在如表3 所示的对应关系。

图2 测速测距单元MVB电路结构图Fig.2 Circuit diagram of SDU MVB

图3 MVB周边纤细电路图Fig.3 MVB peripheral thin circuit diagram

表3 MVB控制信号与故障现象的对应关系Tab 3 Correspondence between MVB control signal and fault phenomena

由表3 可知在相关故障发生时,其原因是相应管脚运行时电平出现异常导致某一管脚固定在高电平或低电平。为了进一步分析导致高低电平的原因,对电路原理图进行分析,基本确定了如下部分电路可能存在问题:

1)LTC485 存在问题;

2)FPGA 存在问题;

3)MVBC01 存在问题;

4)其他问题。

为排除器件本身存在批次问题,测试采用替换方法,经过反复试验,最终排除了器件批次质量问题。

2.3 问题发现

在排除了各种因此器件质量问题导致的因素之外,重新对MVBC01 控制LTC485 的引脚进行监测分析,发现在一定时间内存在输出不稳定。而造成这种不稳定因素主要可能来自干扰。

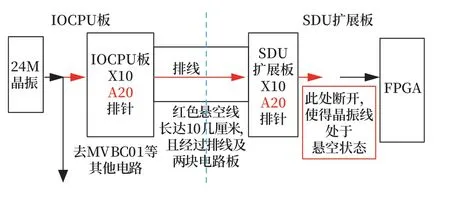

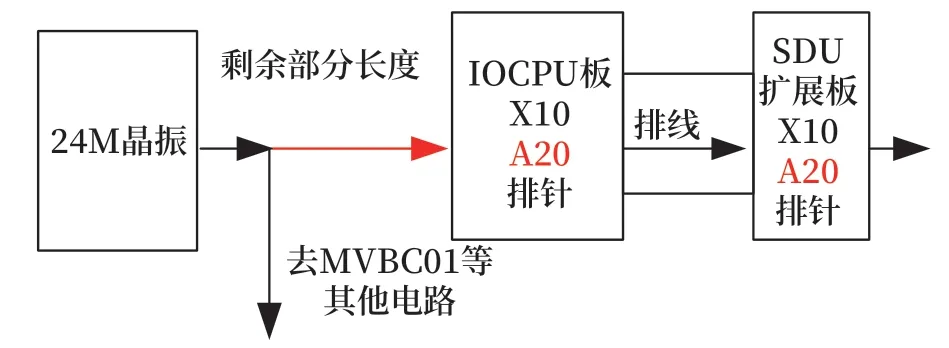

经过对电路板电路及PCB 仔细分析发现,SDU的CPU 板上的24M 晶振除了给MVBC01 使用以外,还通过长的PCB 线引到X10 排线,再经排线引到IO 板。VDX 的IO 板这条线是直接接到芯片的。但SDU 的IO 板这条线是悬空的,如图4 所示。

如此长的悬空线,会因PCB 布线及各部分阻抗的不同,导致作为天线将空间电磁干扰引入电路从而导致设备出现问题。

图4 晶振悬空线示意图Fig.4 Schematic diagram of crystal suspension line

为验证对干扰来源的分析,进行如下测试。如图4 所示,在晶振悬空线上,人为加入短暂干扰,然后恢复,出现如表4 所示的3 种结果。

从表4 中,可以看出,短时的干扰确实能够造成设备的死机,并能够复现现场故障,从而验证逻辑分析的正确性。

3 改进方案

3.1 优化方案

根据电路及测试验证,晶振延长线是导致MVC01 偶发死机的根本原因,其引入干扰会出现现场偶发的3 种故障现象。为解决引入干扰的问题,需要切断引入干扰的辐射源,根据电路改造及优化的可行方案,提出如下3 种优化方案。

1)取消晶振延长线设计,从设计源头防止该问题的发生。

2)在晶振延长线末端,加入高阻抗电阻。

3)优化PCB 版布局,改变晶振延长阻抗。

方案1:设计优化

晶振延长线设计原本是用于VDX 单元的电路设计,在SDU 中由于没有相关电路设计,因此该悬空线应该从设计上去掉,如图5 红色虚线部分。

图5 方案一 设计优化原理图Fig.5 Scheme 1 Schematic diagram of design optimization

方案2:在晶振延长线中串入电阻

天线设计中,改变天线阻抗可以降低天线接受外界电磁波的能力,因此在晶振中串入高阻抗的电阻,可以有效降低外界串入晶振延长导致的干扰问题,如图6 所示。

图6 方案二 优化电路示意图Fig.6 Scheme 2 Schematic diagram of optimized circuit

方案3:缩短晶振延长

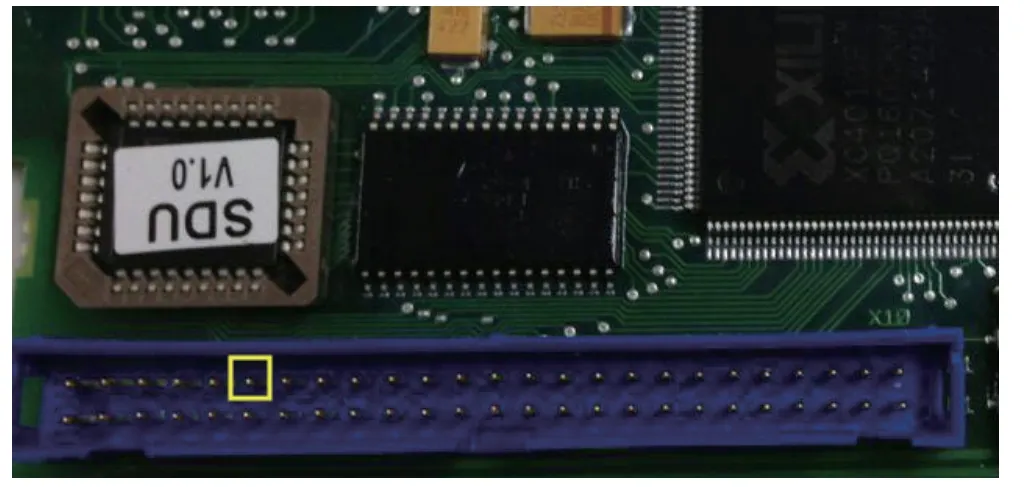

如图7 中红色部分所示,是将IOCPU 板上的A20 针拔除。这样,24 MHz 晶振线上悬空只有3 cm 左右,大大缩短了晶振延长线,从而能从很大程度上降低干扰。

图7 方案三 优化原理图Fig.7 Scheme 3 Schematic diagram of optimization

3.2 方案比较及优选

3.1 节中的3 种方案都可以解决测速测距单元存在问题,对比3 种方案,综合考虑工程实施难度,选择方案3,原因如下。

方案3 中晶振延长线原本悬空,拔除CPU 板上的X10-A20 后,原理上对整个电路图没有任何改动,对电路的功能没有任何影响,如图8 所示。

图8 方案实施的A20针脚位置图Fig.8 A20 pin location map in scheme implementation

对于中长期考虑,应从设计上根本解决电路设计问题,方案一无疑是最佳的解决方案。

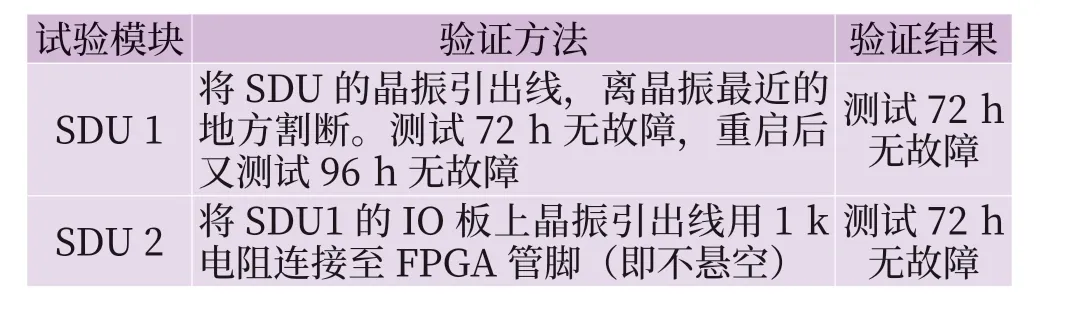

3.3 测试及验证

使用两个SDU 测试,这两个SDU 原来均能在24 h 内复现故障。针对两个SDU 采取不同的措施进行验证,如表5 所示。

表5 测试验证结果Tab 5 Test verification results

后恢复两个模块,故障在24 h 内复现,综上,晶振延长线的悬空是导致问题出现的原因。

4 总结

本次改进方案已经在全路2000 套CTCS3-300T 级列控车载设备上进行了应用,经过近一年多的观察,该偶发性故障未再发生,效果良好,测速测距相关类故障下降50%。