基于DDS 信号生成原理的压电驱动装置电源设计*

2020-04-25贾丹平王海燕

韩 硕,贾丹平,张 涛,王海燕

(1.沈阳工业大学信息科学与工程学院,辽宁 沈阳 110870;2.中国科学院网络化控制系统重点实验室,辽宁 沈阳 110016;3.大连理工大学电气工程学院,辽宁 大连 116024;4.沈阳白云机械有限公司,辽宁 沈阳 110000;5.中国科学院沈阳自动化研究所,辽宁 沈阳 110016;6.中国科学院机器人与智能制造创新研究院,辽宁 沈阳 110169)

0 引 言

压电驱动装置是一种由新型智能材料压电陶瓷元件[1-2]制成的高精度运动电机设备[3-4],它具有体积小、推力大、噪声小和发热率低等特点,被广泛应用在微电子测量、光学仪器和纳米技术等领域[5]。依据电路原理分类可知,压电陶瓷元件属于一种容性负载。在理想的条件下,压电陶瓷元件伸缩长度跟输入两端的电压成线性关系,响应速度跟信号的输入频率有关。本文综合大量的理论研究,设计了一种驱动该负载的电源。

传统频率合成技术是依靠振荡器产生单一频率信号,只能在很小范围内可微调而无法满足频率源的稳定度和精确度的要求。基于DDS 原理生成的信号具有极高的输出分辨率。当频率发生改变时相位连续、相位噪声低、集成度高以及可灵活产生多种信号等。与传统频率合成技术相比具有无法可比拟的优点[6]。现已经被广泛的应用到通讯、航天、军事、现代仪器仪表检测以及生物医学检测等领域。本文将该理论应用到压电陶瓷元件驱动领域,在大电压±250V 下产生了频率高达1.5KHz 任意信号,保证了在65nf 容性负载下的压电驱动装置波形不失真。实现了压电驱动装置大量程和高响应运动的功能。且通过搭建实验的方式验证了采用DDS 信号生成原理的驱动电源的有效性和实用性。

1 DDS 信号生成原理

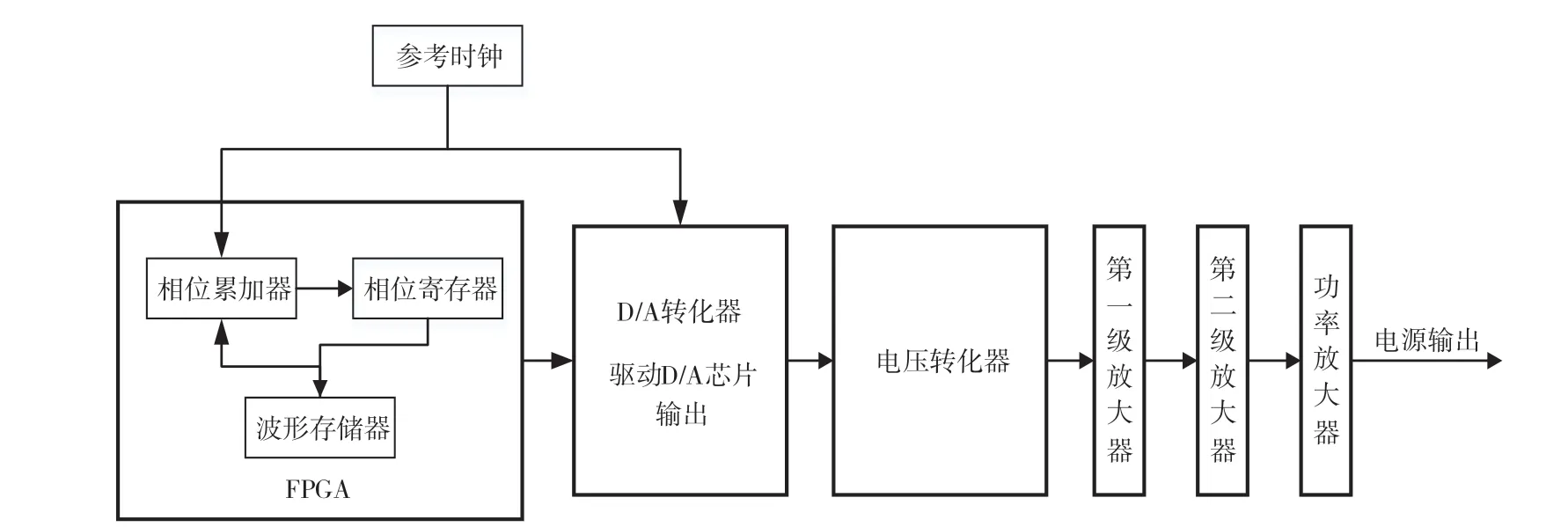

DDS 信号产生的理论基础是“奈奎斯特采样定理”[7]。在定理中可知当抽样频率大于等于模拟信号最高频率两倍时,就可以从离散序列无失真的信号中恢复出原始模拟信号。DDS 信号生成原理是对模拟信号进行抽样。当一个抽样过程已经发生且抽样值已经量化完成,从量化数值重建原始模拟信号。基本的 DDS 结构主要由相位累加器、波形量化数据存储器、D/A 转换器组成。其中相位累加器和波形量化数据存储器称为数控振荡器,是 DDS 结构中的数字部分。DDS 基本结构原理如图1 所示。

图1 DDS 基本结构原理

其中图中的输入频率为基准时钟频率,即fc。频率控制字为K。数据量化后的数据地址位数为N位,也是ROM 数据线位数。输出频率为fo。则输出信号频率与基准时钟频率之间的关系如下:

由式(1)可知,DDS 信号的最小分辨为:

结合式(1)和(2)可知,当改变输入的频率控制字就会改变DDS 合成输出的频率,但不能改变输出信号的最小分辨率。

DDS 信号发生器的数控振荡器部分主要是在FPGA 中实现的,也是DDS 信号产生的核心部分。本文中的驱动信号电源是基于DDS 信号产生原理设计的,其中基本的驱动电源设计流程结构图如下图2 所示。

DDS 信号发生部分是在FPGA 硬核中实现的。其中包括ROM IP 核、相位累加器和相位寄存器。D/A 转化器主要是采用FPGA 驱动PCM1702 构建的DDS 信号发生电路组成。其中PCM1702 是20 位高分辨率的信号输出芯片。ROM IP 核中量化的数据点越多,离散信号的线性度越好,信号输出的质量越高。但是数据点的多少受控于ROM 的数据线位数。本设计采用N=20,参考时钟fc=50 MHz,输出信频率为1.5 KHz,D/A 转化器输出电流信号为±1.2 mA。产生压电驱动装置所需要的驱动信号梯形波。

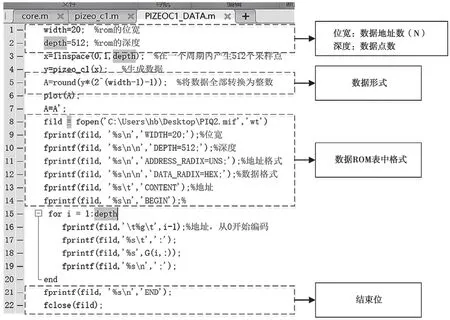

原Altera 公司的Quartus16.0 开发软件中提供了现成的ROM IP 核,其中需要加载(.mif 文件)文件中的数据应用到IP 核中,波形存储器初始化数据形式后,对数据进行整数化处理,以满足所输出的信号数据要求。.mif 文件中数据内容格式是使用MATLAB 工具生成所需要的信号数据,然后主控核心板FPGA 调用ROM 核填充文件的数据点。.mif 文件内容格式解析如下图3 所示。

图2 驱动电源设计流程结构

图3 .mif 文件内容格式解析

通过查表地址的方式,FPGA 实现了对于ROM IP 核中的数据调用。ROM 表尺寸与数据位数成2N指数增长关系,采用缩减查表地址和压缩ROM 表尺寸的方法可节省资源[8]。D/A 发生器应用Verilog语言程序驱动D/A 芯片生成所需的模拟电流信号,即将量化后的数据还原成波形输出。电流信号生成的参考时钟是50MHz,产生频率为1.5KHz。

以生成的梯形波为例,基于Verilog 语言的ROM IP 核数据输出的DDS 软件流程图如下图4 所示。

ROM IP 核完成1/4 梯形函数的数据存储后,需要设计地址扩展来生成其余3/4 的波形数据。正如图4 所示,当系统复位完成后,一旦检测到时钟上升沿,相位寄存器移位一步,累加器就累加一个步长,得到的相位数据值映射到地址查表中。第一、三象限地址取反,第二、四象限地址取补。其中数据宽度为20 位,以524,287 为中心分别输出正负半轴的波形量化幅度值数字量。

应用Quartus16.0 软件进行功能仿真得到的波形数字量如图5所示。其中clk为输入的参考时钟(晶振时钟),DA_dat1 为输出信号。改变相位增量可调节输出信号的频率,改变波形存储表内容可得到任意波形,仿真图中频率控制确定。由(1)式可知频率控制字可改变DDS 信号频率,在程序设计的过程中通常使频率控制字作为输入变量[9-11],进而实现了不同频率DDS 信号输出。

图4 DDS 软件流程

图5 中(a)、(b)、(c)、(d)图是以十进制无符号的形式展现。随着上升沿信号的触发使得ROM IP 核中数据开始输出。各个图中的数据量化点代表各个象限的数据离散点。(e)连续信号,是由各个离散点线性化组成的模拟信号。

2 驱动电路硬件设计

2.1 D/A 转化器设计

由查找表中读出的数字量幅度值是一串数字序列,最终要经过 D/A 转换器才能转换成相应的模拟波形输出。为了解决数据处理的准确性和模拟波形信号的质量问题,D/A 转换器必须有足够的转换精度。为了考虑 D/A 转换器的非线性和噪声特性,综合了各方面的因素之后,本文设计采用 PCM1702为波形发生主芯片。PCM1702 是一种高速处理芯片,其中信号以电流的形式输出。输出电流幅度值为±1.2mA。D/A 转换器硬件电路设计如图6 所示。

D/A 波形产生电路早期应用在音频放大电路中,具有响应时间快、低噪声干扰以及输出精度高等特点。为了实现信号的降噪和滤波作用,在电流信号经过电压转化器后,采用前级放大芯片OPA137 作为反向电压跟随器,构成的跟随电路具有滤波和降噪的功能。信号放大到±10V 输出。

图5 波形仿真数字量图

2.2 功率放大电路

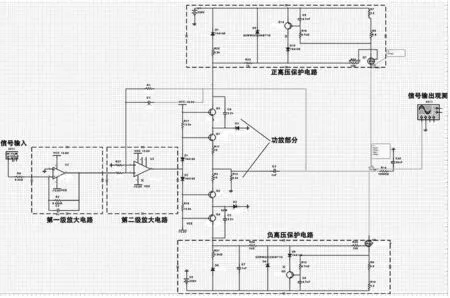

利用LM356 放大芯片进行了第二次反向放大,从而完成了整个前端信号发生电路的设计。为了驱动对象运行,需要对驱动信号进行功率放大。在本文中设计了一种高电压,小电流的功放模块。该放大模块是应用三极管的放大原理设计的,其中原因有两点,其一是信号频率较大,其二是信号的电压大电流小。且搭建了高电压信号保护电路。使用仿真软件Multisim14.0 对电路进行仿真和各个电压检测点进行观测。如图7 所示。

图6 硬件电路设计

图7 Multisim14.0 仿真电路

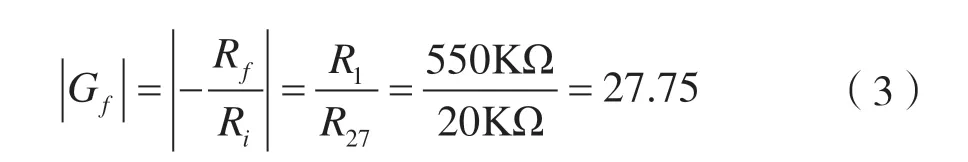

功放部分电路图由第一级放大开始,最后输出±250V 的电压信号。由于信号的频率较高,电路设计采用甲乙类三极管放大设计。为了满足整个实验的高电压输出的需求,采用高电压MOS 管对电压信号进行放大从而得到高电压任意波形信号。其中整个系统的增益放大倍数如下式(3)所示:

其中Gf为功放系统的增益放大倍数。Rf为放大增益电阻对应仿真图中的R1阻值。Ri为信号输入电阻对应仿真图中的R27阻值。在一定条件下,由电路仿真与设计可知Rf与Ri电阻比决定了功放部分电路中的放大倍数。本文按照实际要求放大到27 倍左右。

3 系统实验与信号分析

本文为了满足输出压电驱动装置运动的电源信号。频率控制字K 为固定的值,则相位增量就会相同,输出频率不变,当相位累加器的字长N 取32位时,将ROM 地址线位数定最高20 位。当设计中采用50 MHz 晶振,无倍频的情况下,频率分辨率达到0.012 Hz。由此如下式(4)得到的输出幅度分辨率为:

其中ΔVOUT幅度最小分辨率,VOUT数字量化电压,Gf为功放系统的增益放大倍数(与式3 中等意义)。为了验证应用DDS 原理信号质量问题,由相位截断误差引入的DDS 无杂散动态范围SFDR 为[12-14]:

其中为了满足功放模块的性能指标。综合压电装置的动态响应和实际状况,得到输出频率为fo=1.5 KHz。由综合式(5)可以近似得到DDS 无杂散动态范围SFDR 为[15]:

其中本文取N 和B 取值分别为32、20。可知DDS 无杂散动态大于等于72.24 dB,满足信号输出质量要求。为了验证基于DDS 原理设计的压电驱动装置电源能够达到压电驱动装置正常运行的目的。建立如下图8 所示的系统实验平台。

图8 系统实验平台

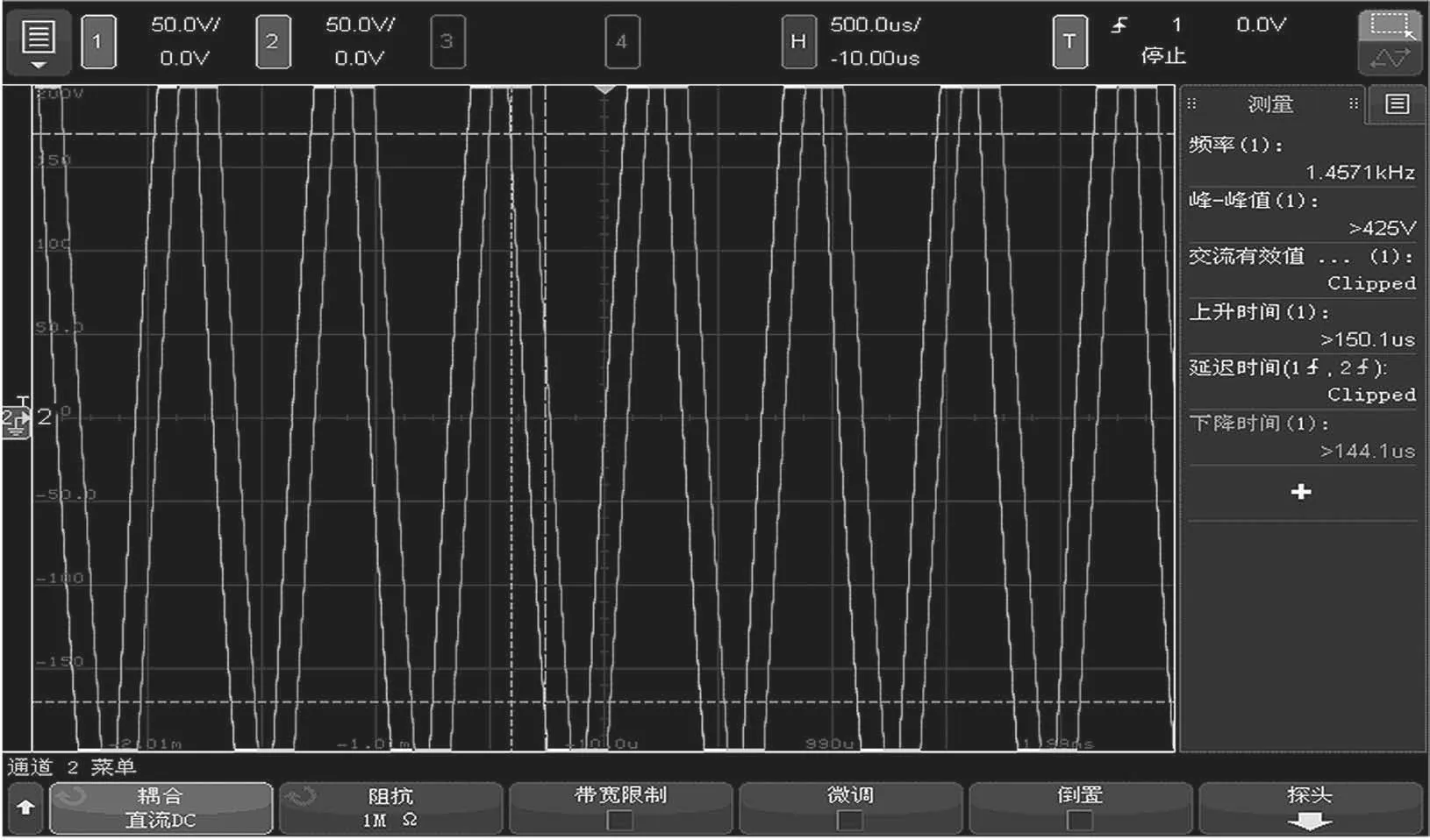

该实验平台主要由电源部分、驱动器和检测系统组成。电源采用±250 V 线性可编程电源和±15 V开关电源分别供电功率放大模块以及运放供电部分。驱动器由多核处理器、FPGA 和DDS 信号发生器组成。由上层的PC 控制驱动信号输出和观测运动实际轨迹曲线,其中输出驱动信号由示波器进行观测,示波器型号为KEYSIGHT。应用激光干涉仪作为位移测量系统。为了验证该电源的信号质量,应用示波器观察驱动信号输出如图9 所示。

图9 DDS 信号梯形波

依据图9 示波器观测到的梯形波信号,实际测量输出频率为1.4571 KHz,其中频率精度误差为0.98%左右。在±250 V 电压输入的情况下,实际测量的电压输出峰峰值为495.5 V。其中输出电压精度误差为0.9%。因此证明了DDS 信号生成原理的驱动电源是具有可行性的,所带来的误差可能是信号线缆引起的。

应用激光干涉仪测得压电驱动装置的运动轨迹图如图下10 所示。其中检测装置采用的是高精度4 Khz采样率的激光干涉仪设备对运动步长进行位移采集。

图10 压电驱动装置运动轨迹

由图10 可知应用DDS 原理设计的信号驱动电源驱动了压电驱动装置运动,应用本文的方案解决了压电装置的运动问题。

4 结 语

本文完成了基于DDS 原理设计的压电驱动装置电源。使用FPGA 实现了DDS 结构系统的整体过程。通过实验和理论证明,应用本文的方案可以驱动压电装置运行。实现了±250 V 信号输出,频率最高可达1.5 KHz 梯形波信号。搭建驱动电源测试平台中,证明了信号输出的质量高和精度高,验证了采用DDS 信号生成原理的驱动电源的有效性和实用性。