基于SW1621 处理器的双控阵列研究

2020-04-13何云龙

◆何云龙

(上海领存信息技术有限公司 上海 201101)

截止到2020 年,全球数据总量已经达到40ZB[1]。如何高速、高可靠、高可用、高安全地将这些数据存储起来,成为越来越多研究者亟待解决的技术难题。

近年来,“棱镜门”、“中兴事件”、“中美贸易战”等一系列涉及信息安全的问题爆发,我国逐步加大党政、军工、金融等关键领域信息设备的国产化升级工作。本文研究的基于国产申威SW1621 处理器的自主可控高端双控阵列,可解决关键领域数据的高可用存储问题。

1 双控阵列的工作原理

(1)双控制器冗余机制

双控阵列采用两个配置完全相同的控制器作为冗余阵列,可避免单控制器发生故障,提高存储系统的可用性。不但控制器需冗余,而且阵列中的电源、风扇及心跳信号等硬件资源也都需冗余。

(2)工作模式

双控阵列可以分为主备和双活两种工作模式。主备模式下,两个控制器被分为主控制器和备份控制器。客户端通过主控制器来访问阵列,备份控制器通过心跳信号实时检测主控制器的状态。当主控制器发生故障时,备份控制器会主动接管主控制器的业务,并将备份的缓存数据同步至硬盘中[1]。

双活模式下,客户端可通过任何一个控制器来访问阵列。两个控制器要分别备份对方的缓存,并同时相互监控对方状态。当其中某个控制器发生故障时,另一个就会重新接管数据业务,并将缓存实时写入硬盘中[2]。

(3)高速数据同步链路

文中的存储阵列使用万兆以太网接口作为高速数据同步链路,并采用TCP/IP 协议来保证数据的可靠传输。

(4)心跳模块

心跳模块每隔一段时间发送心跳包给对方,如果没有收到心跳包,就认为控制器发生了故障。本文研究的双控阵列中的心跳模块采用了多种不同的冗余低速链路,用来确保心跳信号正常接收。

2 基于SW1621 处理器的双控阵列系统架构设计

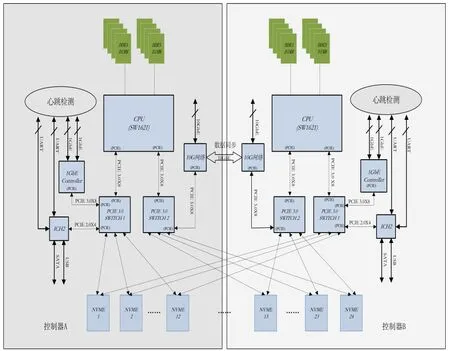

双控阵列的设计目标是为了保证整个系统“数据不丢,任务不断”。当其中出现故障时,能将存储业务平滑迁移。阵列硬件平台架构如图1 所示。

双控制器均为SW1621 16 核处理器的高性能计算刀片。24个双端口的NVME SSD 通过无源背板和计算刀片实现高速连接。每一个NVME SSD 的两个端口分别对应着两个控制器。双控制器、SSD 以及无源背板之间采用无线缆设计,将会大大减少信号间的串扰。

3 基于SW1621 处理器的双控阵列硬件设计

阵列整机采用19 英寸2U 上架式机箱,每个控制器单元为1U 高度。整机电源、风扇模块也采用1+1 冗余备份的方式,每个电源模块均选用750W 交流输入电源,并分别位于整机两侧。风扇模块位于机箱前端,采用前后通风的散热方式,整机实物图如图2 所示。

图1 基于SW1621 处理器的双控阵列系统架构框图

图2 基于SW1621 处理器的双控阵列整机实物图

3.1 基于SW1621 处理器高性能计算刀片的硬件设计

刀片以SW1621 处理器为计算核心,完成阵列业务数据流的管控和调度以及系统数据的高速密集计算。

刀片对外引出多路PCIE 插槽,通过扩展外接PCIE 网卡的方式来实现阵列缓存数据同步和心跳信号检测。万兆网卡可提供两路万兆网口,其中一路用于双控之间的数据同步,另一路用于阵列对外提供存储服务。千兆网卡扩展两路千兆网口,用作心跳信号连接。硬件功能框图如图3 所示。

SW1621 处理器对外引出2 路8x PCIE 3.0 接口,统计刀片所需的PCIE 资源,通过外接2 个PCIE 3.0 交换芯片对实现外围接口的扩展。

PCIE 3.0 交换芯片1 用于连接包括12 个NVME SSD、BMC芯片和千兆以太网卡在内的各个接口功能电路:

●12 路4x PCI-E 3.0 接口,连接12 个NVME SSD,用作阵列数据存储;

●1 路4x PCI-E 2.0 接口,连接PCIE X4 插槽,用作千兆以太网接口;

●1 路1x PCI-E 2.0 接口,连接BMC 芯片,提供刀片健康状态信息管理;

●PCIE 3.0 交换芯片2 用于连接包括另外12 个NVME SSD、ICH2 套片和万兆以太网卡在内的各个接口功能电路:

●12 路4x PCI-E 3.0 接口,连接12 个NVME SSD,用作阵列数据存储;

●1 路8x PCI-E 2.0 接口,连接PCIE X4 插槽,用作万兆以太网接口;

●1 路4x PCI-E 2.0 接口,连接ICH2 套片,提供外围IO 接口(如SATA、USB、SPI 以及UART 等接口),供系统调试使用。

图3 刀片硬件功能框图

3.2 基于申威处理器双控阵列背板的硬件设计

阵列背板为2U 无源背板,用于2 块1U 计算刀片、2 块电源模组和24 块NVME SSD 的连接,从而实现对供电信号、SSD 信号、风扇控制信号和心跳信号连接的作用。其硬件设计框图如图4 所示。

图4 背板设计框图

4 基于SW1621 处理器双控阵列的软件设计

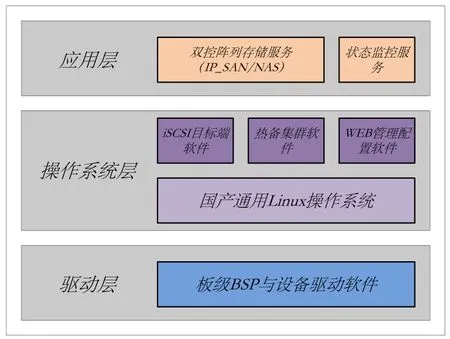

阵列软件采用模块化、标准化、层次化的体系架构。其自下而上分别为板级BSP 与设备驱动、双控存储专用存储操作系统、存储阵列管理软件及WEB 管理配置软件等四个部分,软件总体架构框图如图5 所示。

4.1 基于SW1621 处理器高性能计算刀片BSP 与设备驱动

BSP 提供了专用存储操作系统与硬件平台的基本接口,其作用包括:

(1)负责刀片上电时芯片的初始化;

(2)对操作系统访问芯片提供驱动支持;

(3)衔接操作系统与底层硬件;

(4)实现板级芯片的适配及调优工作。

图5 阵列软件总体架构框图

4.2 基于SW1621 处理器双控专用存储操作系统

本文研究的专用存储操作系统是在国产睿思通用操作系统的基础上,加上专用阵列管理软件构成。阵列管理软件主要由三个部分组成:iSCSI 目标端软件、热备集群软件和WEB 配置管理软件[3]。

(1)iSCSI 目标端软件

本文研究的存储阵列可通过以太网接口对外实现IP_SAN 或NAS 等存储服务。目前,通用Linux 操作系统有对iSCSI 系统专门的支持,称之为iSCSI-SCST。iSCSI-SCST 目标端驱动封装在内核态,可以减少系统调用率,从而提高系统性能[4]。

为解决内核态的SCST 的锁竞争问题,通过对专用存储操作系统内核的优化改造,可使磁盘阵列的逻辑卷能够高效导出,更好地为用户提供网络存储服务。

(2)热备集群软件

热备集群软件主要负责双控阵列的故障监测、故障切换和缓存数据备份等功能。热备集群软件主要包括:虚拟IP、共享卷组、复制逻辑卷和脑裂等多种技术[5]。

为了让阵列更大限度提高硬盘利用率,实现故障快速重构,在热备集群软件中还加入了RAID2.0 管理技术。利用RAID2.0管理技术,可以将阵列中的所有存储资源进行池化,从而更加高效地实现数据保护。

(3)Web 配置管理软件

Web 配置管理软件采用SNMP 管理协议。它采用独特的方式使网络管理者和代理进程之间相互作用,来实现对远程资源的访问及控制。可让用户更方便地使用双控阵列,使其置于网络管理之下。在本文所研究的双控阵列中,用户可通过管理网络登录WEB 页面,远程配置管理阵列。

5 结束语

为摆脱国外大厂商对高端存储行业的垄断,突破高可用存储核心技术,研制一款自主可控的高可用存储阵列非常重要。本文研究的自主可控高端双控阵列,具有良好的扩展功能,支持基于高速网络的海量数据共享,数据访存高效、安全、可靠,可满足军用云计算、关键领域大数据应用等大规模存储需求。

但在国产处理器性能不足的前提下,还存在如何提高网络访问效率、如何更好地使用RAID2.0 技术、如何做好全局负载均衡等问题,解决这些问题将成为下一步研究的主要内容。