多片国产FPGA加载方式的探讨*

2020-03-25沈佐峰梁文婷

沈佐峰,梁文婷

(中国电子科技集团公司第三十研究所,四川 成都 610041)

0 引 言

现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)以其高灵活性、丰富的逻辑和I/O资源,在电子、通信领域应用越来越广泛。众所周知,目前FPGA市场被Xilinx、Lattice、Alter(已被Intel收购)及Actel(已被Microsemi收购)4家美国公司垄断。国家对核心关键芯片的国产自主化日益迫切的需求,促使国内厂家近年来大力发展FPGA设计和制造产业,涌现出一批优秀的FPGA厂家,如上海安路、高云半导体及京微齐力等。但是,上述国内厂家由于工艺和技术上的限制,芯片性能一定程度上落后于国外几家大厂。因此,通常FPGA在国产自主可控设备的工程使用上,由于性能的不足,需通过多片FPGA功能分隔完成工程化应用[1]。

目前,无论国内外厂商,FPGA的制造工艺大多数基于SRAM工艺。它具有易失性,FPGA在每次上电后需要重新进行配置加载。配置加载传统采用单片FPGA单独配置一个PROM的方式,以实现FPGA程序的非易失和上电自动加载。但是,该方式费时费力,一旦FPGA板卡装入整机后再进行程序的修改或升级,必须通过开箱后连接下载电缆实现,整个过程非常繁杂。

针对上述情况,本文提出了3种解决方案:第一种通过MCU采用菊花链的方式实现两片或多片国产化FPGA程序的加载;第二种通过MCU配置和更新FPGA的程序存储FLASH,再实现从FLASH启动FPGA;第三种是直接通过MCU加载FPGA。

1 FPGA配置加载原理

目前,针对国内外FPGA产品在配置方法,配置引脚功能设置及配置接口时序基本完全相同。这里以上海安路信息科技有限公司的AL3A10BG256为例进行原理介绍[2]。AL3A10BG256共有7种配置方式可选择,分别是主动串行(Master Serial,MS)、从动串行(Slave Serial,SS)、从动并行(Slave Parallel,SP)、主动并行(Master Parallel,MP)、快速SPI、标准SPI和JTAG配置模式。配置模式由MSEL[0-2]3个模式选择信号确定。

AL3A10BG256芯片的配置过程包含3个步骤:

(1)在芯片上电复位或者系统复位信号有效后进入复位阶段,等待内部信号和电源稳定后,系统开始进行初始化和内部配置信息清除过程;

(2)当芯片初始化完成后,FPGA开始接受配置数据写入;

(3)数据写入完成后,FPGA芯片进入启动阶段。

AL3A10BG256的配置引脚分为专用配置引脚和复用引脚,复用引脚配置完成后可以用一般IO使用。专用引脚包括配置模式选择引脚(MSEL[0-2])、配置时钟引脚(CCLK)、配置开始信号引脚(PROGRAMN)、配置完成引脚(DONE)、配置错误指示引脚(INITN)、从模式配置片选引脚(CSN)及边界扫描相关引脚(TDI、TDO、TMS、TCK)。复用引脚包括配置级联片选、数据输出脚(CSON/DOUT)、SPI模式片选输出(SPICSN)和配置数据输入引脚(D[7:0]),其中D[1]还可以做为MSPI模式下的MOSI,D[0]还可以作为从模式下的DIN和MSPI模式下的MISO。DONE和INITN是开漏输出,需采用电阻上拉。

在初始化过程中,如需要重新下载配置数据,拉低PROGRAMN引脚后,系统进入初始化过程。初始化过程中,FPGA将清除内部所有配置点,复位内部寄存器。在数据写入阶段,INITN信号变为高电平,此时用户配置数据开始写入AL3A10BG256。在启动阶段,FPGA释放DONE信号、释放全局三态信号GTS、释放全局复位/置位信号GSR及释放全局写使能信号GWE。

2 系统实现方案

2.1 多片FPGA级联方式

安路公司FPGA支持两种级联方式:一种是JTAG方式下的级联(即通常说的菊花链);另一种是从动模式下(SP/MP)的联级。

2.1.1 JTAG级联加载

JTAG级联加载相对比较简单,如果要下载到FLASH,则只支持三级级联,如图1所示。

图1 JTAG级联硬件

JTAG级联在TD软件中需要进行设置,先把需要加载的多个bit文件加入,并生成SVF文件,然后设置level,即可下载。如果是单级,则直接下载bit文件。安路的FPGA和国外FPGA在下载时有一定区别。国外FPGA直接下载到FPGA里是bit文件,如果下载到FLASH里则是MCS等文件。安路FPGA不论是下载到FPGA还是FLASH,都可以选则bit文件,可以在软件中选择采用JTAG方式加载还是FLASH方式加载[3]。

该方式较适合在开发调试阶段使用,通过JTAG调试或下载程序到FLASH,也是最常用的方式。由于只存储单一程序的配置文件,一旦加载后只能实现一个特定功能,不同功能模块之间不能直接进行互换,也不方便升级。该模式一般应用于产品量小且产品只在特定室内运行,能快速拆卸机壳的环境,或者产品本身没有MCU。

2.1.2 从动级联加载

无论是在SS、MS还是MP、SP模式下,都有Flow Through和Bypass两种级联模式。级联工作模式由位流中的命令指定。这两个级联模式是可以无限级数的级联,非常适合大型系统采用。

在AL3A10BG256芯片的配置数据下载时,若采用Flow Through模式,第一块FPGA配置完成后,输出CSON启动第二款芯片进入配置。Bypass模式下,第一块芯片配置完成后,配置给其他FPGA的数据在每个CCLK上升时刻输出给DOUT引脚。级联配置芯片的DONE和INITN引脚通过上拉电阻线与连接在一起,只有2片都完成配置后,通过DONE芯片同时开始工作,如图2所示。

图2 级联

2.2 实现方式

随着通信设备的复杂化、多样化和国产化,同一套硬件设备可能应用于不同场合,这要求国产FPGA的内部逻辑要可随着应用场合可变化,使设备可以满足“一机多用”的应用需求。为了适应这种需求,本文介绍了一种“MCU+FLASH+JTAG”的硬件配置系统,可在不同条件下进行不同方式的加载[4]。

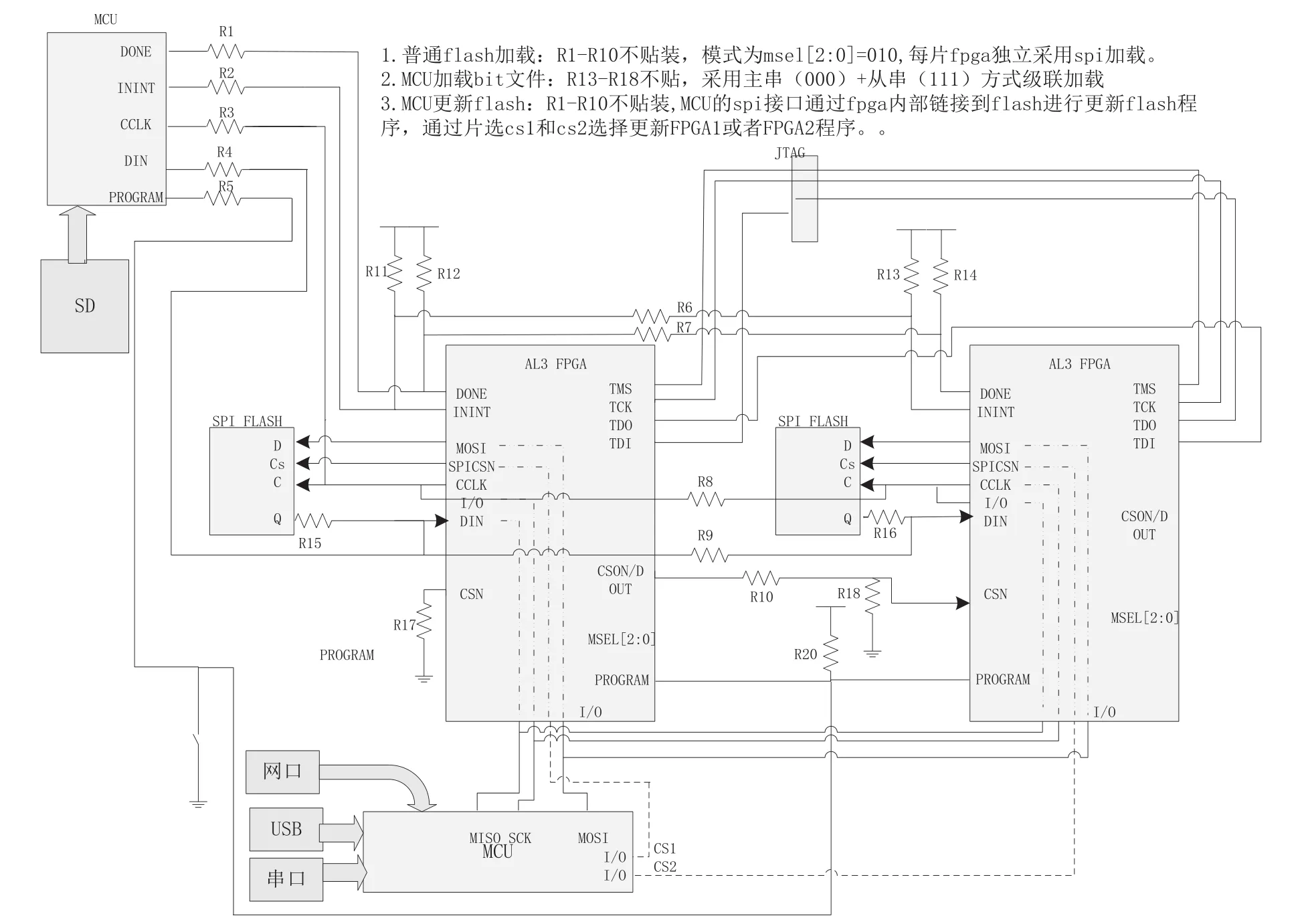

图3可以选择几种加载方式:一是JTAG加载或通过JTAG下载程序到FLASH;二是MCU直接加载,程序存在MCU中;三是通过FLASH加载,FLASH可以通过MCU的网口、USB、串口随时更新程序。第一种即JTAG级联,不作详细介绍,下面主要说明后两种加载方式。

2.2.1 MCU加载

第二种方式MCU加载bit文件,不需要FLASH。安路TD软件生成的bin文件存入MCU软件。MCU在启动后读取二进制文件,通过串行口写入FPGA中,硬件设计如图3所示的第2种方式。

FPGA软件可以设置为Flow Through级联模式,也可以是主动串接的Flow Through级联模式,通过MSEL选择。如果要采用Bypass级联,则把上一级的DOUT输入到下一级的DIN。需要在TD软件中设置以下两个选项开关,分别为设置级联模式为Bypass或Flow Through模式和设置多片同步启动模式。

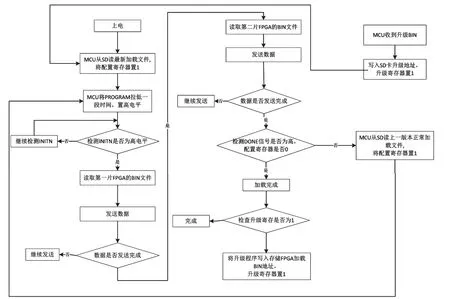

MCU将FPGA和MCU之间的配置寄存器设置为加载模式,将PROGRAM信号拉低并保持低电平时间大于1 μs,FPGA检测到PROGRAM为低且配置寄存器为0x1(加载模式),清除现有的程序进入加载状态,同时拉低INITN信号和DONE信号对CPU反馈。CPU检测INITN和DONE信号为低,待FPGA准备就绪后,将INITN信号拉高;CPU检测到INITN信号为高后,将输出时钟,并在时钟下降时开始发送数据。第一片FPGA芯片配置完成后,它会在每个CCLK上升时刻将新收到的数据通过DOUT引脚移位到下一片FPGA中。当所有FPGA加载完成后,最后一片FPGA将DONE信号拉高。如果加载不成功,DONE信号一直为低。FPGA在DONE信号拉高的同时,把配置寄存器设置为0x0(正常模式)。CPU在所有配置写入后延迟1 s,检测DONE信号并且读取配置寄存器,如果都正常,则表示加载成功。

图3 FPGA加载硬件

当需要升级FPGA程序时,通过网口或别的通信口通过MCU。MCU接收到远程传来的FPGA程序的BIN文件存放在外挂的非易失存储器中(如SD卡)的特定位置,同时开始进入加载模式。在FPGA加载成功后,将此次收到的BIN文件覆盖之前FPGA加载文件存放位置。如果没有加载成功,则把FPGA以前版本BIN重新加载,并且通知远方主机。

MCU软件流程序逻辑,如图4所示。

这种加载方式成本较低,升级性能好,可以在程序运行任何时间段更新程序并重新加载,缺点是CCLK也要由MCU GPIO口模拟。如果MCU GPIO口的速度较慢,加载文件较大,那么时间就较长。以兆易的MCU(GD32F450)+复旦微JFM7K325T为例,兆易自身启动大于90 s(与程序大小有关),JFM7K325T的BIN文件是11 176 kbyte。如果MCU GPIO的速度为800 kHz,FPGA加载时间为14 s,还需要MCU读取加载文件的时间,从加电到FPGA启动完成正常工作,需要将近120 s。对于时间比较敏感的产品来说,用户的体验会很差。在同等条件下,如果从FLASH启动,时钟为33 MHz,则加载只需要2.7 s。

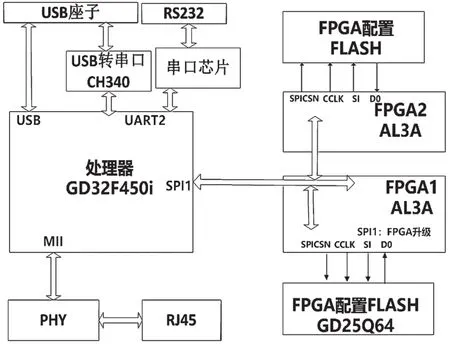

2.2.2 FLASH加载

第三种方式是通过FLASH加载bit文件,同时升级FLASH很方便,硬件如图3所示的第3点,产生bit文件或bin文件都可以(这与国外FPGA不同),要升级时可以通过MCU外接的RJ45或USB或RS232口连接。以北京兆易的MCU(GD32F450)+安路FPGA(AL3A10BG256)搭建一个升级平台,如图5所示。

图4 MCU软件流程序逻辑

图5 硬件平台

GD25Q64作为FPGA配置Flash,启动时连接FPGA的加载引脚。需要FPGA升级时,MCU和FPGA通信,通过SPI1接口访问配置Flash,实现FPGA升级功能。FLASH要成2个BANK,初始状态BANK1和BANK2的BIN文件为一样的。收到升级BIN后,BANK1为升级的BIN,BANK2为当前版本的BIN。在RJ45、USB、RS232三种接口中,RJ45距离最远,只要网络允许即可通信,但要在下载bin或bit文件时,加校验措施。USB和RS232都只能近距离升级,可以通过U盘升级连接USB座子。MCU收到USB提示后,读取USB内容后送入FLASH中。通过RS232可以实现RS23和计算机相连,然后MCU自带的使用“GigaDevice ISP Programmer”软件,选择相应的MCU,把BIN下载到MCU再进入FLASH。

MCU升级FLASH,需要制定一个升级寄存器,初始状态为0x0。如果有程序写入FLASH,则置0x3,在下次启动时从BANK1读取程序。如FPGA正常启动,则把升级寄存器置0x1。MCU检测到寄存器为0x1时,把BANK1的BIN文件写入BANK2,同时把升级寄存器置为0x00。如果CPU检测到FPGA重新加载了,升级寄存器为0x3,则把BANK2的数据覆盖BANK1,把寄存器置为0x00,且通过升级不成功。

第三种方式也是在产品阶段,通过FLASH启动。如果需要更新程序,MCU通过SPI更新FLASH的程序。这种配置方法的优点是外围电路简单、体积小,适合不需要频繁升级、对启动时间要求高的产品。第三种方式综合了前两种的优点,但比第二种方式增加了FLASH的成本。

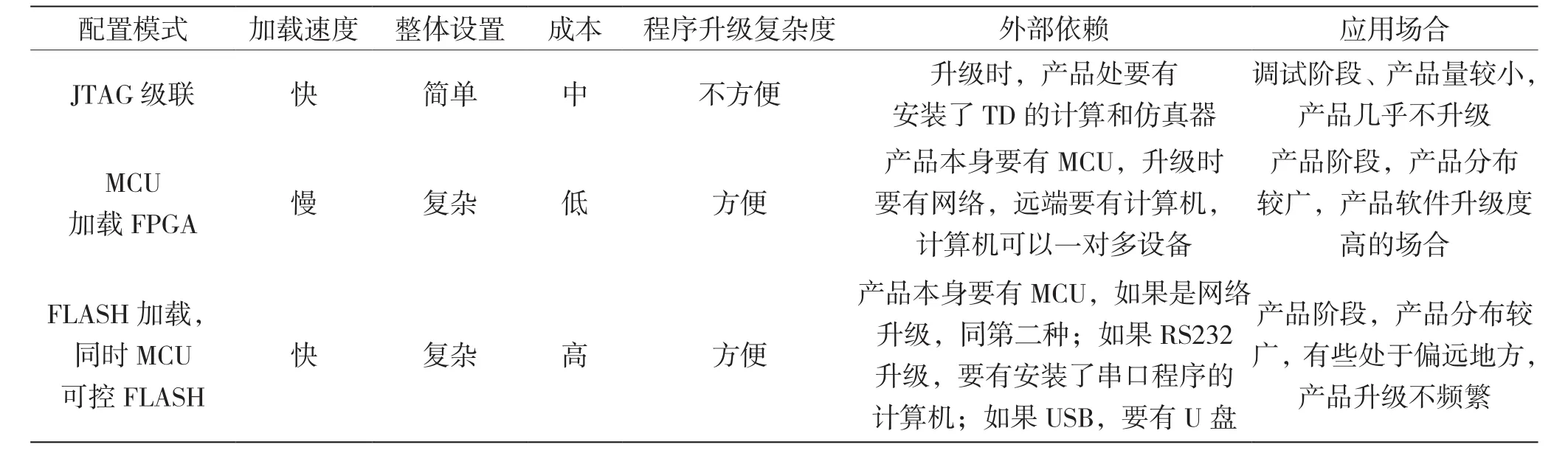

2.3 几种方式的对比

对于同样大小的配置文件,选择不同的配置模式,配置电路设计和配置时间会大不相同。常用配置模式比较如表1所示,选择配置模式时考虑的因素有整体设置、速度、成本、程序升级复杂性和应用场合等。

表1 配置模式比较

3 试验结果

为了对本文设计的配置系统功能和性能进行验证,根据图1搭建了系统验证平台。MCU采用兆 易 的MCU(GD32F450),FPGA采 用2片 安路公司的AL3A10BGA256,FLASH采用兆易公司的GD25Q64CSIG。选择文件为bit文件,采用Flow Through级联方式,JTAG下载时钟选择1M时钟。配置文件大小分别为285 kB和292 kB,MCU选用配置时钟为800 kHz,采用FLASH加载方式,用示波器实测加载时间为2 069 ms和2 105 ms(计算加载时间为2 280 ms和2 336 ms)。选择MCU的配置方式,配置时间为81 s(这里MCU启动到加载FPGA约为70 s),根据配置结束后的在线示波器采样的信号时序,FPGA的DONE引脚拉高,配置成功。

4 结 语

随着国产FPGA被越来越多的使用,设计中对多片FPGA加载方式也提出了更高要求。本文提出了典型国产FPGA加载的几种方案,设计者可以根据实际工程应用情况,灵活选择不同的加载方式,使得FPGA的配置加载更灵活可靠。本文提出的设计方案在实际使用时具有一定的参考意义,同时本方案经过实际工程应用检验,证明了安全性和可行性。