基于转换概率及RO结构的硬件木马检测

2020-02-19高良俊任传宝易茂祥黄正峰

陈 鑫,高良俊,任传宝,易茂祥,黄正峰

合肥工业大学 电子科学与应用物理学院,合肥230009

1 引言

随着集成电路(IC)的快速发展,IC的设计与制造分离已经成为一种趋势,导致IC安全面临更多威胁。这种分离给攻击者提供了机会在原始电路中植入具有恶意功能的冗余电路,称为硬件木马(HT),它可以篡改或者破坏载体电路的参数或正常功能,导致电路功能改变、敏感信息泄露或拒绝服务等[1-3]。IC芯片被广泛地应用于国防、军事、金融、交通等领域,一旦受到HT的攻击,就会造成极大的经济、安全等方面的损失。同时,“斯诺登棱镜门”“伊朗震网”等事件的发生也表明,HT可以作为武器来进行信息战、网络战,甚至可以摧毁军事装备及关键设备,给国家和人民的安全带来严重的威胁。因此,如何检测出IC中的HT就变得尤为重要。

硬件木马的检测方法主要可分为破坏性方法和非破坏性方法。破坏性方法主要指的是逆向工程验证,通过将待测芯片去封装,然后使用扫描电镜等设备对电路逐层进行拍照,再与原始版图作对比,从而判断芯片中有无硬件木马,该方法效果较好但成本非常高昂[4]。非破坏性方法包含逻辑测试和旁路分析。基于逻辑测试的检测技术主要是通过在电路的输入端施加各种测试向量,并观察电路的输出是否和预期的输出一致,从而判断电路内部是否被植入硬件木马,该方法能够有效地检测较小规模电路中的HT,对于大规模电路,由于测试向量的获取较为困难,故HT难于检测[5];旁路分析方法则是利用在电路中植入HT会对电路的旁路信号产生影响来观察比较待测电路与原始电路的旁路信息进行HT的检测,该方法能够检测出电路中规模较大的木马电路,对于较小的木马电路,由于工艺噪声的影响,HT对电路产生的影响易被覆盖,故不易检测HT[6]。

可信任设计方法则是通过在电路上增加额外的电路模块来辅助促进非破坏性硬件木马检测方法,减小测试向量的获取难度或者放大HT对电路参数的影响。文献[7]在电路中插入MUX来构建RO结构,通过构建多个RO来确保电路中每个门都在环内来检测HT,但在电路内部构建多个RO会改变电路的原始布局,对原始电路的布局布线质量会产生较大影响。文献[8-10]通过构建多个RO覆盖整个电路来检测电路中是否有HT的插入,基于HT在工作时会产生一个电压降的原理,从而将RO作为电源功率监测器应用于电路,由于构建RO的数量和级数较多,因此会造成较大的硬件开销。文献[11]选择转换概率比较低的电路节点作为目标节点来构建锁存结构,通过在版图级选择合适的参考路径来尽可能地降低工艺波动对锁存结构检测HT的影响。文献[12]提出基于与非门的RO比基于反相器的RO对HT的检测更敏感。文献[13]中提出通过调整RO级数的方法来提高对HT的检测敏感度。

因此,对于上述提到的基于可信任设计的硬件木马检测方法存在硬件开销较大及HT倾向于在电路转换概率较低的节点插入的问题,本文提出了在基于电路中转换概率较低的节点处构建RO的HT检测方法。该方法首先计算电路节点的转换概率并挑选出低于转换概率阈值的节点,然后在挑选出的节点处构建RO结构,进行木马的检测。实验结果表明,与文献[7,14]相比,本文提出的方法具有较小的硬件开销,并在可接受的面积和功耗开销下,可以检测到仅有一到两个门的小型木马电路。

由于小型木马电路规模较小而具有更低的硬件开销及对电路的旁路信号的影响较小而具有更高的隐蔽性,现有的硬件木马检测方法对小型木马的检测具有局限性[15-16]。而硬件木马对于电路的危害并不是随HT的规模线性增加的,因此,小型木马一旦被激活也会对电路产生较大的恶意后果[17-18]。本文提出的方法则弥补了现有方法对检测小型HT的不足。

2 基于RO的硬件木马检测

2.1 转换概率及HT植入节点分析

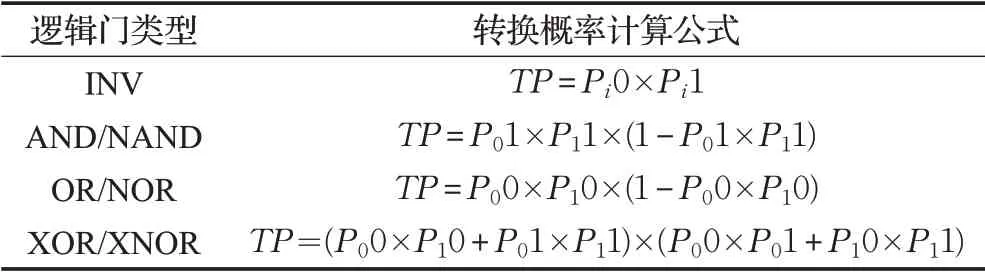

电路节点的转换概率指的是节点逻辑值的翻转概率。当假定电路中所有主输入端输入为“0”和“1”的概率都为0.5时,就能够根据逻辑门的类型及电路的拓扑结构来计算出各逻辑门的输出节点转换概率,即输出为“0”和“1”的概率的乘积。基础逻辑门的转换概率计算公式如表1所示。

表1 转换概率计算公式

表1中TP表示为该逻辑门输出节点的转换概率;Pi0表示第i个端口输入为0的概率,同理可得Pi1表示第i个端口输入为1的概率。

首先可以假设攻击者倾向于将HT插入不容易控制的电路节点中,即转换概率较低的节点。这一假设的基本原理为,高度可控的电路节点在制造测试阶段会有比较大的切换活动,所以连接到这些节点的HT引起的旁路效应容易被现有的检测方法检测到,故攻击者就会选择低可控节点作为HT的插入点[1,11]。

2.2 RO结构及延时计算公式

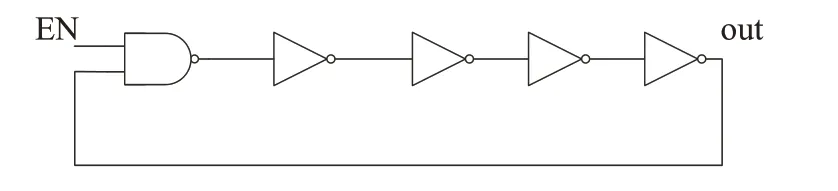

环形振荡器(RO)是一种采用奇数个具有反向功能的逻辑门组成的一种电路结构,且不需要时钟来控制其逻辑值的翻转。

如图1所示为一个5级的RO结构,由1个与非门和4个非门组成,其中与非门的一个输入端口当做使能端(EN)使用。当EN=0时,该环形振荡器未达到振荡条件,不能起振;当EN=1时,环形振荡器振荡。RO的振荡频率由组成该环的门的数量及单个门的延时决定。例如,当门的平均延时用td表示,RO的级数为n,则该RO的振荡周期为2×n×td,其振荡频率为:

图1 RO结构示例

2.3 检测方法流程

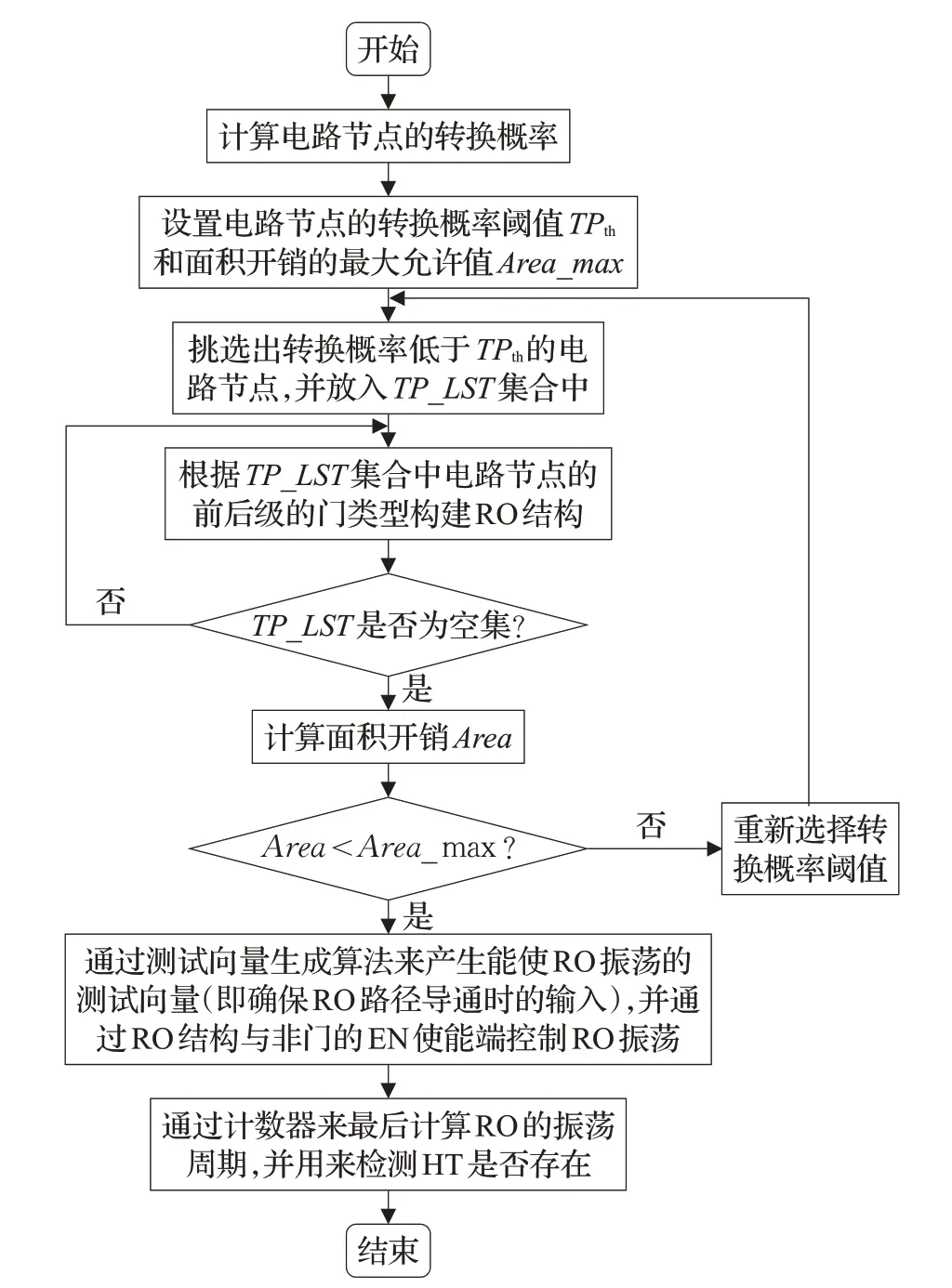

由前述可得,基于转换概率及RO结构的硬件木马检测流程如图2。该方法主要步骤如下:

步骤1根据电路节点转换概率计算公式及电路的拓扑结构来计算电路节点的转换概率。

步骤2设置合适的转换概率阈值,挑选出转换概率低于阈值的电路节点并放入TP_LST集合中。

步骤3根据TP_LST集合中节点在电路中的拓扑结构来构建RO结构。

步骤4计算电路的面积开销,根据设置的Area_max调整RO的数量。

步骤5根据算法产生的测试向量及RO的周期变化来检测是否有木马的存在。

图2基于RO的HT检测方法

综上可知,本文方法首先将低于转换概率阈值的电路节点挑选出来,然后分别配置RO结构,可以保证电路中若有HT的插入就会被检测出来;而判断构建的结构的面积开销及重新调整TPth,则可以保证在可接受的硬件开销下获得最大的HT检测范围;通过算法获得测试向量则可以保证在测试待测电路时构建的RO结构导通,进而检测HT的存在;对于电路中构建的多个RO结构,本文方法只需要1个计数器、1个解码器及1个多路选择器,确保了最小的硬件开销。

2.4 电路示例分析

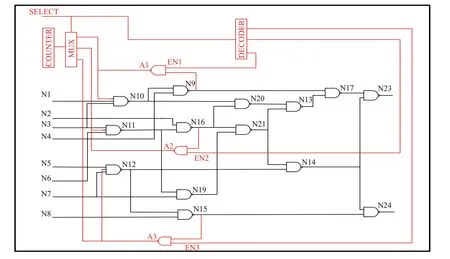

本文方法主要针对电路中转换概率较低的节点进行RO结构的构建,且适用于所有ISCAS’85基准电路。为了对该方法构建的RO结构有一个直观的了解,本文选择将ISCAS’85基准电路中结构相对简单、规模适中的C24电路作为示例电路来对所提方法进行分析讲解。如图3所示,黑色部分为原始电路。当假设电路的所有输入端口输入“0”和“1”的概率都为0.5时,则可以根据电路中门的类型及电路的拓扑结构来计算出电路中所有节点的转换概率,如表2,当转换概率阈值设置为0.2时,可以看到节点N10、N11、N12的转换概率低于阈值TPth。由于木马攻击者倾向于将HT插入不容易控制的电路节点中,即转换概率较低的节点,所以提出的方法对示例电路节点N10、N11、N12进行了RO的构建(图中红色部分)用来监视这些节点是否被插入硬件木马。

图3 示例电路c24

表2 c24电路节点的转换概率

从图中可以看出,本文的方法还需要1个计数器、1个多路选择器和1个解码器。解码器连接电路中RO的EN端口,用来控制选择RO的振荡;多路选择器则连接RO的输出端口,用来控制将当前振荡的RO的输出送到计数器;然后计数器计算一定时间范围内RO的振荡次数来计算该RO的振荡周期;图中2位输入信号SELECT(SELECT信号位数与电路构建的RO数量有关)是解码器和多路选择器的选择控制信号。从图中可以看出,若有HT在电路的低转换节点插入,则在检测阶段检测该节点处的RO的振荡周期时就会发现该RO结构的延时增加,从而导致HT被检测出来;若有具有反向功能的木马门插入,则当对该RO检测时会发现RO未进行振荡,也会检测出HT。综上所述,利用该结构可以有效地检测HT是否存在。

3 实验结果与分析

本实验是以ISCAS’85基准电路作为实验对象。首先使用C++编程语言在Visual Studio 2017实验平台上计算出基准电路的电路节点转换概率;然后使用Verilog编程语言在ISE14.7实验平台上搭建实验所需的RO结构;根据RO路径导通时部分节点逻辑值及电路的拓扑结构在VS2017上生成电路需要的测试向量;将构建好的RO结构下载到SPARTAN6 FPGA开发板进行实验并使用ISE中的Chipscope功能进行观察计数结果;最后使用Synopsys公司的DC(Design Compiler)综合工具在基于Nangate 45nm标准单元库下对所提方法的面积、功耗及延时信息做出分析。

3.1 测试向量生成

为实验的顺利进行,需要多组符合RO振荡条件的测试向量。在电路中,当MUX选择其中某个RO时,需要输入的测试向量能够满足该RO的振荡条件(即通过该RO路径上的逻辑门的其余输入端的逻辑值为非可控逻辑[11]),让其振荡从而求得延时信息。首先,输入电路的网表结构;然后把电路中逻辑门的类型和电路的拓扑结构转换成对应的合取范式(CNF),如表3;再根据RO路径部分电路节点的逻辑值增加额外的约束,使用SAT算法求解出一组测试向量;最后,重复上述步骤来得到不同的RO振荡所需的测试向量集。

表3 基础逻辑门CNF表达式

3.2 ISCAS’85部分电路的实验数据分析

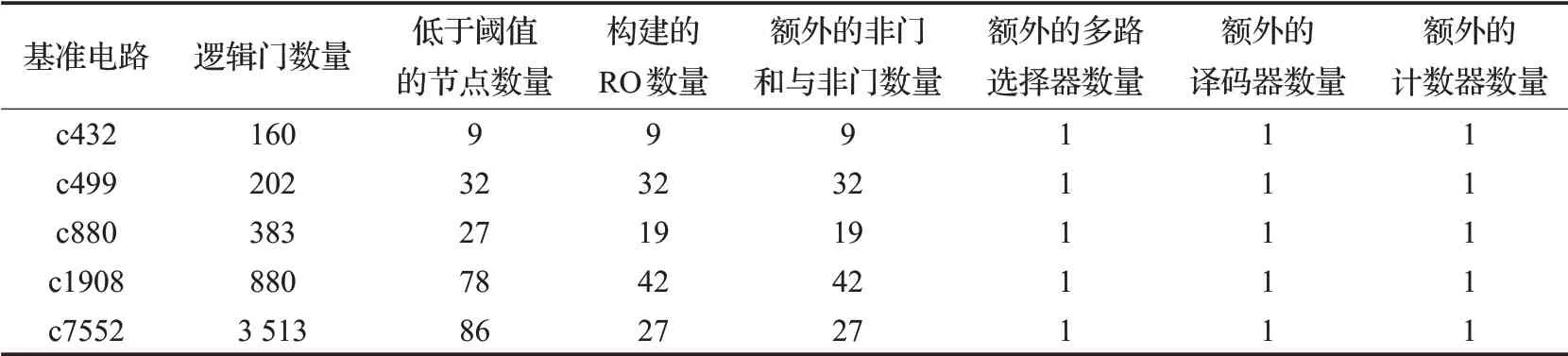

如表4所示第一列为ISCAS’85部分基准电路的名称,第二列为benchmark电路的门数量,第三列为各基准电路中转换概率低于设置阈值(TPth)的节点数量,第四到第八列分别表示需要构建的RO的数量,构建RO需要的额外的非门和与非门数量,以及计数器、解码器和多路选择器的数量。

从表中可知,随着电路逻辑门数量的增加,构建的RO数量并不是随之递增的,而是取决于电路中节点转换概率低于设定阈值的节点数量以及该节点前后级相邻的节点转换概率是否也是低于阈值的节点数量;而用来控制RO振荡及计算周期额外需要的计数器、解码器和多路选择器的数量都为1,因为每次只选择某一个RO进行振荡检测,所以本文提出的方法中只需要1个计数器,1个多路选择器和1个解码器,并且在不同的benchmark电路上所需要的计数器,多路选择器和解码器的大小不一样,这取决于电路构建的RO数量及振荡周期的预计值大小。

3.3 示例电路(C24)的振荡数据分析

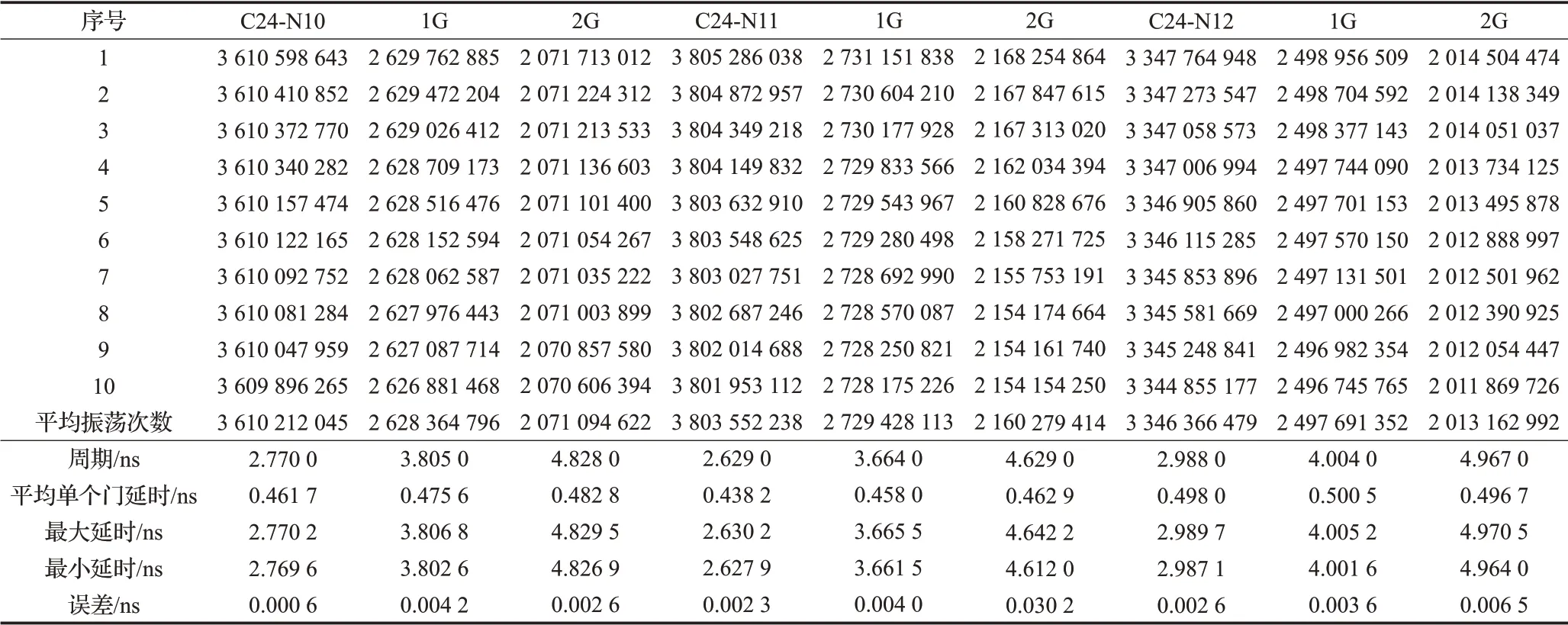

如表5所示为示例电路C24的实验数据,表中C24-N10、C24-N11、C24-N12分别表示电路C24的三个低于设定转换概率阈值的节点N10、N11、N12;而表中1G和2G则分别表示插入到电路节点的1个和2个与门木马[11,15]。为了减小测量误差,每个节点构成的RO(插入HT前后)分别进行了10次振荡来求取平均值;然后根据在设定时间内的振荡次数来计算RO的周期值;同时计算出RO中平均单个门延时,约为0.48 ns;表中也给出了在10次振荡测量中,最大振荡周期与最小振荡周期之间的误差值。由此可看出,若有HT插入,则引起的RO振荡周期的改变比测量时的误差大得多,故HT易于被检测。

表4 ISCAS’85部分电路(TP th=0.01)

表5 示例电路c24数据

3.4 功耗、面积、延时分析

由于c17、c24、c38基准电路相对较小,故在此未进行分析。而所提出的方法的硬件开销主要来源于环形振荡器,计数器,多路选择器和解码器。

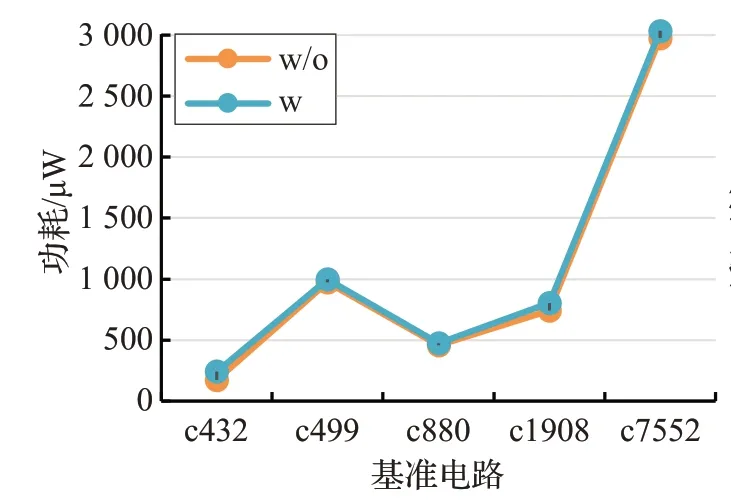

3.4.1功耗

图4给出了部分ISCAS’85电路在节点转换概率阈值TPth=0.01时构建RO结构前后的功耗分布,图中w/o表示基准电路原始的功耗,w表示在构建RO结构后的电路功耗。在不同的电路中,构建RO时尽量选择只添加一个与非门(当原路径中有偶数个具有反相功能的门时)或者一个非门加与非门(当原路径中有奇数个具有反相功能的门时)的组合,同时在电路低转换概率节点的地方观察该节点前后级是否还存在其他的低转换概率节点,若有,则选择将它们构建在一个RO内,以此来减小硬件开销。从图中可以看出,在不同的基准电路,电路的功耗在构建RO结构前后相差很小。

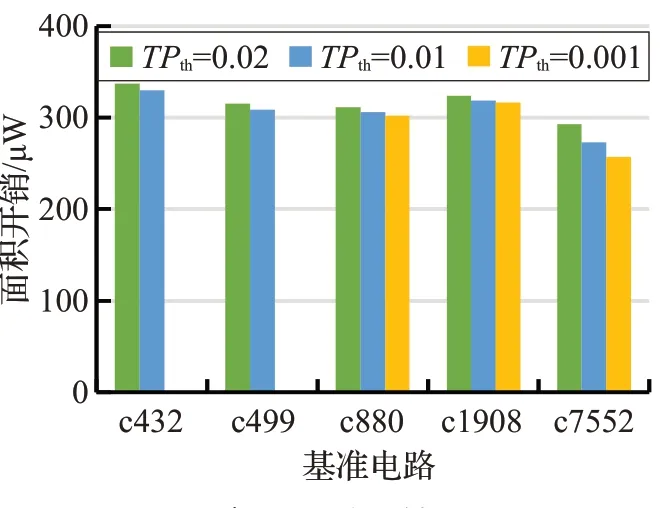

3.4.2 面积

如图5所示,给出了在部分基准电路中构建RO结构的面积开销直方图。从图中可以看到,在实验中共设置了三组不同的转换概率阈值,并在每一次的阈值设定后对基准电路做了相应的实验,得到其面积开销数据;由于在阈值TPth=0.001时,基准电路c432,c499节点转换概率没有低于阈值的节点,故其面积开销为零;还可以从图中得出,随着基准电路的规模增加以及电路转换概率阈值的不同,每个电路的面积开销变化都比较小。由此可知,在大型电路中,本文提出的HT检测方法所占用的面积资源百分比会更低。

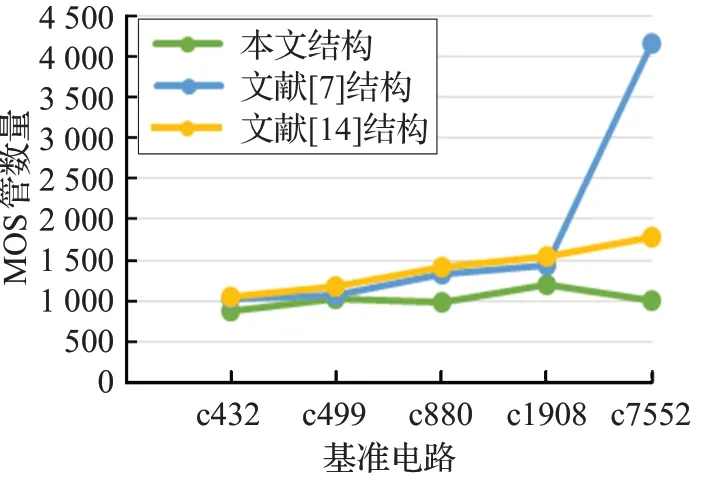

图6所示为本文提出的RO方法与文献[7]和文献[14]中提出方法的硬件开销的比较。纵坐标表示为三种方法结构所需的MOS管数量,横坐标表示不同的基准电路。从图中可以看出,随着基准电路规模的增加,本文方法的硬件开销变化波动较小,而文献[7]和文献[14]提出的方法的硬件开销呈现一个递增的趋势且均高于所提方法,因此可得,本文方法相对于文献[7]和文献[14]中提出的方法具有更低的硬件开销。

3.4.3 延时

图4 功耗开销

图5 面积开销

图6 三种结构MOS管数量对比

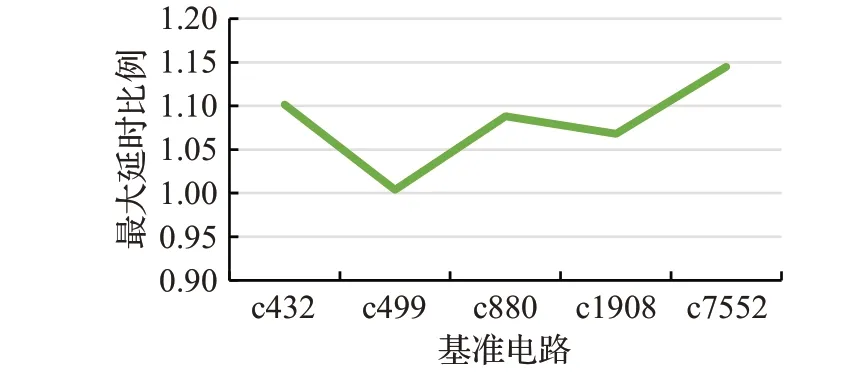

在原始电路中添加结构会对电路的原始性能造成影响,特别是关键路径的延时的增加[19]。所以在实验时要严格控制电路的时序,通过在部分ISCAS’85基准电路上进行实验(节点转换概率阈值设为TPth=0.01)得到如图7所示的延时数据。

图7 构建RO后电路最大延时与原电路最大延时比例

图7所示为电路在构建RO后与原电路的最大路径延时比,可以看出,通过选择将RO的位置控制在低转换概率节点路径附近来减少布线的延时,电路的最大路径延时比不超过1.15,较低程度地影响电路性能。

4 结论

在本文中,提出在电路的转换概率较低的节点处构建RO来检测该节点是否有HT的插入,并通过多路选择器,解码器和计数器来分别控制选择不同的RO并计算振荡周期。通过对电路门类型及拓扑结构的分析来计算电路节点的转换概率;通过测试向量生成算法得到实验所需的测试向量;通过分析选择适当的转换概率阈值来确定所需要构建的RO数量从而来减小所提方法的功耗和面积开销;同时,通过严格控制构建RO时的布局布线信息,将电路的最大路径延时控制在一定范围内。通过实验分析,电路在构建RO结构后,其功耗,面积及延时的增加都在可接受范围内,并且提出的方法能够检测小型HT,弥补了旁路分析法对检测小型HT的不足。接下来的研究工作会对不同RO级数进行实验,通过寻找合适的RO级数来提高对HT的检测精度;对HT攻击机制进行进一步的研究来寻找HT易于攻击的节点并构建RO结构来检测HT的插入。