1553B总线硬件架构分析与国产化研究

2020-02-02周鑫志李宁

周鑫志 李宁

(四川九洲空管科技有限责任公司 四川省绵阳市 621000)

上世纪70年代,美军为解决军用飞机载机各设备接口各异,互联难度大等带来的高额开发和维护成本等问题,提出了机载电子设备各系统信息交互的总线标准MIL-STD-1553B。1553B 总线作为应用于飞行器内部的多路复用的时分制指令/响应式数据总线,采用双冗余热备份通道架构,信息传输采用奇校验方法检查的错误,因此1553B 总线具有较高的可靠性且使用简单、灵活,已广泛应用于军民航的航空电子数据系统等领域。

1 1553B总线协议简介

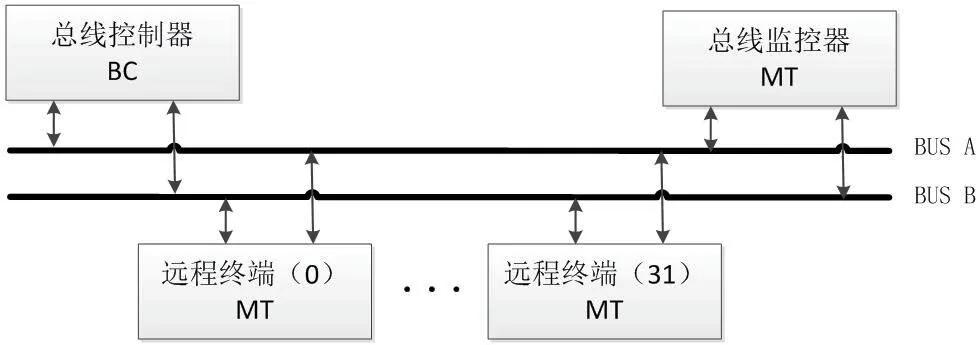

1553B 总线是一种集中管理的串行总线。在其总线系统上,可以看到多个子系统经总线传输媒介相互交联,完成功能和信息共享的同时,又保持各自的独立性。1553B 总线架构如下:

(1)一个总线控制器(BC),执行发起总线数据的传输任务,主要保证完成总线调度和管理;

(2)远程终端(RT),总线最多可连接32 个独立子系统,完成各自的通信与数据交互;

(3)总线监视器(MT),主要用于监视总线的运行状态,记录通信过程。

1553B 总线的数据传输方式为半双工通信,通信速率为1 Mbps,每个字字长20 位,数据有效位为16 位,最长消息长度为32 个字。总线传输的数据编码格式为曼彻斯特II 型双相码,采用差分传输的方式,传输采用的介质为屏蔽双绞线。

如图1所示,1553B 总线网络拓采用双冗余的扑结构:总线A、总线B 双总线之间互为冗余热备份。当总线A 工作异常时,总线B 将接替总线A 工作,大大增强了总线通信系统的可靠性。

2 1553B总线硬件架构

为实现1553B 总线数据传输,总线接口电路的协议芯片是核心,它可完成1553B 数据转换、曼彻斯特Ⅱ型码的编译码功能、同步头的产生与检测、各种消息格式和方式代码的总线传输等。其中,比较典型的代表有BU-61864,HI-2130 等。

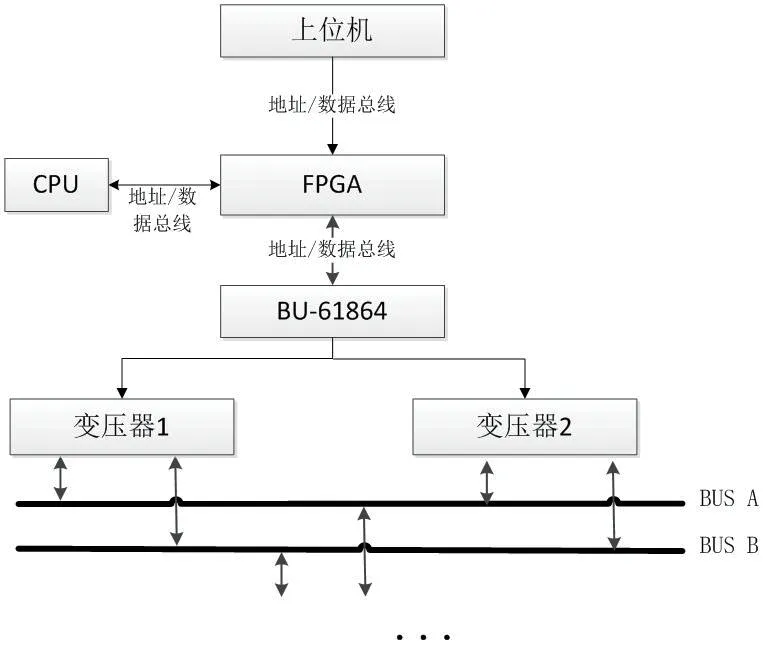

DDC 公司作为1553B 标准的主要制定者和研制者,他们开发的1553B 协议芯片以ACE 系列最为著名[1]。其中,比较经典就是其推出的MiniACE 芯BU-61864 协议芯片,该芯片内部具有64K字节的双口RAM,采用20Mhz 的时钟频率。基于BU-61864 的总线通信接口电路的硬件架构框图如图2所示。

该方案硬件主要包括:处理器(CPU)、1553B协议处理器,时钟、收发器与隔离变压器等。各功能电路如下:

(1)主机接口:主机接口包括CPLD 和对外接口部分。主要完成主机接口的总线从逻辑,协议芯片存储空间的访问,以及协议芯片的硬件配置等。

(2)协议处理电路:对外发送数据时,CPU 解析上位机的命令信息并将其存入协议芯片的存储器,协议芯片完成总线收发数据的1553B 格式编码,送入收发器送出;接收命令时,协议芯片将曼彻斯特码解析后存入内部存储器,CPU 处理后由CPLD 转发至上位机。

图1:1553B 总线网络拓扑结构

图2:基于BU-61864 的1553B 硬件架构

图3:基于SM61864G3 的1553B 硬件架构

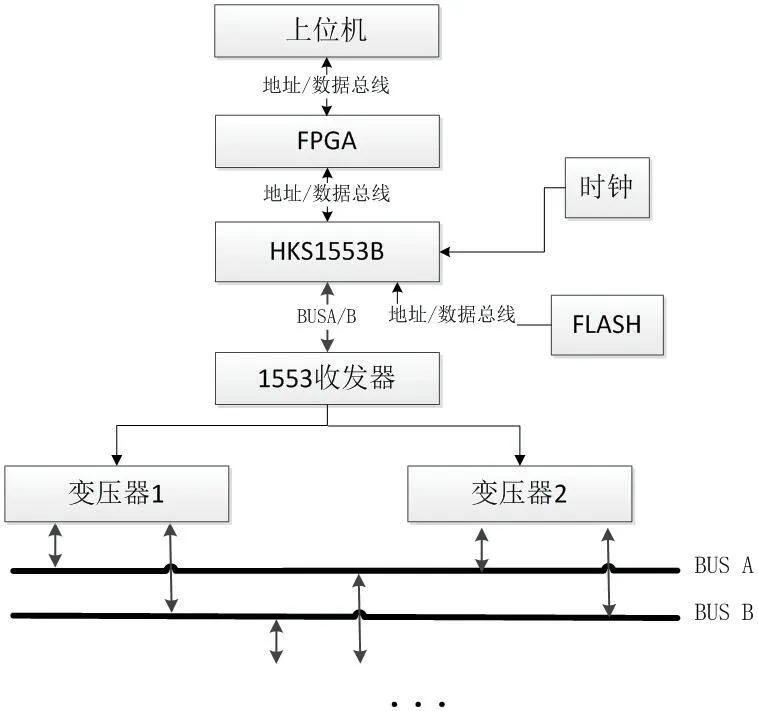

图4:基于HKS1553B 的1553B 硬件架构

HI-2130 是美国HOLT 公司的一款经典1553B 协议芯片。HOLT 是一家主要为航空工业提供器件的供应商,具备超过20年的经验为世界范围内的商业和军用客户提供显示驱动芯片及数据总线芯片。基于HI-2130 的1553B 总线数据接口硬件架构与61864 基本一致,但其内部集成了收发器和变压器,且尺寸更小(15*15mm),因此芯片该可以有效节省设备空间。

3 1553B总线国产化研究

3.1 国产化发展现状

近年来,1553B 系列芯片的价格逐年上升。且华为、中兴的芯片断供案,愈发表明,国产核心芯片的自主可控的重要性。为适应我国自主开发的大环境,我国于1997年11月发布了GJB289A-97[2],该标准充分解读国际标准的基础上,增加了适应我国相应标准的内容。

目前,我国在1553B 国产化发展和思路主要分为两类:一是利用FPGA 内置的1553 IP 核开发相关功能板卡以替代国外协议芯片,这种方法在空间、成本等各方面有一定的优势,但可靠性有待进一步提高,主要由FPGA 自身的质量等级、电磁兼容性能等各因素决定;第二,是开发可功能替代甚至原位替代国外相似型号的国产协议芯片,近年来,已经有相应的国产化1553B 协议芯片用于我国航空、航天、航海及其它使用GJB289A 总线传输数据的通信网络领域。国产化芯片在各平台得到充分的使用和验证,在一定程度上改变了1553B 芯片及相关产品高度依赖国外厂家产品的局面,打破了国外对这一技术的垄断,并得到了用户的认可。下面,重点针对国产协议芯片SM61864G3 和HKS1553,简单介绍其功能应用和硬件架构设计。

3.2 国产协议芯片

SM61864G3 是国产的符合1553B 总线标准的接口控制器,可以实现BC、RT 和MT 功能。它兼容Mini-ACE (Plus)和ACE 产品,而且增加了很多信息处理功能,为数据传输提供了更加灵活,更加丰富的处理能力,已经在产品中得到验证。

SM61864G3 内部各功能模块如下:总线控制协议模块;半双工的编解码器;标准4K*16bit RAM;可扩展的64K*17bit RAM;存储器管理电路和中断逻辑电路;灵活的与主处理器和存储器相连的接口逻辑;双1553B 收发器。可以实现BC、RT 和MT 功能。

基于SM61864G3 的1553B 硬件架构设计如图3所示。FPGA主要完成接口电路的逻辑控制功能,主要包括:

(1)与CPU 的接口控制逻辑;

(2)与SM61864G3 的接口控制逻辑;

(3)与上位机的总线通信接口控制逻辑;

(4)内部实时时钟控制逻辑。

CPU 主要完成配置和通信等功能。包括:

(1)初始化协议芯片,根据上位机的命令,完成BC、RT、RT/MT 的工作方式选择配置,内部区域配置,寄存器配置等;

(2)协议芯片自测试,将自检结果周期上报,并根据自检结果自动送出中断请求;

(3)协议芯片的启动,CPU 解析上位机送来的通信需求,写入/读取存储器相应数据。配置协议芯片的开始寄存器,启动协议控制模块控制芯片内部的读写模块、编解码模块和收发器的工作,完成1553B 的总线通信功能。

3.3 国产化片上系统

目前,飞行器内部的设备集成度日益增高,各种外围接口如422,429,AFDX 等标准接口的种类也越来越多。1553B 总线多年的发展中也成为航电系统的标配接口,因此,随着载机设备的功能性能要求的提升,对1553B 总线的功耗、体积、重量和国产化的要求也越来越高[4]。

为满足日益增长的需求,一种多功能高速1553B 总线接口SoC 片上系统协议芯片应运而生,型号HKS1553。它内部集成了CPU、GJB289A 协议处理器、DPRAM、中断控制器、定时器、UART 等功能模块,同时兼容了计时器、看门狗和实时时钟等功能模块,可实现GJB289A 总线系统中BC/RT 功能。因此,使用该芯片可降低了软硬件设计的复杂性,减少CPU 等功能电路所占PCB的面积,有效节省了装备的使用空间。

基于HKS1553 的硬件架构如图4所示。各功能电路主要完成以下任务:

(1)FPGA:完成接口电路的逻辑传输管控功能,主要包括与上位机的总线通信接口控制逻辑;与HKS1553B 的控制逻辑;

(2)HKS1553B:协议芯片通过总线收发器连接到GJB289A总线,芯片内部集成的处理器负责完成片上设备的管理,HKS1553B 芯片的主机接口与FPGA 连接,FPGA 通过访问HKS1553B 芯片内部的双端口存储器,实现对GJB289A 总线数据的处理;

(3)内部1553B 协议收发器:发送器部分将上位机送来的互补格式的曼彻斯特编码信号转换为适于驱动隔离变压器的双相位曼彻斯特编码的1553 B 信号,每个发送器有一个单独的禁止端口;接收器则将总线上的双相位曼彻斯特编码数据接收并转换为互补格式的曼彻斯特编码信号传输至上位机作进一步处理分析;

(4)时钟电路:系统时钟SYSCLK 采用33MHz 时钟输入,GJB289A 协议处理器时钟1553BCLK 采用12MHz 的时钟输入,串口时钟UARTCLK 采用3.6864MHz 时钟输入,时钟输出信号LCLK 是将APB 总线时钟引到片外,为外部总线接口提供参考时钟。

4 发展趋势

目前,1553B 至今已发展30 余年,得到广泛的应用。但随着机载设备的信息交互数据量吞吐率不断提高,各子系统的复杂度不断提高,1553B 总线已经不能满足特定的要求,例如:带宽不足,1553B 总线的传输速率只有1Mbps;时间调度颗粒较大,总线周期在5ms 以上,一般为10ms 或者25ms;节点数量太少,最多只能挂31 个节点[4]。

因此,在1553B 的发展中,接口子系统电路的重量上要求尽可能轻、体积上尽可能小、消息处理速度尽可能快、存储器容量尽可能大、软硬件编程尽可能方便等方向发展[5]。

未来1553B 充分发挥其稳定可靠的优势的同时,将朝着高速化(2/4/10Mbps)甚至光纤传输方向发展。此外,芯片及应用的小型化、低功耗,电磁兼容,抗恶劣环境、抗辐射的能力也是未来重点研究方向。