低频信号失真度测量系统设计

2020-01-14

(南开大学 电子信息与光学工程学院,天津 300071)

总谐波失真(THD)是信号的重要参数之一,它表征了信号偏离正弦波的程度,是衡量运算放大器、功率放大器等器件及函数信号发生器等仪器的重要指标,另外THD的测量在电力电子、电声学等诸多领域有着广泛的应用与重要意义。THD主要有基波抑制、频谱分析及正弦波形拟合等测量方法[1-5]。通过阅读文献及对比现有的失真度测量仪,发现利用现有的方法或仪器测量THD被测信号频率的下限基本都在1 Hz以上,为了解决低频信号THD测量的问题,本文在频谱分析法基础上利用可编程逻辑器件对比较器输出的方波信号进行自适应消抖处理,成功地实现了频率下限为0.1 Hz被测信号THD的测量。本文研究的技术方案可为测量低频信号THD的应用场景提供有益的参考。

1 系统整体方案设计

系统的硬件结构主要包括嵌入式处理器、可编程逻辑器件、模数转换器(ADC)、电压比较器及方波电平变换电路等部分。其中比较器负责产生与被测信号频率、相位一致的方波,该方波经过电平变换电路输出给可编程逻辑器件。可编程逻辑器件的主要作用是运行自适应消抖算法以消除输入方波在上升沿及下降沿处产生的抖动,消抖后的方波信号输出给嵌入式处理器。嵌入式处理器利用32位定时计数器捕获该输入信号的频率和起始过零点(上升沿),然后控制ADC从起始过零点开始以上述频率的整数倍来采样原始的被测信号,这样就实现了对被测信号的整周期同步采样,有效地避免了频谱泄漏和栅栏效应[6]。对采样得到的数据进行快速傅里叶变换(FFT)并结合THD的定义就可以获得被测信号的THD值[7-9],同时利用液晶屏(LCD)显示被测信号整周期的波形及频率、峰峰值等信息。综上,该系统的结构框图如图1所示。

图1 低频信号失真度测量系统结构框图Fig.1 Structure block diagram of low frequency signal distortion measurement system

2 系统设计实现

下文从软、硬件两方面对该低频信号失真度测量系统进行介绍。

2.1 系统硬件设计

2.1.1 嵌入式处理器及可编程逻辑器件

本文采用意法半导体(ST)公司的基于ARM Cortex-M7 32位RISC内核的STM32F767IGT6嵌入式处理器作为主控芯片,该嵌入式处理器工作频率可达216 MHz,内置1 MB闪存,512 KB SRAM及32位定时计数器等多种外设。消抖部分的协处理器采用Altera公司的Cyclone IV系列可编程逻辑器件EP4CE10E22C8N,其内嵌10320个Logic elements(LEs),414 Kbits RAM,并内置硬件乘法器、模拟锁相环等丰富的外设资源。

2.1.2 模数转换器

被测信号必须经过ADC转换成数字量后才能利用嵌入式处理器做进一步的处理,如果选用STM32F767IGT6内部的ADC,则被测信号的电压范围必须为正值且不能超过处理器的电源电压,对于交流被测信号则必须利用运算放大器搭建电平抬升电路才能满足ADC输入电压范围的要求,而电平抬升电路的引入将一定程度上增大被测信号的噪声并影响其THD值,综合上述原因,模数转换器考虑采用亚德诺半导体(ADI)公司的AD7606,该芯片为8通道同步ADC,16位采样精度,最高采样率200 kS/s,单电源5 V供电兼容±5 V或±10 V模拟量输入,具有1 MΩ模拟输入阻抗的输入缓冲器,及二阶抗混叠模拟滤波器[10],可以很好地满足该失真度测量系统的要求。

2.1.3 比较器及电平变换电路

利用比较器芯片LM393对被测信号进行过零比较,比较器输出的方波信号再经过电平变换电路输出给可编程逻辑器件,该部分的电路原理如图2所示。

图2 比较器及电平变换电路原理图Fig.2 Schematic diagram of comparator and level translationcircuit

图2中Vin为被测信号,Vsq为比较器的输出,二极管D1的作用是将Vsq整形成电压全正的方波,电阻R3、R4对整形后的方波分压得到Vout_FPGA,输出给可编程逻辑器件。LM393是双路比较器,未用到的那路不能悬空否则会影响Vsq的波形,将未用到的比较器正输入端接地,负输入端通过电阻R2接地,这样就不会对Vsq产生影响。

2.2 系统软件设计

2.2.1 自适应消抖算法

由于比较器自身的特性,当被测信号频率较低或幅值较小时,输出信号在过零点极容易会发生抖动,如果不做消抖处理则很难实现后续的整周期同步采样等操作。本文利用可编程逻辑器件对比较器输出的方波进行自适应消抖,消抖算法的结构图如图3所示。

图3 自适应消抖算法结构图Fig.3 Structural diagram of adaptive elimination buffeting algorithm

图3的Vout_FPGA为图2中经过电平变换后的比较器输出信号,Vout_MCU为消抖后的信号并最终输出给嵌入式处理器。Ejitter_clk及Ejitter为利用硬件描述语言编写的功能模块,其中Ejitter模块的功能是对方波进行消抖,下面对消抖算法进行简介。连续10个时钟周期采样xin管脚的输入信号,当10个时钟上升沿采样得到的信号都为高电平时dout输出高电平,如果采样都为低电平则dout输出低电平,其他情况下维持dout先前的输出状态不变,这样就实现了对输入信号的消抖处理。D触发器对dout进行等占空比二分频得到TS_OUT,则TS_OUT的高电平时长即为dout的周期,也相当于Vout_FPGA的周期。TS_OUT连接到Ejitter_clk模块的xin管脚,该模块的功能是产生周期为xin输入信号高电平时长万分之一的时钟信号 clk_out,即 clk_out的频率为Vout_FPGA频率的一万倍,系统复位时clk_out的频率为10 MHz,clk_out连接到Ejitter模块的时钟输入端,这样Ejitter消抖模块的时钟频率自适应输入信号的频率,即实现了对该输入信号的自适应消抖处理。

2.2.2 整周期同步采样及FFT处理

可编程逻辑器件将消抖后的方波信号输出给STM32F767IGT6处理器的PH10管脚,该管脚为32位定时计数器5的通道1,具有输入捕获功能,在程序中开启上升沿输入捕获中断,两个连续上升沿的时间间隔即为被测信号的周期,对周期取倒数即得到其频率值。为了实现对被测信号的整周期同步采样,从理论上说需控制模数转换器从被测信号的起始过零点开始以上述频率的整数倍进行采样,但考虑到AD7606的抗混叠滤波器具有15 μs的群延时,程序中设置AD7606采样时刻整体延后相同的时间。实测AD7606采样一次耗时约7.5 μs,为了在被测信号的一个周期内尽可能多的采样,同时采样点数要满足基2FFT运算的要求,设定ADC采样的频率与被测信号频率间的关系见式(1):

式中:fADC为ADC的采样频率;fVin为被测信号频率。

STM32F767IGT6处理器厂家提供的DSP库具有基2的浮点FFT函数,式(1)中N即为FFT的点数。ADC采样得到的数据传递给FFT的相关函数,即可得到基波及各次谐波对应的幅值。由于FFT结果的对称性,最高可以计算得到N/2次谐波的幅值。式(2)为THD的计算公式:

3 系统测试

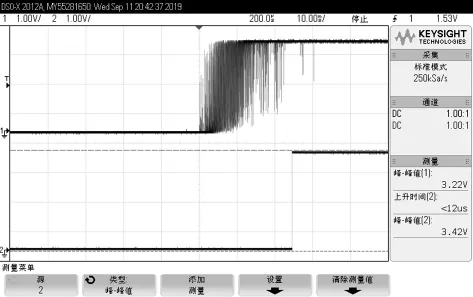

利用直流稳压电源(型号:SS2323)、函数信号发生器 (型号:TFG6080)及示波器 (型号:DSO-X 2012A)搭建低频信号失真度测量系统的测试环境。由于AD7606芯片输入电压的限制,本文研究的失真度测量系统被测信号的电压范围不超过±5 V,另外由于采用过零比较器,所以被测信号应为交流信号。利用直流稳压电源输出±10 V为系统供电,函数信号发生器产生频率0.1 Hz峰峰值4 V的正弦波,利用示波器测量消抖前后的波形以验证自适应消抖算法的效果,测量结果见图4。

图4 消抖效果示波器测量结果图Fig.4 Oscillogram of measurement results of elimination buffeting

图4中通道1波形(上半部分)为经过电平变换后的比较器输出信号波形,通道2波形(下半部分)为可编程逻辑器件对该信号进行消抖处理后输出给嵌入式处理器的波形。可以明显看出抖动已经完全消除。

设置函数信号发生器产生频率500 Hz峰峰值4 V的正弦波,按照式(1)在一个周期内ADC等间距采样128个点,每次ADC开始采集时配置STM32F767IGT6处理器的PB0输出高电平,采集结束后配置PB0输出低电平。利用示波器观察正弦波及PB0的波形,测量结果见图5。

图5 整周期同步采样示波器测量结果图Fig.5 Oscillogram of measurement results of integer-period synchronous sampling

从图5可以看出实现了对被测正弦波的整周期同步采样。

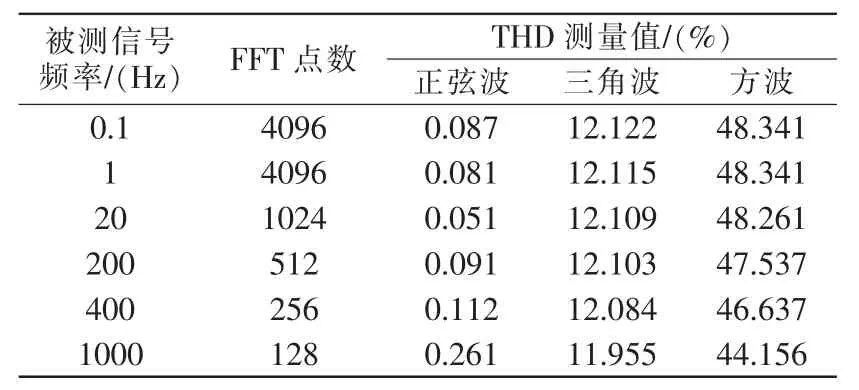

利用函数信号发生器产生峰峰值4 V不同频率的正弦波、三角波及方波作为被测信号,THD的实测结果见表1,系统实物及LCD的显示界面见图6。

表1 THD测量结果数据表Tab.1 Data of THD measurement results

图6 低频信号失真度测量系统实物图Fig.6 Actual picture of low frequency signal distortion measurement system

根据式(2)可推导出方波和三角波THD的理论计算值分别为48.343%及12.115%,对比表1的测量数据,当被测信号频率在0.1~1000 Hz之间时本文设计的失真度测量系统对正弦波、三角波及方波THD的测量值与理论值的偏差在分别在0.261%、0.16%及4.187%以内。

4 结语

本文设计的低频信号失真度测量系统,可以实现电压范围不超过±5 V,频率0.1~1000 Hz交流信号失真度的测量,对于电压范围超过±5 V或非交流的被测信号需经过电压衰减电路及电容隔直处理再输入到该系统进行测量。此外本文研究的基于可编程逻辑器件的自适应消抖技术方案可为测量低频信号失真度的研究提供有益的参考。