基于Zynq的固态存储系统设计和实现

2020-01-07蔡德林

吴 祥,彭 卫,蔡德林

基于Zynq的固态存储系统设计和实现

吴 祥1,彭 卫2,蔡德林2

(1.安徽大学 电子信息工程学院,安徽 合肥 230601;2.中国电子集团第38研究所 微波研发中心,安徽 合肥 230031)

针对传统的存储介质对高速数据流进行存储时可能出现的低速率以及高延时的情况,通过设计固态存储系统以提高系统的存储性能。基于Xilinx推出的Zynq平台进行设计,Zynq作为行业内第一个成功地将ARM和FPGA整合到一起的可扩展处理平台,在FPGA部分设计PCIe接口和数据接口分别驱动固态硬盘和存储数据流,在ARM部分移植嵌入式Linux操作系统并实现NVMe(非易失性存储器)驱动和数据接口驱动。项目设计使用了PCIe接口方案的IP核简化了对PCIe链路部分的设计,通过移植嵌入式Linux使系统支持文件系统以及多线程的能力。最后通过验证系统可将PL端的高速数据流存入SSD(固态硬盘)中,相比于现有关于存储系统的设计,缩短了系统的开发周期,提高了系统的速度和实用性。

PCIe;固态存储;Petalinux;状态机;Zynq;DMA控制器

在对高速大量的数据流进行存储时,使用传统的机械硬盘或片上存储芯片存储的速度和存储的容量都很难达到要求,然而SSD(固态硬盘)有着存储速度快、体积小、使用寿命长、无机械噪音和抗干扰能力强等特点更加适合在工业环境中应用,并且随着NAND Flash成本的进一步降低,SSD这一新型存储器经历了爆发式发展和应用[1]。通过研究发现现有的关于固态存储系统的设计主要是对PCIe接口部分的设计以及在standalone(裸板)下实现NVMe[2]驱动,然而对于PCIe接口和驱动部分的开发有着难度大和时间周期长等问题,在系统结构方面也没有预留对外的数据接口无法对外部的数据流进行存储,不能体现出系统的完整性缺乏灵活性。本文通过使用Xilinx的PCIe接口方案[3]来简化PCIe接口的设计,并增加数据接口来接收外部数据;在软件方面,通过实现NVMe驱动和数据接口部分驱动实现对高速数据流的存储。

1 关键技术介绍

1.1 Zyng平台介绍

Zynq平台是由Xilinx公司推出的行业内第一个可扩展处理平台,可为高端嵌入式应用提供性能处理与计算[4]。Zynq在结构上可分为2个部分:PS(processing system)和PL(programmable logic),其PS部分和传统的ARM处理器内部结构一致,PL部分则是传统的FPGA。但相较于传统的ARM平台外设固定,Zynq最大的特点就是可以利用PL部分来自定义外设,这也是Zynq灵活性的一个具体表现。

本文系统设计基于Zynq 7035芯片,其PL部分集成了4路的高速GTX收发器,支持PCIe Gen2×4,可以配置为PCIe Root Complex(根复合体)模式来驱动PCIe接口的固态盘,PS部分的双核ARM处理器架构为V7,主频可根据需要进行配置最高可达800 MHz。

1.2 PCIe总线介绍

PCIe总线使用串行差分信号来传输数据具有传输带宽高、可靠性高、抗干扰强以及成本低等特点。在PCIe链路的拓扑结构中可将PCIe设备分为Root Complex(根复合体)、Switch(交换开关)和Endpoint(端点设备)3个部分。

PCIe总线和绝大多数总线一样也采用分层来实现,PCIe总线协议定义了三层从上到下依次为:事物层(transaction layer)、数据链路层(data link layer)、物理层(physical layer)[5],每一层的功能不同但下层总是为上层提供服务。其中事物层的主要职责是创建或解析TLP(transaction layer packet)和流量控制等,数据链路层主要是负责创建或解析DLLP(data link layer packet)、检错和纠错等,物理层则是处理所有的Packet数据的物理传输。

2 PL部分逻辑设计

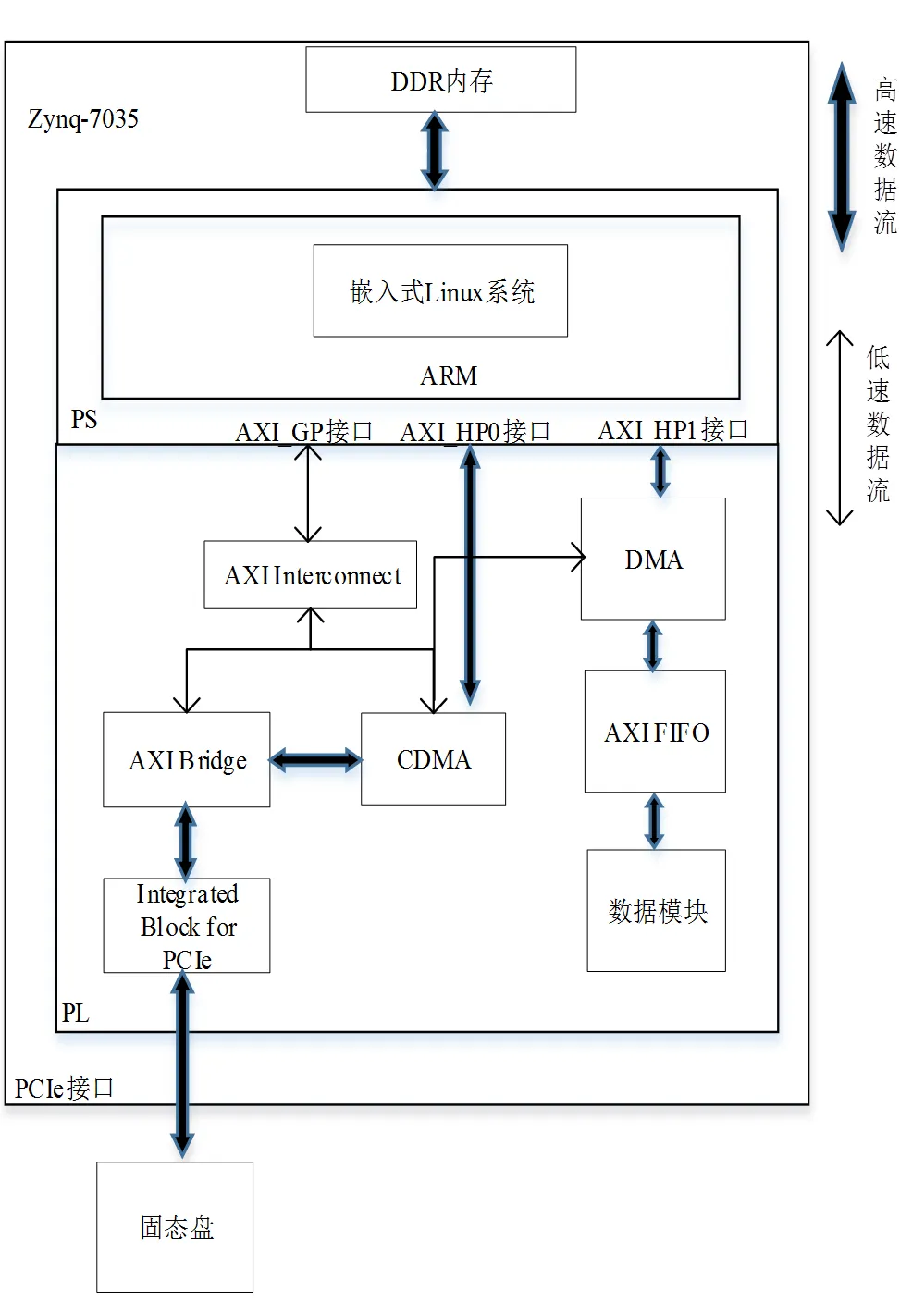

图1所示为系统结构框图,对于固态存储系统的设计可分为2个部分来进行,在PL部分使用FPGA资源设计PCIe接口子系统和外部数据接口模块,当逻辑部分设计完成后再在PS部分完成NVMe驱动和数据接口驱动设计。系统的PL和PS通过2个高速接口AXI_HP0和AXI_HP1进行高速的数据传输,PS通过AXI_GP接口来对PL中各模块控制。

图1 固态存储系统结构图

2.1 PCIe接口子系统设计

2.1.1 AXI PCIe桥接器

在Xilinx提供的多个PCIe接口解决方案中都包含一个名为Integrated Block For PCIe的IP核,Integrated Block For PCIe是Zynq芯片集成的PCIe硬核用来实现PCIe协议的物理层和数据链路层,其传输数据流是Unmapped(无地址映射)型的TLP数据包,在与PS进行数据传输时要使用AXI Bridge来进行地址映射以及对TLP数据包的封装和解析,在Vivado中Integrated Block For PCIe和AXI Bridge组合为AXI Memory Mapped to PCIe,也称为AXI PCIe桥接器[6]。使用AXI PCIe桥接器可简化PL部分对PCIe接口子系统的设计,AXI PCIe桥接器既可配置为EP模式也可配置为RC模式,本文Zynq作为主机来驱动SSD,因此AXI PCIe桥接器应被配置为RC模式。

AXI PCIe桥接器结构如图2所示,主要由3个部分组成:Integrated Block For PCIe、Master AXI Bridge和Slave AXI Bridge分别连接AXI地址域空间和PCIe地址域空间,2个不同的地址空间之间进行访问需要地址转换的过程,当EP设备对主机发起访问时,发出的TLP请求首先被PCIe硬核接收,然后由Master Bridge(主桥)进行地址翻译将PCIe域地址转换成相应的AXI域地址,使得EP访问到正确的AXI域中地址。当RC对EP的BAR(基地址寄存器)空间发起访问时,首先RC访问的AXI域地址请求被SlaveBridge(从桥)接收,并且将其翻译成PCIe域地址,然后由PCIe硬核将访问请求封装成TLP数据包,最后发送给PCIe设备完成对EP设备的BAR空间访问。PCIe硬核实现了PCIe总线协议的物理层,主要完成创建和解析TLP数据包。

图2 AXI PCIe桥接器

2.1.2 DMA控制器

DMA(直接内存访问)控制器的使用可大大减少处理器的工作负荷,处理器只需要只需指定源地址、目的地址、传输字节数和传输方向,DMA控制器就可以在无CPU控制下进行数据搬移,在搬移结束后通过中断告知CPU结果即可,这很大程度地提高了系统的性能[7]。

AXI PCIe桥接器完成了数据从Unmapped到Mapped的映射,CDMA(AXI Central DMA Controller,AXI中枢控制器)在PL部分使用FPGA逻辑资源实现,可将PL端Mapped型数据流传输到PS端内存中[8],因此选择CDMA来完成高性能的数据搬移是最合适的方法。

2.2 数据接口设计

设计数据接口来接收外界数据流,针对不同的系统应用,对数据模块进行设计就可实现对不同接口(光口和以太网等)的数据流存储,这更能体现系统的灵活性。

2.2.1 数据模块

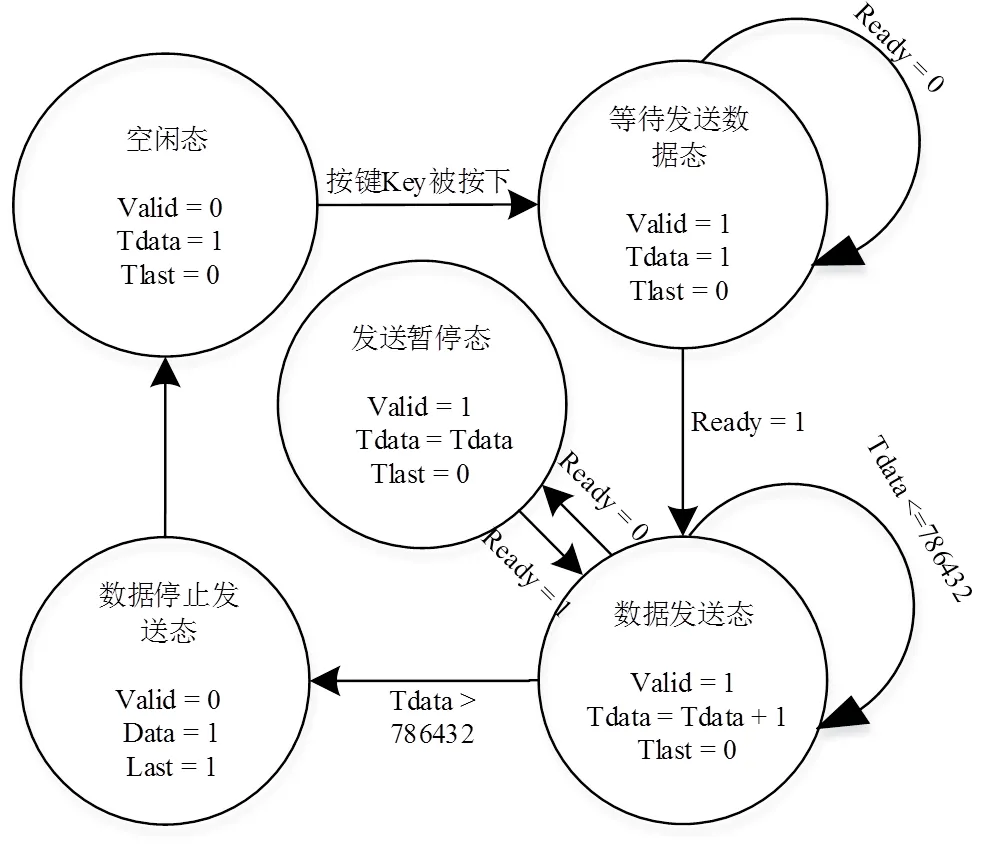

在PL端设计一个数据模块,该模块是自定义的具有AXI4接口的IP核,在该模块中使用一个状态机来控制其产生连续的32位数据,状态机的状态转换如图3所示。其中Ready、Valid、Tdata和Tlast均是AXI4接口中的信号,Ready为高电平表示从设备准备就绪可以接受数据,Valid为高电平表示此时发送的数据为有效数据,当所发送的数据是最后一个数据的时候Tlast会从低电平变成高电平,Tdata为发送的数据且只有当Ready和Valid均为高电平时数据才会被接收方成功接收。

图3 数据模块状态转换图

在状态机中,空闲态时valid为低电平此时输出数据为无效数据;当按键被按下后跳转到等待发送数据态,如果此时接收方Ready为高电平,表示准备好接受数据,此时跳转到数据发送态;在数据发送态下,数据模块从Tdata为1开始连续向从机发送数据,当Tdata的值大于786432时,立即跳转到停止发送态,并且将Tlast拉高表示786432为最后一个数据;最后状态机重新回到空闲态,等待下一次按键被按下。

2.2.2 接口模块

数据接口模块通过DMA控制器来将PL端的高速数据流搬移到PS端的内存中,FIFO模块是一种先进先出的数据缓存器,在对不同速率的模块之间的数据进行传输时可以作为缓冲器进行调节[9]。数据模块产生的数据首先放入FIFO中缓存,当主机发起数据搬移命令后,FIFO中的数据则通过DMA搬移到PS端内存中。

3 PCIe设备枚举

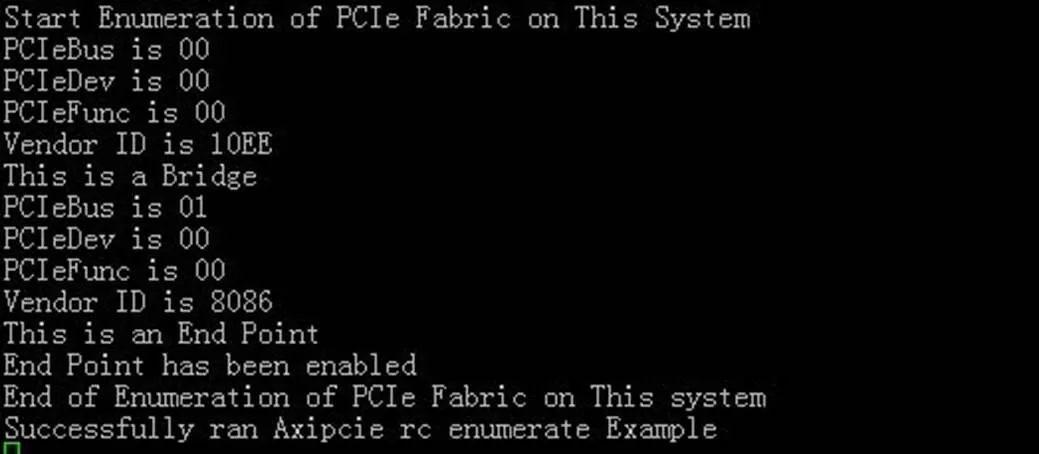

PCIe接口子系统的作为系统中重要的一部分,PCIe链路能否成功建立可以通过PCIe设备枚举来得到验证,在裸板环境下使用Xilinx官方提供的SDK来对AXI PCIe桥接器进行配置,并对系统中EP设备进行枚举。为使系统的性能更稳定,PCIe链路的参考时钟由可编程时钟芯片SI5338P提供,PS端通过IIC接口对时钟芯片进行配置,使其输出稳定的100 MHz PCIe链路参考时钟。

首先通过Export Hardware功能将Vivado设计中的HDF(硬件描述文件)和编译完成的bitstream文件导入到SDK中,再基于此设计裸板下的PCIe设备枚举程序,裸板下对PCIe设备的枚举流程如图5所示。在枚举函数中首先需定义AXI PCIe桥接器的实例,其类型为:

图4 PCIe设备枚举流程

其中Config是类型为Struct XAxiPcie_Config的变量,其包含了IP的硬件配置信息:

当时钟芯片配置成功后,SI5338P将为PCIe链路提供稳定的100 MHz的差分时钟,XAxiPcie_LookupConfig()函数通过唯一的设备ID来查找IP核配置信息,根据得到的配置信息来对Struct XAxiPcie变量进行初始化,初始化成功后依据成员变量IncludeRootComplex的值判断IP是否配置为RC模式,若未被配置为RC模式则无法进行设备的枚举串口打印枚举失败并且退出函数,若IP被配置为RC模式,则通过XAxiPcie_IsLinkUp()函数来读取BAR中链路状态寄存器判断链路是否建立成功,链路建立成功后读取IP核寄存器的值,包括总线号、设备号、功能号和端口号,并对IP中可写寄存器写入数据再读回比较读写数值是否一致,最后枚举系统中的PCIe设备并通过串口将这些设备的信息打印出来并退出枚举函数。

4 驱动开发

在Linux系统中,驱动程序作为低层硬件和上层应用的桥梁,硬件设备在Linux下能够正常工作必须要开发对应的驱动程序,Zynq平台采用的是FPGA+ARM的架构,在FPGA部分设计的IP核也必须要有驱动程序的支持才可以在Linux中正常运行[10]。NVMe官方已开放Linux环境下的NVMe驱动源码,因此本节主要描述对数据接口部分驱动的开发。为使DMA控制器可正常工作需要设计嵌入式Linux系统下的DMA驱动程序,在早期发布的Linux内核中,各种嵌入式处理器对DMA驱动框架是不统一的,都有自己的DMA编程接口,这给开发者带来了很多不便,为了改变这一局面,Linux内核开发了一个统一的DMA子系统—dmaengine[11](DMA引擎)。

在DMA驱动中定义一个struct dma_channel结构体类型,此结构体包含了一个DMA通道所涉及到的所有数据struct dma_channel结构体类型定义如下:

DMA驱动的工作流程可以分为以下几个步骤:

(1)使用API函数dma_request_slave_channel()向DMA引擎申请一个DMA接收通道,指定DMA传输的方向并在内存中为其分配一块适用于DMA操作的内存。

(2)使用API函数device_prep_slave_sg()创建传输描述符chan_desc,对其进行初始化并指定回调函数,当DMA操作完成后回调函数将被调用。

(3)使用API函数dmaengine_submit()将初始化过的传输描述符chan_desc提交给DMA引擎。

(4)使用API函数dma_async_issue_pending()开始对指定的DMA通道传输。

(5)等待DMA传输完成。

除此之外,驱动中还包括驱动的初始化函数,驱动卸载函数。

5 嵌入式Linux系统以及驱动的移植

5.1 Petalinux的安装

Petalinux由Xilinx公司开发,在Linux环境下对嵌入式Linux操作系统进行开发的工具,不仅提供了Linux内核(Kernel)、启动文件(U-boot)、文件系统以及嵌入式应用程序的配置和编译方法,还整合了同步Vivado FPGA硬件设计工程到Petalinux中的方法,方便了软硬件协同设计[12]。

在安装Petalinux之前需要安装依赖库:lia32-libs、ncurses-dev、gcc-multilib、libssl-dev等,安装成功后使用以下命令配置Petalinux环境变量脚本,每一次使用Petalinux工具之前都要进行环境变量的配置。

#source

5.2 Linux内核及文件系统的配置

在Petalinux导入HDF文件并解析HDF文件后,使用内核配置命令来对Linux内核进行配置,命令如下:

#petalinux-config -c kernel

在内核配置的图形界面下使能PCI总线支持,Xilinx AXI PCIe host bridge,NVMe块设备等驱动的支持,完成配置保存并退出。

使用文件系统配置命令来配置Linux文件系统,在文件系统配置界面下需要配置SSD的功能单元,命令如下:

#petalinux-config -c rootfs

5.3 DMA驱动模块的添加

DMA驱动是用户开发的驱动模块,需要使用Petalinux来添加到Linux系统中,大体流程如下[13]。

(1)使用Petalinux创建一个驱动模块,此驱动模块为自定义驱动基本框架。

(2)将开发的DMA驱动dma_driver.c等头文件复制到驱动模块文件夹下。

(3)编写驱动的Makefile文件。

(4)向设备树文件中添加DMA驱动的设备树节点。

(5)用Petalinux编译生成内核镜像文件image.ub(内核镜像文件)和BOOT.BIN(启动镜像文件)。

在使用DMA设备之前要手动加载驱动进入内核,加载进内核后在/dev目录下可以看到一个名为dma_rx的字符设备。通过编写上层应用,在应用程序中对dma_rx字符设备进行操作就可通过DMA将PL端数据搬移到PS端内存中。

6 系统测试

本文的实验使用Zynq 7035开发板搭建项目平台,主机端配置为win 7操作系统,8 GB内存,I5-5400 CPU,在主机端虚拟机中安装Ubantu14.01操作系统来使用Pealinux来对嵌入式Linux操作系统的裁剪和移植,将使用Petalinux工具生成的启动文件U-BOOT和镜像文件IMAGE拷贝到SD卡的FAT分区中,将文件系统拷贝到SD卡的EXT-4分区中,最后接通电源开机运行。

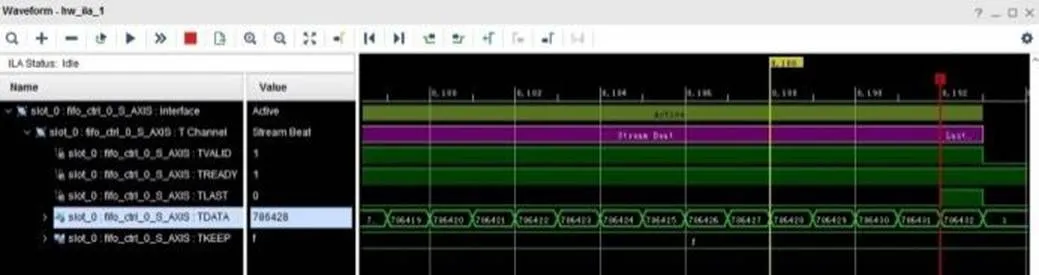

ILA(逻辑分析仪)是Vivado中对系统进行调试时重要的工具,对数据模块插入Vivado逻辑分析IP核来观察模块发送的数据,图5为按键按下后抓取的数据波形,模块从1开始连续地发送数据接收方Ready信号一直为高,数据可正常被接收。

图5 开始写数据到FIFO

图6为数据模块连续发送数据直到786432,Tlast信号为高表示为最后一个数据,Ready信号为高接收方可正确接受。数据模块可以连续向fifo发送从1到786 432,总共786 432个数据,每个数据位宽为32位,数据量为3 MB。

图6 停止写数据到FIFO

图7为PCIe枚举函数通过串口打印出系统中的PCIe设备,包括AXI PCIe Bridge IP核以及PCIe接口的固态盘,并分别读取它们的总线号、设备号、功能号和厂家ID。

图7 PCIe枚举

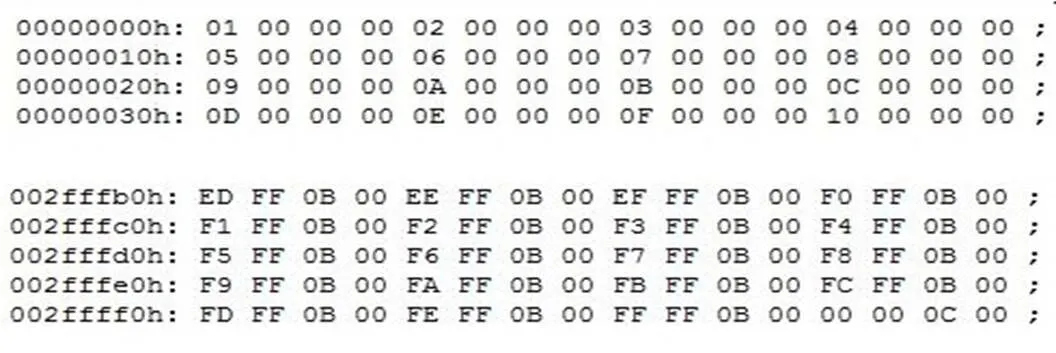

在Ubuntu系统中,使用交叉编译工具GCC将应用程序编译成在嵌入式Linux环境中运行的二进制文件,并通过Tftp服务器将文件下载到开发版文件系统中。程序运行结果如图8所示,PL端的数据存入了固态盘的data文件中,将其通过Tftp上传到主机端,图9为data文件中头和尾部分数据,接收到的32位数据均以二进制格式存入文件中,文件大小为3 MB其中连续保存了786 432个数。

图8 程序运行结果

图9 Data文件中二进制数据

7 结论

本文基于Zynq平台,通过软硬件协同设计的方法在PL端分别完成了PCIe接口和数据接口的设计,在PS端使用Petalinux移植嵌入式Linux操作系统并完成Linux下的驱动开发,最终实现了对外部数据的存储。不同于采用裸板开发主要针对PCIe接口子系统部分的设计,本文设计的存储系统预留对外的高速数据接口更能体现系统的整体性,在不同的应用中只需对数据模块进行重新设计就可以完成系统的整体设计,在Linux的支持下此系统也可进行更为复杂的任务处理具有更高的灵活性。

[1]陈思扬. 基于FPGA的NVMe接口设计[D]. 西安: 西安电子科技大学, 2015.

[2] NVM Express Inc. NVM Express[EB/OL]. http://www. nvmexpress.org/about/,2018.

[3] Xilinx Inc.pcie central dma subsystem[EB/OL]. http:// china.xilinx.com/support/documentation/application_notes/xapp1171-pcie-central-dma-subsystem.pdf,2019.

[4] 陆启帅, 陆彦婷, 王地. Xilinx Zynq SoC与嵌入式Linux设计实战指南[M]. 北京: 清华大学出版社, 2014.

[5]Revision 3.0,PCI Express Base Specification[S].

[6]LiuYu-feng,Xu De-gang, Cai Hai-ming, et al.System Architecture Design of PCIe Root Complex Based on SOPC[C]. Proccedings of the 36th China Control Conference,USA:IEEE Conference Publi -cation,2017.

[7] 郭志红,石春, 吴刚.嵌入式以太网通信系统设计与实现[J].小型微型计算机系统,2015, 36(4):754-758.

[8] Cao Ying-jie, Zhu Yong-xin, Wang Xu,et al. An FPGA based PCI-E Root Complex Architecture for Standalone SOPCs[C]. International Sympo-sium On Field- programmable Custom Computing Machines, USA: IEEE Conference Publication,2013.

[9] 黄万伟,董永洁.Xilinx FPGA应用进阶[M].北京:电子工业出版社,2014.

[10] Wang Long-fei, Zhao Xiao-qing, et al. Zynq-based Solid-State Drive Prototyping Platform for Emerging Non-Volatile Memories[C].2016 13th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT)Proceeding,USA:IEEE Conference Publication, 2016.

[11] 姜先刚,刘洪涛.嵌入式Linux驱动开发教程[M]. 北京: 电子工业出版社,2017.

[12] 李朗,张索非,杨浩.基于Zynq-7000的视频处理系统框架设计[J].计算机技术与发展,2017, 27(5):192-195.

[13] Xilinx Inc.Xilinx Petalinux SDK user guide:getting started guide[EB/OL].https://www.xilinx.com/support/documentation/sw_manuals/xilinx2018_2/ug1144-petalinux-tools-reference-guide.pdf, 2018.

Design and Implementation of Solid-state Storage System Based on Zynq

WU Xiang1,PENG Wei2, CAI De-lin2

(1.School of Electronics and Information Engineering, Anhui University, Hefei 230601, China;2.Microwave Research and Development Center, The 38th Institute of China Electronic Corporation, Hefei 230031, China)

In the data acquisition and processing system, storing a large number of high-speed data streams is one of the key points of system design. Traditional HDD has some deficiencies, such as low storage rate, high storage delay, poor system stability and so on. Compared with the insufficiency of HDD, NVMe SSD has the characteristics of high storage rate, low storage delay and small size. This paper is based on the Zynq platform of Xilinx. Zynq is the first extensible processing platform to successfully integrate ARM and FPGA. In the PL of Zynq, the PCIe interface and data interface are designed, which are respectively used to connect the PCIe interface SSD and external data stream. The embedded Linux operating system is transplanted in the PS of the Zynq and the NVMe drive and data interface drive are realized. By using the IP core of PCIe interface, the design of the PCIe link part is simplified. By transplanting embedded Linux, file system and multi-threading capability are supported in the system. Finally through verification, the high-speed data stream can be stored in SSD. Compared with the existing design of storage system, the system designed in this paper has the characteristics of high storage performance, strong practicability and high flexibility.

PCIe; solid-state storage; Petalinux; state machine; Zynq; DMA controller

TP368

A

1674-3261(2020)01-0012-06

2019-10-17

安徽省高校自然科学研究重大项目(KJ2017ZD03);安徽省教育厅自然科学重点项目(KJ2018A0019)

吴 祥(1994-),男,安徽铜陵人,硕士生。

蔡德林(1965-),男,安徽安庆人,研究员。

优先出版地址:http://kns.cnki.net/kcms/detail/21.1567.T.20191227.1019.010.html

责任编校:孙 林