国外空间红外遥感器模拟前端处理技术发展研究

2020-01-03王华李强薄姝闫静纯蔡帅富帅赵宇昂贺强民

王华 李强 薄姝 闫静纯 蔡帅 富帅 赵宇昂 贺强民

国外空间红外遥感器模拟前端处理技术发展研究

王华1李强1薄姝1闫静纯1蔡帅1富帅1赵宇昂2贺强民1

(1 北京空间机电研究所,北京 100094)(2 内蒙古电力科学院,呼和浩特 010020)

文章对空间红外遥感器模拟前端处理技术进行调研研究,首先对美国、欧洲的红外遥感器模拟前端处理技术的电路结构、性能指标和关键电路设计方法进行了介绍;然后对红外遥感器模拟前端处理技术的低噪声、低功耗、深低温工作的技术特点进行了分析,最后给出中国空间红外遥感器模拟前端处理技术发展建议。期望通过对美国、欧洲红外遥感器模拟前端处理技术研究和分析,为中国空间红外遥感器模拟前端处理技术发展提供参考。

红外遥感 模拟前端 低噪声 空间相机

0 引言

空间红外遥感器是空间光学遥感器的一种,主要是通过红外探测器收集地物辐射的人眼看不到的红外辐射波,经过光电转换变成人眼所能看到的图像,具有全天候、隐蔽性好、可以穿透云烟等优点,被广泛应用于军事、气象、环境监测、海洋观测等领域。与可见光遥感器的探测器相比,空间红外遥感器的探测器具有深低温(几十开)工作、输出阻抗大、对偏置驱动电压精度和噪声要求高的特点[1-4]。

空间红外遥感器模拟前端处理技术主要是对红外探测器输出的模拟信号进行阻抗变换、调理放大(包括可编程增益放大、模拟处理链路失调校正)和模数转换,并为红外探测器提供高精度低噪声偏置驱动,该处理技术位于红外遥感器信号流的最前端,其性能直接决定遥感器的成像性能,是空间红外遥感器视频电子学的核心处理技术。本文旨在通过对美国、欧洲空间红外遥感器模拟前端处理技术现状进行调研研究,为我国空间红外遥感器模拟前端处理技术发展提供参考。

目前国际上关于空间红外遥感器模拟前端处理技术有两种设计思路:一种是标准集成芯片通过印制电路板(Printed Circuit Board,PCB)互联设计实现对红外探测器的驱动和处理;另一种是将模拟前端处理部分进行集成,设计高集成度可深低温工作的单片式模拟前端专用芯片(Application Specific Integrated Circuit,ASIC)。前者为传统的板级设计方法,该方法标准集成芯片需工作在军温(–55℃~125℃)或常温条件下,因此只能在低温杜瓦外实现与探测器的互联,处理电路传输干扰大、体积大、功耗大;后者可将单片式模拟前端ASIC放置在低温杜瓦中,直接与探测器连接,缩短探测器高阻模拟信号的传输距离,就近对探测器模拟信号进行模拟调理和模数转换,同时对量化后的图像数据进行数据预处理,具有噪声低、集成度高、体积小、易于模块化设计的优点[5-6]。

1 美国红外遥感器模拟前端处理技术

目前美国红外遥感器模拟前端处理电路均采用单片式模拟前端ASIC实现,其2002年即开始了对单片红外焦平面模拟前端ASIC的研究[5],典型的模拟前端ASIC有SIDECAR(System for Image Digitization Enhancement Control and Retrieval)和ACADIA(ASIC for Control and Digitization of Imagers for Astronomy)。

1.1 SIDECAR

SIDECAR是美国Teledyne公司研制的一款单片式红外焦平面模拟前端ASIC[3],已应用于美国“哈勃”望远镜(Hubble Space Telescope,HST)、“詹姆斯韦伯”望远镜(James Webb Space Telescope,JWST)、Landsat-8卫星和欧洲的“欧几里得”(Euclid)空间望远镜等多个项目中[7-9],并已成为Teledyne公司的货架产品。

(1)组成结构

SIDECAR组成结构如图1所示,其集成了36通道16bit 模数转化器ADC(可配置为12bit ADC);具有36通道可编程增益放大器PGA,放大倍数–3~27dB可调;可通过20通道10bit数模转化器DAC产生20路可调偏置,偏置类型即可为电压型也可为电流型;通过微处理器产生32通道输入输出数字时序信号,所有时序信号的周期和相位可编程;另外还包括16bit可编程微控制器和256 kbit程序存储器、992 kbit数据存储器,具有加、减、乘、除、平均等阵列数据运算功能[6,10]。

图1 SIDECAR的组成结构

(2)关键电路设计

1)PGA和ADC。可编程增益放大主要是对探测器输出的模拟信号进行缓冲、放大和滤波,SIDECAR的PGA采用了电容反馈的电路结构。

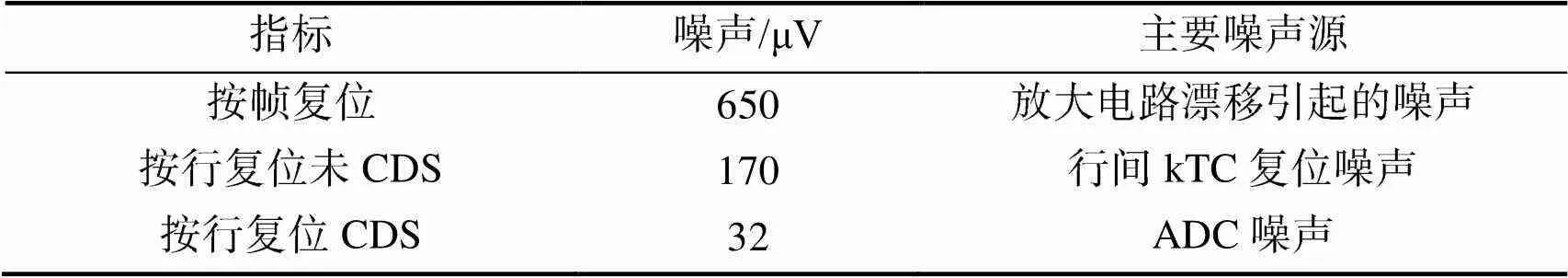

电容反馈放大电路通过切换不同的反馈电容,实现不同的放大倍数。电容反馈与电阻反馈相比具有低噪声、低功耗和高线性度的优点,但由于电容的漏电流随时间和温度漂移会引起信号漂移,因此需要周期性为电容网络复位以抑制电容漏电流漂移对放大电路的影响,SIDECAR内部设计相关双采样(Correlated Double Sampling,CDS)电路抑制电容复位产生的kTC复位噪声[11-12]。文献[12]给出了SIDECAR在100kHz采样速率,增益放大4倍时,按秒级帧复位、按毫秒级行复位未CDS和按行复位CDS的噪声测试数据如表1所示。

表1 SIDECARPGA测试结果

Tab.1 Test results of SIDECAR preamplifier

由表1的测试结果可以看出,以秒为单位按帧复位,复位周期长,电容反馈放大电路的电路漂移非常大;缩短复位周期,以毫秒级行周期按行对电容网络复位可以消除放大电路漂移,但会引入kTC复位噪声;缩短复位周期并通过CDS技术则可以很好地抑制电路漂移和kTC噪声,将电路噪声由650μV降低到32μV。

2)偏置驱动。SIDECAR可调偏置驱动部分采用10bit DAC+电压缓冲器+驱动调整电路的架构实现,如图2所示。通过微控制器配置控制寄存器,控制寄存器设置设定输出的电压值或电流值,电压可调范围为0~3.3V,电流可调范围为0.1μA~25mA[6]。

图2 SIDECAR可调偏置结构

SIDECAR偏置电压驱动输出端设计由RC构成的低通滤波电路,对产生的偏置电压进行滤波。在输出端未加低通滤波和加低通滤波(RC参数360ms,帧周期2s)时,图像噪点明显,经过低通滤波后图像干净均匀。将输出图像总噪声扣除PGA电路噪声和ADC噪声,得到未加低通滤波时偏置驱动噪声(RMS)为36μV,加低通滤波时(RC参数360ms)噪声(RMS)仅为4μV[12]。

1.2 ACADIA

宽视场红外巡天望远镜(Wide-Field Infrared Survey Telescope,WFIRST)是继JWST后的新一代空间望远镜,其宽视场载荷(Wide-Field Instrument,WFI)具有18片Teledyne公司的H4RG红外探测器,是NASA目前最大的红外焦平面阵列。2016年,针对WFIRST的需求NASA在SIDECAR的基础上新研制出一款单片红外焦平面ASIC,即ACADIA[13]。

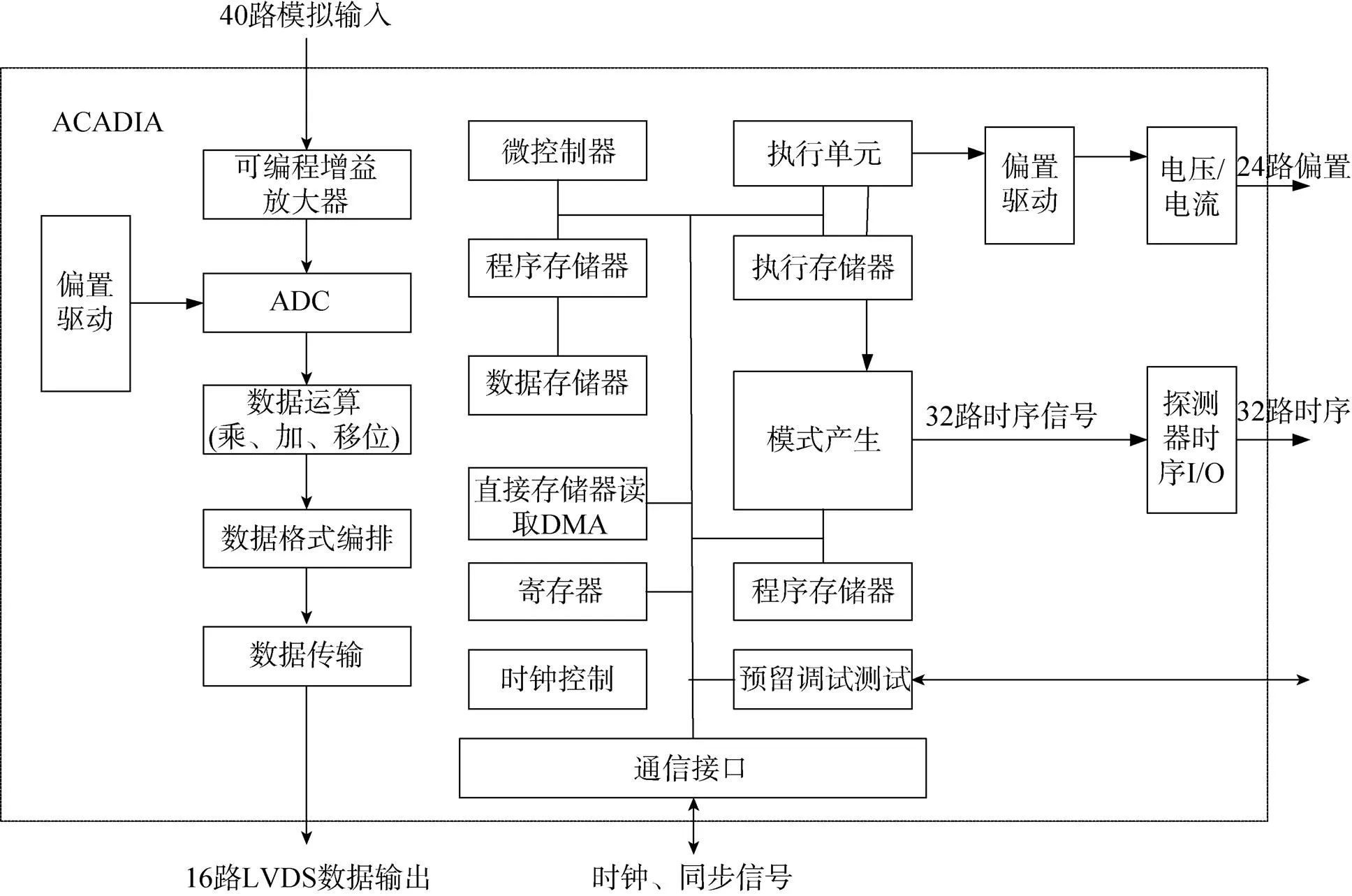

(1)组成结构

ACADIA集成了40通道16bit ADC(可配置为14bit ADC);具有40通道PGA,放大倍数–3~33dB可调;24通道可调偏置,偏置类型既可为电压型也可为电流型;通过微处理器产生32通道输入输出数字时序信号,所有时序信号的周期和相位可编程;另外集成了16bit可编程微控制器和程序存储器、数据存储器,并具有数据运算功能[13],如图3所示。

图3 ACADIA的组成结构

(2)关键电路设计

1)PGA。ACADIA的PGA同样采用电容反馈的结构,但考虑通用性也设计了电阻反馈结构,通过配置寄存器可设置采用电容反馈或电阻反馈,可编程增益调整范围为-3~33dB[14]。

电阻反馈相比电容反馈结构,无需周期性复位,设计简单,但功耗大、噪声大,线性度差。文献[13]对ACADIA放大增益为16时电阻反馈和电容反馈的等效输入噪声进行了测试,如表2所示,可以看出电阻反馈噪声最大,电容反馈并采用CDS的电路设计噪声最小,实际使用时根据不同的需要,选择可编程增益放大电路的反馈类型。

表2 ACADIAPGA噪声测试结果

Tab.2 Test results of the ACADIA preamplifier 单位:μV

2)ADC结构。ACADIA的ADC采用多次采样分步转换的结构,包括两级转换:首先9bit的Flash转换器,对模拟信号进行粗量化,产生高9bit量化位,同时9bit量化位被送入一个DAC产生一个模拟输入的近似值;然后8bit 逐次逼近转换器(Successive Approximation Register,SAR),对模拟输入与DAC产生的近似输入的差进行细量化,得到低8bit量化值。两级之间有1bit的重叠位,用于消除噪声和电路失配引起的不确定误差。这种由Flash ADC和SAR ADC组合的分步转换ADC结构,可实现比单纯SAR结构ADC更高的转换速率,但功耗低于单纯Flash结构ADC,且转换精度高。

ACADIA ADC所用参考电压(Ref_p和Ref_n)、偏置电压均由其内部偏置电压电路产生,通过调整参考和偏置可以改变ADC的带宽、功耗,可以使ADC适用于30~300K的工作温度范围。PGA和ADC之间的采样保持放大器(Sample and Hold Amplifier,SHA)除了具有采样保持和调整模拟信号共模电平的功能外还具有CDS的功能,用于降低PGA产生的kTC噪声。

3)偏置驱动。ACADIA的低噪声偏置驱动部分所有参考电压和参考电流的基准由带隙参考电路产生,带隙参考电压为2V。偏置驱动部分有26个偏置通道,为红外探测器提供偏置电压或偏置电流。每个通道包括一个可编程电压源和一个可编程电流源。每个可编程电压源由一个12bit DAC和一个缓冲放大器构成,该缓冲放大器可以配置为具有一定输出阻抗(几欧)的超低噪声运放,也可以配置噪声略高但超低输出阻抗(几毫欧)的运放,同时缓冲器的带宽和功耗均可配置。ACADIA的偏置驱动部分还可以产生12路内部参考电压和32路内部偏置电流,为芯片内部ADC、运放等提供偏置。

2 欧洲红外遥感器模拟前端处理技术

欧洲红外遥感器模拟前端处理技术目前处于传统设计方法向深低温单片式模拟前端ASIC过渡阶段。如2016年2月发射的Sentinel-3A上的海洋和陆地表面温度辐射计SLSTR载荷和2017年10月发射的Sentinel-5P卫星的对流层监测仪TROPOMI,仍然采用了传统的设计方法。SLSTR载荷采用ST公司的ADC芯片RHF1401进行模拟前端设计[15];TROPOMI模拟前端电路由荷兰空间研究院研制,其将电源供电、时序控制、模拟调理和量化、偏置电压产生四个部分,分为4块PCB实现,PCB之间通过柔板连接,核心器件ADC为Maxwell公司的9240LP,其管芯为ADI公司的工业级14bit ADC AD9240,Maxwell对其进行了抗辐照加固设计[16]。

欧空局主导原定2020年发射的Euclid空间望远镜中采用的模拟前端ASIC为美国的SIDECAR。正是看到了采用SIDECAR实现探测器驱动和处理的优点,欧空局在对欧洲科学探测项目进行技术规划时,指出需要自主研发一款像H2RG+SIDECAR一样的可深低温工作的全探测系统,取代欧洲航天项目中所用Teledyne公司的面阵探测器系列HxRG和模拟前端ASIC SIDECAR。因此欧空局在支持法国SOFRADIR、CEA-LETI、英国SELEX ES等公司开发大面阵红外探测器的同时,也开始支持挪威IDEAS、比利时Caeleste 等公司同步开展单片式模拟前端ASIC的研制[17]。欧洲目前在研的模拟前端ASIC主要有NIRCA(Near-infrared Readout and Controller ASIC)、aLFA-C(Large Format Array Controller)和FAIR(Front-end ASIC for Infrared Detector)。

2.1 NIRCA

NIRCA为欧空局和挪威航空中心支持IDEAS公司研制的单片式模拟前端ASIC,该ASIC可用于MCT、微测辐射热计、QWIP、InGaAs、InSb等多种探测器的驱动和处理。

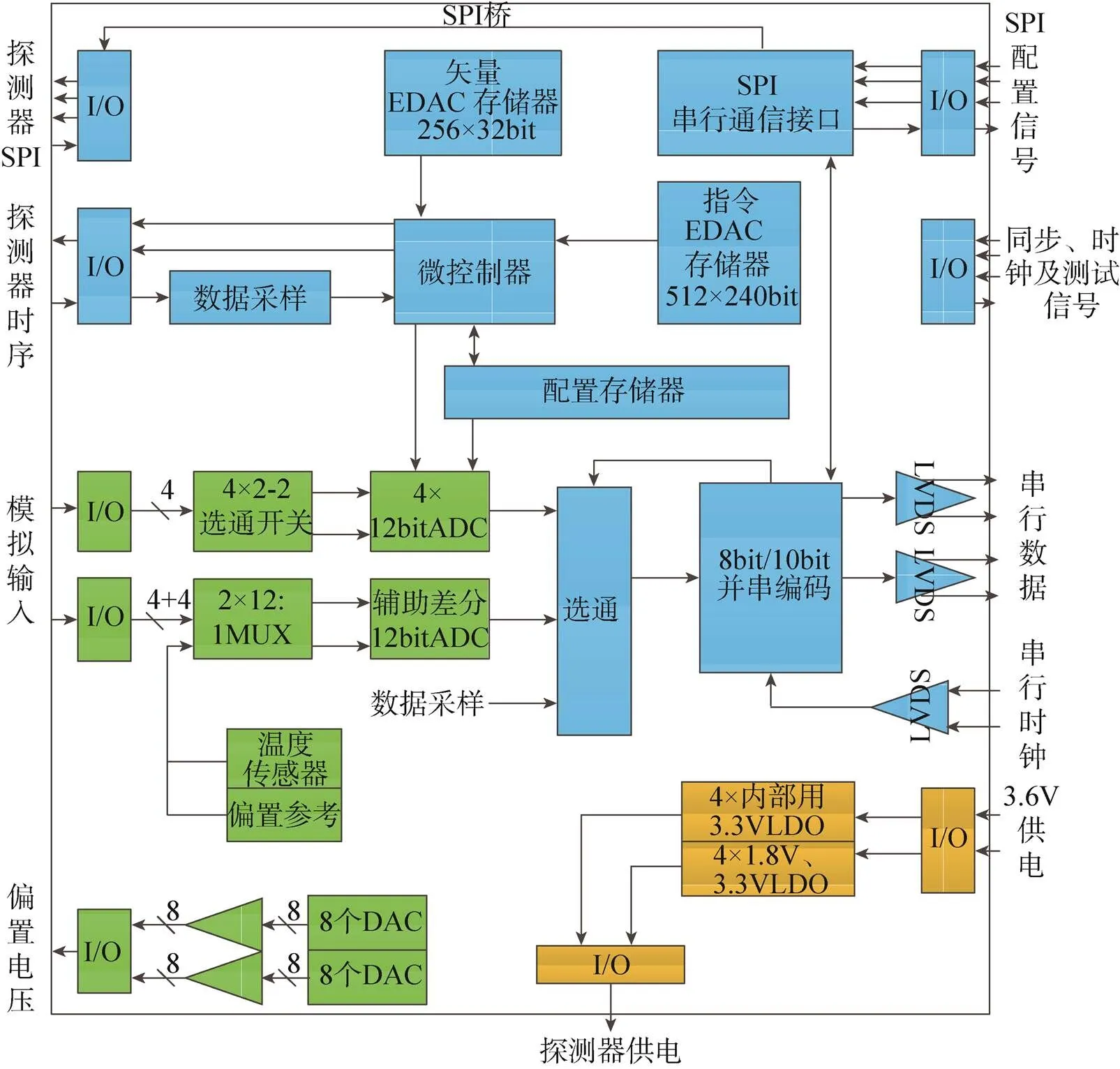

(1)组成结构

NIRCA除了像SIDECAR和ACADIA一样,集成了超低噪声偏置驱动、时序驱动以及多通道模拟前端、微控制器外,同时还集成了8路低压差调整电路(Low Dropout Regulator,LDO),为红外探测器和片内ADC、微控制器等提供大电流的供电电源,其组成结构如图4所示[18]。

图4 NIRCA的组成结构

(2)关键电路设计

NIRCA的模拟调理部分有4个处理通道,每通道包括两个模拟输入MUX、两个模拟输入4︰1MUX,一个PGA和一个12bit逐次逼近型ADC[19],如图5所示。

图5 NIRCA模拟调理结构

NIRCA每通道的差分模拟信号输入后,通过模拟输入MUX,可以对输入的差分模拟信号的极性进行反转[19],该功能对于接收CTIA型红外探测器的模拟输出非常有意义。通常情况下,CTIA型红外探测器积分斜率为负值(即在零光通量输入时,输出模拟信号电压值高;在最大光通量输入时,输出模拟信号电压值低),通过极性反转功能可直接实现探测器输出模拟信号的极性调理,简化电路设计。两个4︰1 MUX可实现PGA的全差分输入、单端输入或模拟通道处理链路失调校正的输入模式切换。

NIRCA的PGA与SIDECAR的设计方法相同,采用了低噪声、低功耗的电容反馈型放大电路,由跨导运放(Operational Transconductance Amplifier,OTA)、共模反馈电路(Common Mode Feed Back circuit,CMFB)、偏置电路、开关和电容网络组成。PGA工作时,首先S1开关闭合,输入电容1对差分输入信号进行采样,OTA的输入和输出反馈被短路,即反馈电容2被复位;然后S1打开,1上的采样电荷对2充电,2和1的容值比决定放大电路的增益,通过改变反馈电容的容值,调整PGA的放大倍数。

NIRCA的12bit ADC采用逐次逼近型ADC(7bit电容DAC,5bit电阻DAC),包括差分DAC、比较器、SAR和电压参考基准。7bit电容DAC对输入的差分信号进行采样,并通过SAR利用二分试探法进行诸位比较,确定量化的高7位,5bit电阻DAC确定量化的低5位。逐次逼近型ADC需要诸位利用二分试探法进行比较,12bit需要12个工作时钟才能完成一次模数转换,因此转换速率较慢,采样频率较低,NIRCA的最高ADC采样频率为3MHz。

2.2 aLFA-C

aLFA-C由比利时Caeleste 公司研制,是欧空局在科学探测任务规划中部署的另一款单片式模拟前端ASIC,欧空局拟将其用于Cosmic Vision项目中[20]。

(1)组成结构

aLFA-C模拟前端处理部分包括4路LDO;4个模拟调理通道;4路监控电路(可以监测模拟输入、温度、芯片状态);16路偏置电压产生电路(每路偏置电压产生电路由10bit DAC+分压电阻+低噪声轨对轨输出缓冲放大器)。模拟部分组成如图6所示[21]。

图6 aLFA-C模拟部分组成框图

(2)关键电路设计

aLFA-C内有4路模拟调理通道,每路模拟调理通道包括 4︰1 MUX、CDS、PGA(增益有1、2、4、8、16五档)、16bit全差分ADC,如图7所示。其中CDS电路可以旁路,PGA将模拟输入信号与DAC产生的失调校正电压进行相减,相减后的信号进行放大,以使模拟信号使用ADC范围,同时可以消除通道间失调不一致,还可将单端模拟信号转换为差分模拟信号。

图7 aLFA-C模拟调理图

aLFA-C通过4︰1 MUX将4路模拟信号分时进行模拟调理,一个模拟调理通道可以处理4路模拟信号,整片可以处理16路模拟信号。

aLFA-C 16bit ADC与NIRCA ADC的拓扑结构相同,也采用逐次逼近的方法实现,16bit分辨率分别通过11bit电容阵列DAC和5bit电阻网络DAC实现。aLFA-C的ADC还设计了校正电路,包括校正电容和5bit校正DAC,对几百开工作温度范围内电容阵列中的电容误差进行补偿校正,提高量化精度。

2.3 FAIR

考虑到高分辨率对地观测或空间望远镜中大面阵或长线列探测器的应用,荷兰空间研究院继承TROPOMI模拟前端处理电路设计经验,于2012年启动模拟前端ASIC研制项目,芯片命名为FAIR[22],该ASIC预计将用于欧空局的EChO(Exoplanet Characterization Observatory)项目中[23-24]。

(1)组成结构

考虑到功耗问题,FAIR不同于NIRCA和aLFA-C,仅将模拟前端处理电路的模拟调理部分、ADC和偏置驱动部分进行集成,未集成数字控制部分和LDO。图8为FAIR的组成结构示意[24]。

图8 FAIR的组成结构

(2)关键电路设计

FAIR的模拟调理部分包括4路信号调理链路,每个调理链路包括模拟链路失调校正电路、PGA、16bit ADC;其中模拟链路失调校正电路的失调校正电压通过DAC产生,失调校正电压的调整精度为24bit,调整范围为0.5~3V;PGA的增益为1倍、2倍、4倍、8倍可选。FAIR单路模拟调理部分组成示意如图9所示。

图9 FAIR模拟调理部分组成示意

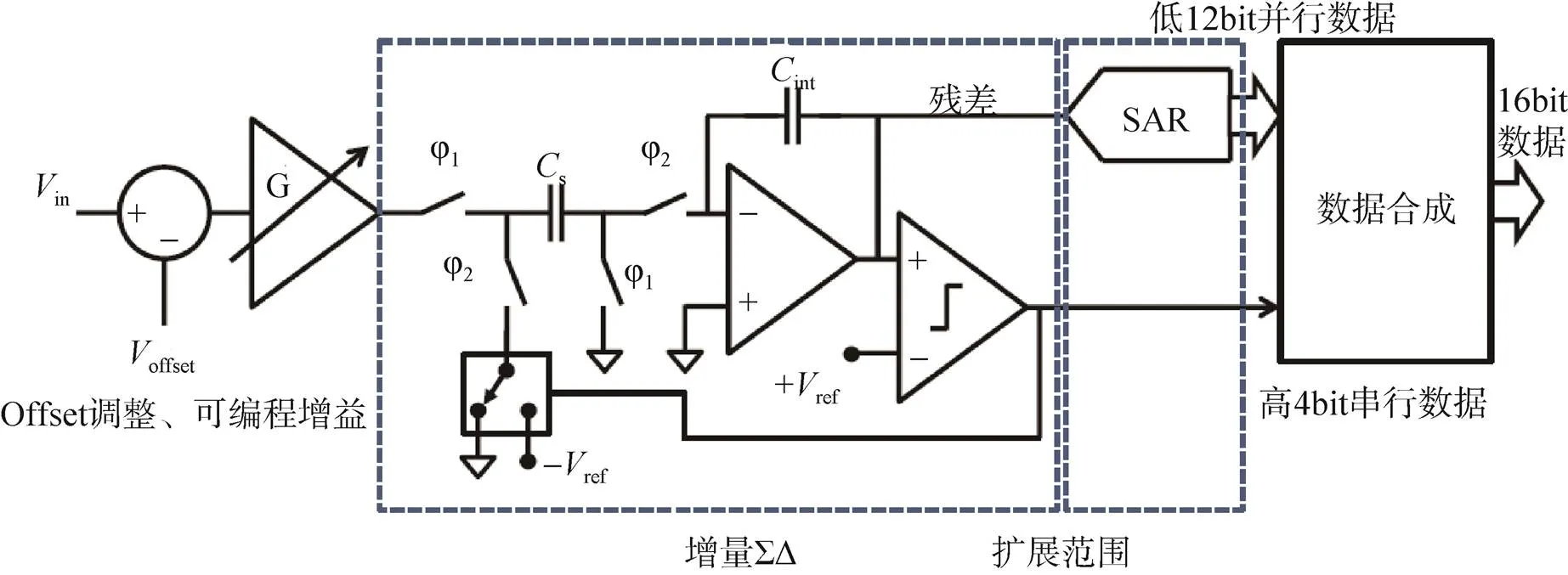

1)扩展范围的增量∑△ADC。增量∑△ADC是所有ADC拓扑结构中转换精度最高、失真和噪声最低的ADC拓扑结构,它的缺点是转换时间长,一次采样转换需要几百个时钟周期,因此转换速率非常低,通常在几千赫兹~几十千赫兹。在FAIR项目中,为了提高ADC分辨率,同时兼顾转换速率,FAIR中的16bit ADC采用增量累加ADC和逐次逼近ADC相结合的量化方法,在转换速率为1MHz时,有效量化位数达到15bit,这种ADC被称为扩展范围的增量∑△ADC[24]。

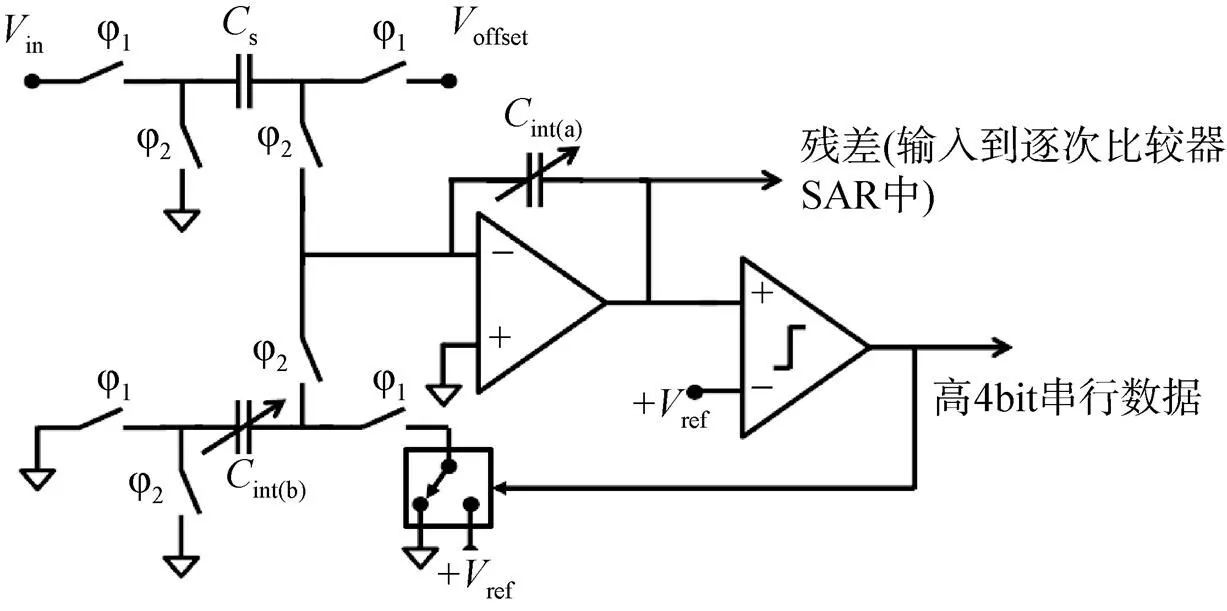

另外,FAIR中还提出一种新的前端处理方法[24],将模拟链路失调校正、可编程增益放大和增量积分采用一个放大器实现,与传统增量∑△ADC用两个运放来实现可编程增益放大和偏置校正的前端处理方案相比具有低噪声、低功耗、高线性度的优点。FAIR中带有增益和失调校正的增量积分电路如图10所示,其工作原理为:首先可调电容int(a)=int(b),当φ1闭合,φ2打开时,采样电容s对in减去offset得到的信号电压采样;当φ2闭合,φ1打开时,s采到的电压值在int(a)上积分,每个像元周期,积分电路输出的残差和固定的参考+ref比较,超出的电荷量从int(a)上减掉,减操作通过int(b)充电到+ref实现。经过16个积分循环,ADC的高4bit产生,低12bit由逐次逼近型ADC对输出残差量化得到。PGA的增益由s和int(a)的比值决定。

图10 FAIR增量∑△ADC可编辑增益放大和Offset校正电路

2)偏置驱动。FAIR偏置驱动部分可产生2路偏置电压,其偏压调整精度为24bit,远高于NIRCA和aLFA-C的调整精度。每路偏置驱动电路由24bit DAC、运放和PMOS管构成,其产生原理与SIDECAR相同,通过24bit DAC产生所需设置的偏置电压,通过运放和PMOS管构成负反馈,产生满足驱动要求的偏置电压。

3 特点分析

美国、欧洲单片式模拟前端处理ASIC的关键技术指标如表3所示。

通过对美国、欧洲单片式模拟前端处理ASIC的关键技术指标和关键电路设计调研,可以看出单片式模拟前端ASIC设计具有以下特点:

1)低噪声设计。单片式模拟前端ASIC的低噪声设计主要体现在PGA、ADC和偏置电压产生等部分,具体为:PGA均采用低噪声、低功耗的电容反馈结构,周期性复位消除电容漏电流,复位引入的kTC复位噪声通过CDS的方法进行抑制使PGA的等效输入噪声仅为几个微伏;在采样速率满足要求的情况下,ADC选用增量∑△ADC、逐次逼近ADC等高分辨率ADC结构;偏置电压产生电路均采用带隙基准+高精度DAC +低噪声运放+低通滤波的方法,将偏置电压噪声降为几个微伏,实现超低噪声设计。

表3 关键技术指标对比表

Tab.3 Specifications of analog front end ASICs

2)低功耗设计。低温真空杜瓦通过制冷机制冷才能达到探测器所需的工作温度,单片式模拟前端ASIC放置在低温真空杜瓦中,必须进行低功耗设计(如:SIDECAR和ACADIA的单通道模拟调理和模数转换仅为几mW),以降低制冷机的功耗和设计难度。低功耗设计方法具体为:①芯片各部分电路采用低功耗拓扑结构进行设计,如PGA选用低功耗的电容反馈结构而不选用高功耗的电阻反馈结构;ADC多选用低功耗的扩展范围增量∑△ADC、逐次逼近ADC而未选用高功耗的Flash ADC结构。②芯片本身具有待机省功耗模式,芯片内部多个处理通道可独立设置工作模式,对不用的通道可设置为省功耗模式。③芯片内部的偏置电压和参考均设计为可调,通过调整参考和偏置改变电路的工作点,在低功耗的情况下使芯片性能达到最优。

3)深低温工作。美国、欧洲研制的单片式模拟前端ASIC均具有深低温工作能力,这主要是为了可以将单片式ASIC放置在低温真空杜瓦中,与探测器读出电路直接互联,减少模拟信号传输距离,提高信号传输品质,降低传输干扰和系统噪声。目前芯片设计的仿真模型均为室温或军温范围模型,无准确的深低温器件模型,因此根据ACADIA、aLFA-C 和FAIR的深低温设计方法[21,24],总结模拟前端ASIC深低温设计需要关注的设计要点如下,为我国开展深低温模拟前端ASIC设计提供参考。

①模拟部分,在器件室温模型的基础上,根据类似电路的深低温特征(如:在深低温条件下,MOSFET的阈值电压增加,载流子迁移率增加;晶体管跨导m增加)进行降额设计,预留出足够的设计余量。

②无源器件选择耐低温低掺杂电阻。

③数字部分,随着温度降低,信号的建立上升或下降时间变快,设计时需对信号的建立和保持时间进行降额设计。

④在芯片设计时,设置多个参数可调(如:ACADIA ADC内部的参考电压和偏置电压均设计为可 调,通过调整参考电压和偏置电压改变ADC的工作点),以适应几百开(几十开到三百开)的工作温度范围。

4 结束语

随着红外遥感器分辨率逐渐提高,探测器像元数和输出通道数在成倍地增加,采用单片式深低温模拟前端ASIC实现红外探测器的模拟前端处理是未来发展趋势。我国红外遥感器模拟前端处理电路目前仍以标准集成电路通过PCB来互联设计的传统方法为主,与国外深低温单片式模拟前端ASIC还有差距。结合国内微电子设计水平和工艺现状,给出分步式发展建议:1)尽快开展电子器件的深低温特性研究。对模拟前端处理电路所用的工业级(–45℃~85℃)或军级(–55℃~125℃)标准集成电路进行深低温试验,对室温条件和深低温条件下器件的关键技术指标进行对比(如:运放的噪声、带宽、压摆率、失调电压等指标),总结器件在深低温条件下的指标变化规律,为后续进行单片式深低温ASIC设计提供参考;2)军温模块级ASIC研究设计。考虑到功耗问题、模数混合电路设计复杂度以及器件深低温特性的不确定性,首先仅对多通道模拟调理、多通道ADC和偏置驱动部分进行集成,对其低噪声和低功耗设计进行技术攻关,实现模拟前端处理技术关键电路部分军温ASIC的设计;3)在以上两项研究完成的基础上,根据深低温试验结果和军温模块级ASIC设计研究结果,进行高集成度单片式深低温模拟前端ASIC的设计。

[1] 范文龙. 采用焦平面探测器的长波红外推扫成像信息获取与处理技术[D]. 上海: 复旦大学, 2014. FAN Wenlong. Image Acquisition and Processing of Long-wave Push Broom Infrared Detector[D].Shanghai: Fudan University, 2014. (in Chinese).

[2] 刘兆军, 周峰, 李瑜. 航天光学遥感器对红外探测器的需求分析[J]. 红外与激光工程, 2008, 37(1): 25-29. LIU Zhaojun, ZHOU Feng, LI Yu. Demands Analysis of IR Detectors for Space Remote Sensor[J]. Infrared and Laser Engineering, 2008, 37(1): 25-29. (in Chinese).

[3] 王华, 魏志勇, 张文昱, 等. 480×6红外探测器信号处理电路设计[J]. 红外技术, 2009, 31(9): 504-512. WANG Hua, WEI Zhiyong, ZHANG Wenyu, et al. Design of 480×6 Infrared Focal Plane Array Signal Processing Circuit[J]. Infrared Technology, 2009, 31(9): 504-512.(in Chinese).

[4] 张文昱, 李涛. 空间相机上第二代红外探测器驱动电压供电电路设计[J]. 航天返回与遥感, 2011, 32(3): 51-56. ZHANG Wenyu, LI Tao. Bias Voltage Supply Circuit Design for the Second Generation Infrared Detector on Space Camera[J]. Spacecraft Recovery & Remote Sensing, 2011, 32(3): 51-56. (in Chinese).

[5] KOZLOWSKI L J, LOOSE M, JOSHI A M, et al. Low Power System-on-chip FPAs[J]. SPIE, 2002, 4820: 525-534.

[6] LOOSE M, LEWYN L, DURMUS H, et al. SIDECAR Low-power Control ASIC for Focal Plane Arrays Including A/D Conversion and Bias Generation[J]. SPIE, 2003, 4841: 782-794.

[7] BELETIC J, BLANK R, GULBRANSEN D, et al. Teledyne Imaging Sensors: Infrared Imaging Technologies for Astronomy & Civil Space[J]. SPIE, 2008, 7021: 70210H-1-70210H-14.

[8] REUTER D C, RICHARDSON C M, PELLERANO F A, et al. The Thermal Infrared Sensor (TIRS) on Landsat 8: Design Overview and Pre-Launch Characterization[J]. Remote Sensing, 2015(7): 1135-1153.

[9] BAI Y B , CHO H, JHABVALA M. Manufacturability and Performance of 2.3-μm HgCdTe H2RG Sensor Chip Assemblies for Euclid[J]. SPIE, 2018, 10709: 1070915-1-1070915-16.

[10] Teledyne Technologies. SIDECAR™ ASIC Development Kit & Focal Plane Electronics [EB/OL]. (2017-01) [2019-10-27]. http:// www.Teledyne-si.com.

[11] DORN R J, ESCHBAUMER S, HALL D N B, et al. Evaluation of the Teledyne SIDECAR ASIC at Cryogenic Temperature Using a Visible Hybrid H2RG Focal Plane Array in 32 Channel Readout Mode[J]. SPIE, 2008, 7021: 70210Q-1-70210Q-12.

[12] LOOSE M, BELETIC J, GARNETT J D, et al, High-performance Focal Plane Arrays Based on the HAWAII-2RG/4RG and the SIDECAR ASIC[J]. SPIE, 2007, 6690: 66900C-1-66900C-14.

[13] SMITH B, LOOSE M, ALKIRE G, et al. Detector Control and Data Acquisition for the Wide Field Infrared Survey Telescope (WFIRST) with a Custom ASIC[J]. SPIE, 2016, 9915: 99152V-1-99152V-18.

[14] SMITH B, LOOSE M, ALKIRE G, et al. The ACADIA ASIC-detector Control and Digitization for the Wide Field Infrared Survey Telescope (WFIRST) [J]. SPIE, 2018, 10709: 107090T-1-107090T-18.

[15] COPPO P, MASTRANDREA C, STAGI M, et al. The Sea and Land Surface Temperature Radiometer (SLSTR) Detection Assembly Design and Performance[J]. SPIE, 2013, 8889: 888914-1-888914-24.

[16] VOORS R, VRIES J, VALK N C J, et al. The TROPOMI Instrument: First H/W Results[J]. SPIE, 2013, 8889: 88890Q-1-88890Q-8.

[17] DUVET L, BAVDAZ M, CROUZET P E, et al. European Space Agency Detector Development for Space Science: Present and Future Activities[J]. SPIE, 2014, 9154: 915403-1-915403-25.

[18] PAHLSSON P, STEENARI D, ØYA P, et al. NIRCA ASIC for the Readout of Focal Plane Arrays[J]. SPIE, 2016, 9189: 91192C-1-91192C-18

[19] MEIERA D, BERGE H K O, HASANNEGOVIC A, et al. Development of an ASIC for the Readout and Control of Near-infrared Large Array Detectors[J]. SPIE, 2014, 9154: 915421-1-9154 915421-9.

[20] LEMMEL F, HAAR J, BIEZEN J, et al. Large Format Array Controller(aLFA-C): Tests and Characterization at ESA[J]. SPIE, 2016, 9915: 99151N-1-99151N-15.

[21] GAO P, DUPONT B, DIERICKX B, et al. Cryogenic and Radiation Hard ASIC Design for Large Format NIR/SWIR Detector[J]. SPIE, 2014, 9241: 92410Z-1-92410Z-8.

[22] SRON. ASIC Development-FAIR[EB/OL]. (2019)[2019-10-27]. http://www.sron.nl.

[23] FOCARDI M, GIORGIO A M D, FARINA M, et al. EChO Payload Electronics Architecture and SW Design[J]. Experimental Astronomy, 2016(2/3): 813-839.

[24] SCHRADER J H R, GARAKOUI K, SCHINKEL D. FAIR, a Front-end ASIC for Infrared Detector Readout [EB/OL]. (2015) [2019-10-27]. http:// www.indico.cern.ch.

Research on the Analog Front End Processing Technology of Foreign Space Infrared Remote Sensors

WANG Hua1LI Qiang1BO Shu1YAN Jingchun1CAI Shuai1FU Shuai1ZHAO Yuang2HE Qiangmin1

(1 Beijing institute of space Mechanics & Electricity, Beijing 100094, China)(2 Inner Monggolia Electric Power Science & Research Institute, Hohhot 010020, China)

In this paper, the analog front end processing technology of the foreign space infrared remote sensors are researched. First, the block diagram, specification and key circuit design of infrared analog front end processing ASICs in America and Europe are introduced. Then, technical characteristics of low noise, low power consumption and cryogenic operation of foreign infrared analog front end processing ASICs are analyzed. Proposals for developing the analog front end processing technology of space infrared remote sensing in China are given. The research can provide reference for the analog front end processing technology of space infrared remote sensor in China.

infrared remote sensing; analog front end; low noise; space camera

O435; TH74

A

1009-8518(2020)05-0083-12

10.3969/j.issn.1009-8518.2020.05.010

2020-06-20

国家重大科技专项工程

王华, 李强, 薄姝, 等. 国外空间红外遥感器模拟前端处理技术发展研究[J]. 航天返回与遥感, 2020, 41(5): 83-94.

WANG Hua, LI Qiang, BO Shu, et al. Research on the Analog Front End Processing Technology of Foreign Space Infrared Remote Sensors[J]. Spacecraft Recovery & Remote Sensing, 2020, 41(5): 83-94. (in Chinese)

王华,女,1980年生,2007年获中科院西安光学精密机械研究所光学工程专业博士学位,研究员,研究方向为空间遥感相机信号处理技术。E-mail:huawang8010@126.com。

(编辑:王丽霞)