应用于薄膜透光均匀性检测的锁相电路设计

2020-01-02高忠坚张锐戈饶连周

高忠坚,张锐戈,饶连周,郑 华

(1.三明学院 机电工程学院,福建 三明,365004;2.福建师范大学 光电信息学院,福建 福州,350117)

薄膜的透光均匀性影响光学产品的一致性及光学器件的性能[1]。 当前普遍采用是机械法、电学法和光学法实现薄膜均匀性检测[2]。 机械法和电学基本上是接触式测量对薄膜容易造成损害[3];纯光学法如椭圆偏振法、干涉测量法、光度测量法等具有测量速度快、精度高特点,但对环境依赖性强、抗干扰能力差,只能在暗室中进行测量[4]。 近年来,光电结合的高吸收型滤光片透光均匀性性测试系统[5]、回反射检测法[6]等可在亮场环境中直接测量。 这些方法的共同特性都使用了锁相放大器LIA(Lock-in Amplifier)。

亮场环境的薄膜透光均匀性检测系统具有下述挑战(1)发光源在传输过程中容易被环境的杂散光干扰需调制;(2)薄膜样品的厚度变化较小只能产生微弱的检测信号;(3)检测结果需与不同薄膜厚度的光信号强度成正比。 锁相放大器依据其相关性技术和通频带窄的设计在一定程度上克服背景光噪声和电路噪声,可降低检测误差、提高系统的检测性能,同时具有放大交流输入、直流输出的特点恰好可解决上述挑战[7]。

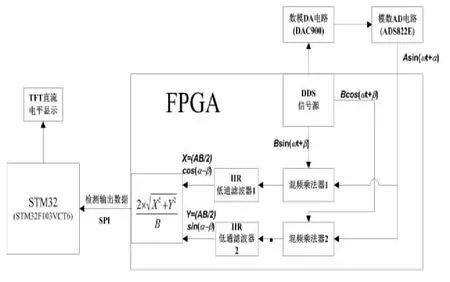

基于FPGA 设计的双通道锁相电路是锁相放大器中重要的组成部分。该电路除了FPGA 电路还包括数模DA 电路、 模数AD 电路、STM32 显示电路。 FPGA 电路内部包括直接数字式频率合成器DDS(Direct Digital Synthesizer)、混频乘法器、IIR 数字滤波器、SPI 串行通信等其他运算模块组成。 其中DDS 产生激光调制信号和内部参考信号,与传统的锁相放大器相比不需要频率跟踪和相位调整电路;而IIR 滤波器采用只有3 阶的chebyshev II 函数设计。这二者都在一定程度上减少了锁相电路的设计复杂度和FPGA 片内逻辑资源的使用,使其可在4 608 个逻辑单元的EP2C5T144C8 芯片上实现。

1 薄膜透光均匀性检测系统

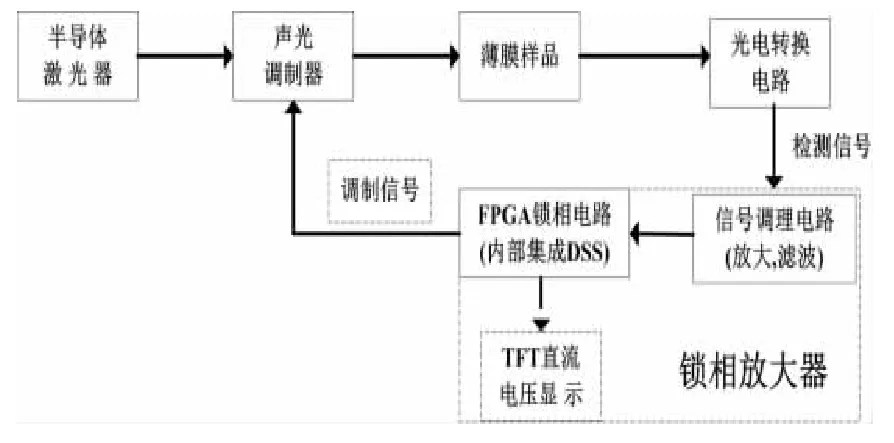

薄膜均匀性检测系统包括半导体激光器、声光调制器、薄膜样品、光电转换电路、信号调理电路、FPGA 锁相电路等如图1 所示。薄膜样品选用ZnO,此薄膜是透光导电薄膜常应用于光伏电池和液晶显示的透明电极和窗体材料上[8]。其在可见光至近红外是弱吸收区[9]同时基于现有的实验器材最终选择了波长为650 nm的红色激光。

图1 薄膜透光均匀性检测系统框图

图1 用 FPGA 内部的 DDS 作为激光的调制信号源,激光经受调制的声光调制器产生布拉格衍射后垂直透射ZnO 薄膜样品,由相对应波段的光电探测器接收转换透过样品的光强信号。 锁相放大器通过信号调理电路对检测信号放大、滤波完成初步的信噪比改善,后经FPGA 锁相电路的相关检测同步解调出检测信号中的同频成分,最后得出的直流电压幅值大小正比于该点的光强大小。 通过三维位移台逐步改变薄膜样品的检测位置,对比不同位置的薄膜检测值即可鉴别一定区域内薄膜的均匀程度。

2 FPGA双通道锁相电路的设计原理

本设计在FPGA 内部包括直接数字式频率合成器DDS、 混频乘法器、IIR 数字滤波器、SPI 串行通信等其他运算模块组成。 除了FPGA 以外还包括数模DA 电路、模数AD 电路、STM32显示电路。 FPGA 双通道锁相电路的设计框图如图2 所示。

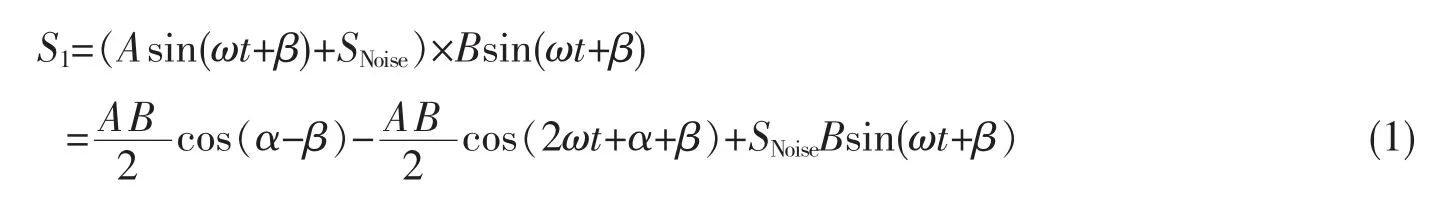

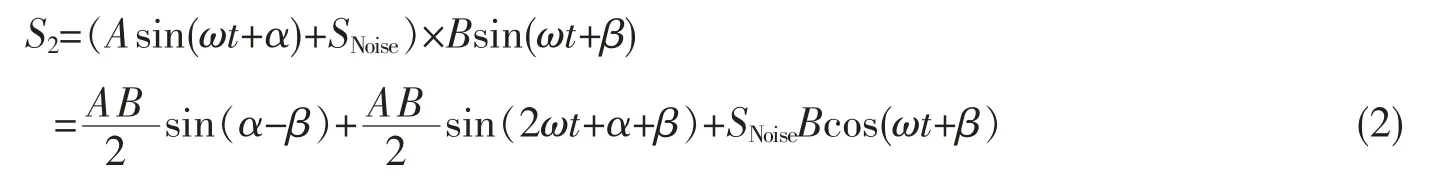

FPGA 内部的 DDS 模块和数模 DA 电路组成信号发生器产生正弦波,一方面作为调制信号源另一方面作为内部参考信号Bsin(ωt+β)和 Bcos(ωt+β)。 设第一通道参考信号为 Bsin(ωt+β),模数 AD 电路采样得到的输入信号为:同频率的待测信号Asin(ωt+β)加上噪声信号SNoise, 通过混频乘法器可得:

图2 FPGA 双通道锁相电路的设计框图

式(1)中:A 是待测信号电压幅值;B 是参考信号电压幅值;α 表示待测信号的相位;β 表示参考信号的相位;ω 为信号角频率。第一项当输入信号和参考信号稳定后 cos(α-β)就是个定值,第一项即为直流。 式中第二项为参考信号的二倍频信号,经低通滤波后将被滤除。 式中第三项因噪声信号SNoise的随机特性与内部参考信号Bsin(ωt+β)无相关,其积分结果通常为零,最后只剩下直流分量 S1=ABcos(α-β)/2。

同理,第二通道的输入信号还是为Asin(ωt+α)+SNoise,但DDS 通过不同的ROM 查找表(波形存储表)直接产生与第一通道Bsin(ωt+β)相差90 度的参考信号Bcos(ωt+β),即两通道正交参考信号波形。

第二通道的输入信号输入信号和第二通道参考信号经混频乘法器后,得

将式(2)中信号经低通滤波后,第二项被滤除,第三项SNoiseBcos(ωt+β)=0,只剩下第一项直流分量

从式(1)和式(2)可知直流分量S1和S2都与输入信号和参考信号两者之间的相位差有关。对S1和S2取平方和后开方,即可得

由式(3)可知只要知道参考信号的幅度值B,就可获得输入信号的幅值A 的值,以上为双通道锁相电路的基本原理。

3 各个模块功能的实现

3.1 直接数字式频率合成器DDS与数模DA电路

DDS 模块由频率控制字、相位累加器、同步寄存器、波形查找表、低通滤波器构成[10]。实现原理为输入一个频率控制字,经同步寄存器和累加器产生10 位的数据作为正弦波ROM 的查表地址。 查表输出10 位的正弦波作为DAC900 芯片的数字量输入。 DA 芯片输出的是近似正弦波的梯度波,后级还需加低通滤波器平滑滤波。

DDS 模块只能设置正弦波的频率,输出电压可通过DA 芯片后端增加运放电路调整。 其频率控制字

式(4)中 f0为输出频率,fC为时钟频率,DDS 理论上输出频率为时钟频率的二分之一。 实际上由于低通滤波器过渡带的原因,f0最高输出频率为 0.4×fC[10]。 DAC900 芯片为 TI 的 10 位、双通道、165 Msps的输出更新速率,而时钟频率为50 MHz,理论上最高输出频率为20 MHz,实际为更小,这对于一般应用是完全足够的[11]。 在实现过程中,该芯片的输出需无符号型(unsigned)数据,而波形查找表因混频乘法器的要求为符号型(signed)数据,这其中有符号和无符号的数据主要差别在于最高位的符号位,故需先将DA_Signed 带符号数据值加上 29=512 后转化成 unsigned 数据(DA_OUT)输出给DA 芯片。 二者的波形如图3 所示。

图3 signed 与 unsigned 数据差异

3.2 模数AD电路与混频乘法器模块

模数AD 电路采用AD 芯片是TI 公司位宽为10 位、采样率为40 MHz 的ADS822E,该芯片电源电压5 V,内部参考电压VREFB=1.5 V,VREFT=3.5 V,为了方便输入交直流信号,可通过抬高输入通道偏压使输入信号的电压范围在-1~1 V[10]。

因AD 采样得到的信号为无符号型的10 位数据(如下图AD_IN),而乘法器要有混频的效果需符号型数据,故在输入信号数据值在混频操作前减去512 即可转化成符号型数据,这一操作相当于对输入信号增加偏置电路,将不会对检测产生影响。 图4 在AD 芯片无输入数据的情况下,用Signal-TapII 观察到采样进来的unsigned(AD_IN)和 signed(ADdata)数据,存在一定的偏置误差会导致正弦波的波形不对称,将对交流小信号产生影响,导致最终的检测结果误差,故需减去偏差值34 调整,如图4 所示。

图4 AD 模块存在的偏置电压

3.3 数字滤波器模块

根据冲激响应的不同,将数字滤波器分为有限冲激响应(FIR)滤波器和无限冲激响应(IIR)滤波器。 对于FIR 滤波器,冲激响应在有限时间内衰减为零,输出仅取决于当前和过去的输入信号值[12]。对于IIR 滤波器,冲激响应理论上应是无限持续,输出不仅取决于当前和过去的输入信号值,也取决于过去的信号输出值[13]。 本设计之初选用具有良好的线性特性的FIR 设计,优势在于Altera 已有FIR IP 核可大大降低设计难度,但FIR 要想得到极窄的低通滤波器LPF 要比IIR 多两倍以上的逻辑单元,这将导致芯片CycloneII EP2C5T144C8 的内部逻辑单元不足,所以采用IIR 滤波器。

IIR 滤波器总共分为4 种,本设计用级联型能准确地实现滤波器的零、极点,且参数影响较小,使用较广泛[14]。 IIR 的设计步骤如下

(1) 滤波系数获取

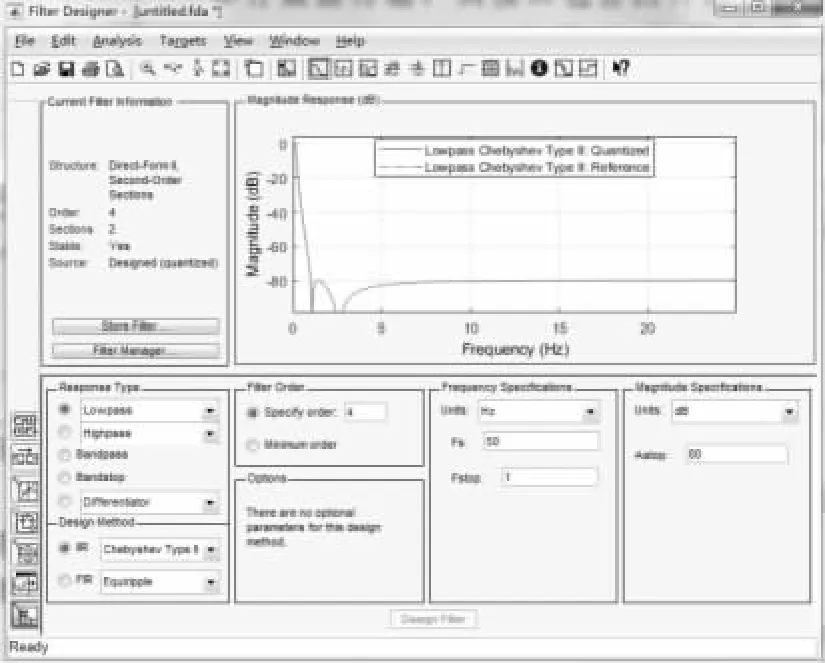

IIR 滤波器采用chebyshev II 函数设计阶数3、级数为4,采样频率50 Hz,截至频率 1 Hz,阻带衰减为80 dB,使用Matlab 的Filter Design & Analysis Tool(FDATool)工具设计,设计界面如图5 所示。

(2) 滤波系数处理

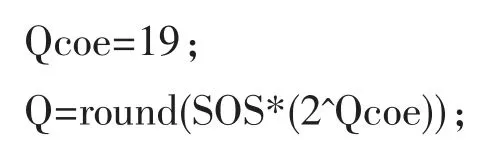

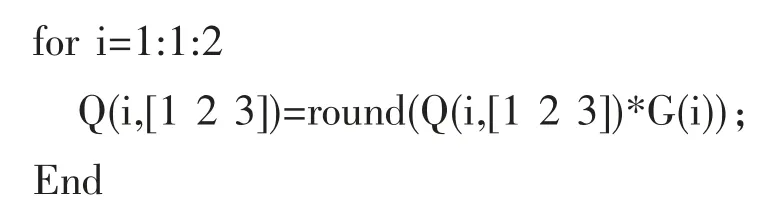

从图5 中获得的 SOS、G 分别是零点极点滤波系数、增益。 为了加快FPGA 的运行速度可将滤波系数量化为整数。 放大倍数一般取 2 的整次幂,取整的位数越多逼近的程度越好,但所占的硬件资源也越大,速度也会减慢[15]。 量化位数的截断选取可由 FDATool 导入取整后的系数进行分析。 针对20 位输入的数据位宽,从FDATool 得到的截断位数是18 位对滤波结果影响较小。 本文选取的截断量化位数19 位,零点 SOS 需乘上增益 G 以保证计算的精度和系统的稳定性。 Matlab 量化程序如下:

图5 低通滤波FDATool 参数设置图

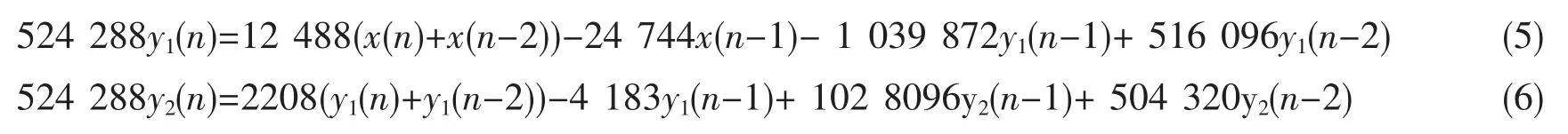

根据级联型结构可直接写出量化后的滤波器的差分方程如下:

IIR 的实现是依据式(5)和式(6)实现的。 因CycloneII EP2C5T144C8 芯片的乘法器资源不够,滤波器设计采用左/右移替代乘/除法运算。 需注意:每一级滤波器的最终数据输出位宽需要通过MATLAB 量化仿真来确定,输出位宽截取太长浪费FPGA 资源,截取太短影响滤波效果甚至会出错。

(3) 滤波器仿真

通过前两个步骤完成滤波器的设计,可通过Modelsim 软件对设计好的截至频率为1 Hz 滤波器进行仿真,如图6 所示。

图6 中输入信号 din 为 Matlab 产生的纯白噪声信号;输出信号dout 为白噪声经过滤波的结果。 从中可知窄带滤波器能有效地抑制噪声。

图6 低通滤波器仿真图

3.4 SPI与STM32显示模块

FPGA 锁相检测的结果即直流数据利用串行外围接口SPI 总线发送到STM32 单片机的液晶上显示。 本设计使用STM32F103VCT6 上硬件已实现好的SPI2 与FPGA 通信。 在STM32 单片机做主机,FPGA 做从机的情况下,只需在FPGA上编写SPI 通信协议即可实现二者通信。 STM32 显示模块采用320*240 分辨率的 2.8 寸TFT 液晶屏。

4 调试与验证

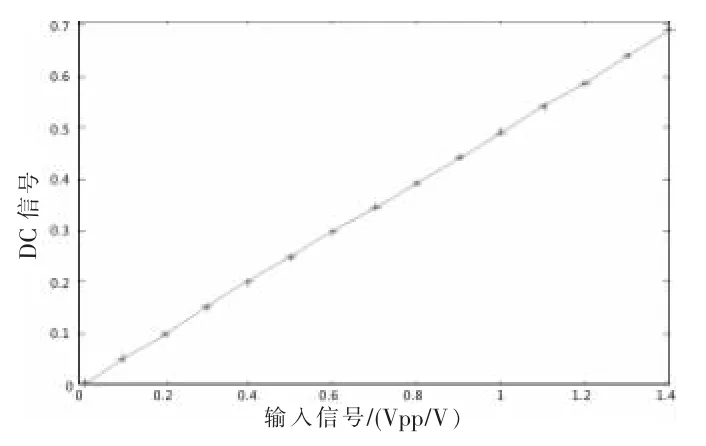

为了验证FPGA 双通道锁相电路的可行性,可将DA 电路的输出与AD 电路的输入直接相连。对设计的锁相电路进行输入输出特性曲线测试。 输入信号的幅度从 0 V 增加到1.4 VPP,频率为48 kHz,在 SMT32 显示模块对输出直流信号进行直流放大后显示保存,最后得到的输入输出特性曲线如图7 所示。

图7 可以看出锁相电路输入输出基本上成一条直线,线性度良好。 在检测过程中发现锁相电路可测量最小信号MDS:10 mVPP。

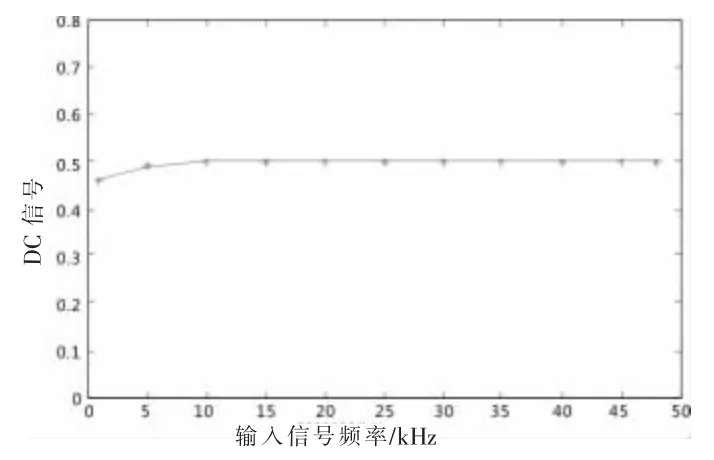

对设计的锁相电路进行幅频响应特性的测试。输入的信号频率从50 Hz 到50 kHz,在 SMT32 显示模块对DC 信号进行显示保存,如图8 所示。

图7 锁相电路输入输出特性曲线图

图8 锁相电路幅频特性曲线图

图8 可以得到锁相电路的输入信号频率范围:1 kHz~48 kHz。 当输入信号频率低于1 kHz 或高于48 kHz 时,输出的DC 信号不稳定。

5 结语

鉴于薄膜透光均匀性检测系统抗干扰能力差、检测信号微弱、输出电压值与输入光信号强度成正比等原因,设计了一种自带DDS 的FPGA 双通道锁相电路。 文中首先对薄膜透光均匀性检测系统的工作原理和FPGA 双通道锁相电路的设计原理进行介绍。 其次详细阐述了FPGA 双通道锁相电路的组成,尤其是FPGA 芯片内部设计的DDS 电路和只有3 阶的IIR 滤波器分别简化了设计、减少了FPGA 逻辑资源的使用,最终在只有4608 个逻辑单元EP2C5T144C8 芯片上实现。通过调试与验证表明该电路的实现与理论一致并具有良好的输入输出特性和幅频特性符合薄膜透光均匀性检测系统的设计要求。