基于FPGA的BAN认证算法硬件实现

2019-12-26林金朝赵艳霞

邓 鸿,林金朝,庞 宇,赵艳霞

(重庆邮电大学 光电信息感测与信息传输实验室, 重庆 400065)

0 引 言

无线通信、嵌入式系统和集成电路技术的进步使传感器网络技术和生物医学工程相结合的人体局域网(body area network,BAN)成为一种有前景的网络模式。BAN由许多可在身体上穿戴或植入的低功耗智能小型传感器组成[1]。BAN能够通过病人身体内或身边的智能医疗传感器实时收集诸如心率,血压和脉搏等人体各项生理参数信息,智能传感器节点可以通过诸如个人数字助理或移动设备将实时数据发送到远程医疗服务端,这样便实现了远程医疗监控。医生和其他医务人员可以根据这些数据,获得患者状态并提供适当的临床诊断[2]。

2012年制定的IEEE 802.15.6人体局域网标准中,将通信安全模式划分为3种级别[3]:①安全级别0:不安全的通信。消息在不安全的帧中传输,即没有提供消息真实性和完整性验证的措施、机密性和隐私保护以及重放保护;②安全级别1:认证但不加密。消息在安全认证但未加密的帧中传输,即提供消息真实性和完整性验证的措施,但不提供机密性和隐私保护;③安全级别2,认证和加密。消息在安全的身份认证和加密帧中传输,即提供消息真实性和完整性验证,机密性和隐私保护以及重放保护[4]。

BAN收集或传输的数据非常敏感和重要,因为这些是临床诊断的基础。此外,从病人的角度来看,隐私也是一个重要问题,因为生物医学数据是高度机密的,应该小心处理、传输和存储[5-6]。为BAN设计的智能传感器节点应具备足够的安全措施能力,在所有通信过程中都应该保证认证、数据机密性、完整性、不可否认性和隐私保护,以防止信息泄露给未经授权的用户。结合IEEE 802.15.6标准,对安全级别2层面,提出了基于Challenge/Response方式的BAN身份认证方案。

基于Challenge/Response方式的BAN身份认证就是终端向节点发送“挑战”信息序列,节点接收“挑战”后,做出对应的“应答”。认证过程如下。

1)终端向节点发出节点证书请求。

2)节点将自己的证书传给终端,终端识别该节点的身份是否合法,若不是,则不做进一步的处理。

3)终端随机产生一个64 bit的“挑战”,发给节点。

4)节点收到“挑战”后,结合秘钥使用HMAC-SHA256算法生成“应答”,传给终端。

5)终端将节点的“应答”与自己计算的结果进行比较,若两者结果相等,则通过认证。反之,认证失败。

认证过程步骤1),2)中,出于测试,证书是自签名的,由openssl创建。证书的验证过程遵循由国际电信联盟制定的数字证书—X.509标准[7]。本文主要针对于硬件底层上来实现后面的验证算法,所以证书验证步骤由协议栈来处理。

1 SHA256函数

安全散列算法(secure hash algorithm,SHA)系列算法之一,由美国国家标准与技术研究院发布,是联邦信息处理标准所认证的安全散列算法。SHA256输入的最大长度不超过264bit,输入按512 bit的块进行处理,输出为256 bit的数据,即32个字节,故称SHA256,其算法步骤如下。

步骤1附加填充比特。在输入末进行比特填充,使得填充后的比特长度为L,L模512等于448。填充的比特个数为1~512,填充比特串的最高位为1,其余位为0。

步骤2附加输入长度值。步骤1的基础上再附加一个64 bit的输入长度值,从而使得输入长度为512 bit的整数倍,这是步骤1将长度填充至L的原因。

步骤3SHA256输出的初始化。使用一个256 bit的寄存器存放散列函数的初始化、中间和最后结果。初始化为前8个质数(2,3,5,7,11,13,17,19)的平方根的小数部分的前32位:

H0(0)=6a09e667,H1(0)=bb67ae85,

H2(0)=3c6ef372,H3(0)=a54f f53a,

H4(0)=510e527f,H5(0)=9b05688c,

H6(0)=1f 83d9ab,H7(0)=5be0cd19。

步骤4初始化常量数组ki。k0~k63分别取自前64个质数(2~311)立方根小数部分的前32位。

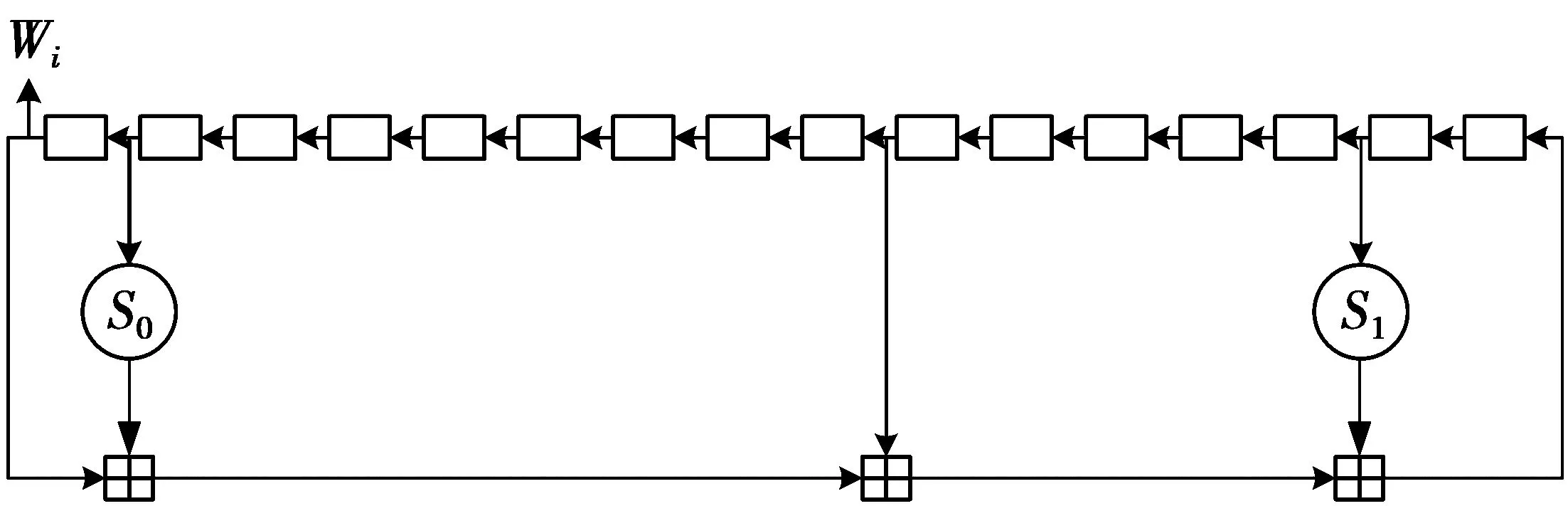

步骤5计算数组Wi,如图1。W0~W15由512 bit的输入块由高位到低位依次分解成16个32 bit得到。W16~W63计算公式

Wi=Wi-16+Wi-7+S0+S1

(1)

S0=(Wi-15ROR7)⊕(Wi-15ROR18)⊕

(Wi-15SHR3)

(2)

S1=(Wi-2ROR17)⊕(Wi-2ROR19)⊕

(Wi-2SHR10)

(3)

步骤6执行压缩函数,更新变量a,b,…,h更新次数64次。如图2。公式如下

h=g,g=f,f=e,e=d+T1

d=c,c=b,b=a,a=T1+T2

(4)

(4)式中,

T1=h+Σ1+ch+ki+wi

T2=Σ0+maj

(5)

(5)式中,

Σ1=(eROR6)⊕(eROR11)⊕(eROR25)

(6)

(7)

Σ0=(aROR2)⊕(aROR13)⊕(aROR22)

(8)

maj=(a&b)⊕(a&c)⊕(b&c)

(9)

a,b,…,h的更新如下

(10)

(10)式中,j表示第j个512 bit的输入块。

(11)

散列输出为

H=H0|H1|H2|H3|H4|H5|H6|H7

(12)

图1 数组Wi计算框图

图2 变量a,b,…,h更新框图

2 身份认证算法

在密码学中,散列消息认证码(keyed-hash message authentication code,HMAC)是涉及密码散列函数和秘密密钥的特定类型的消息认证码。与其他消息认证码一样,可用于验证数据完整性和消息认证。HMAC的加密强度取决于底层散列函数的密码强度,散列输出的大小以及密钥的大小和质量[8]。HMAC的计算可使用多种散列函数,如SHA1,SHA256,将这样的算法以HMAC-X的方式命名,其中,X是所使用的散列函数。HMAC的公式定义为

HMAC(m,k)=H(k⊕opad|H(k⊕ipad|m))

(13)

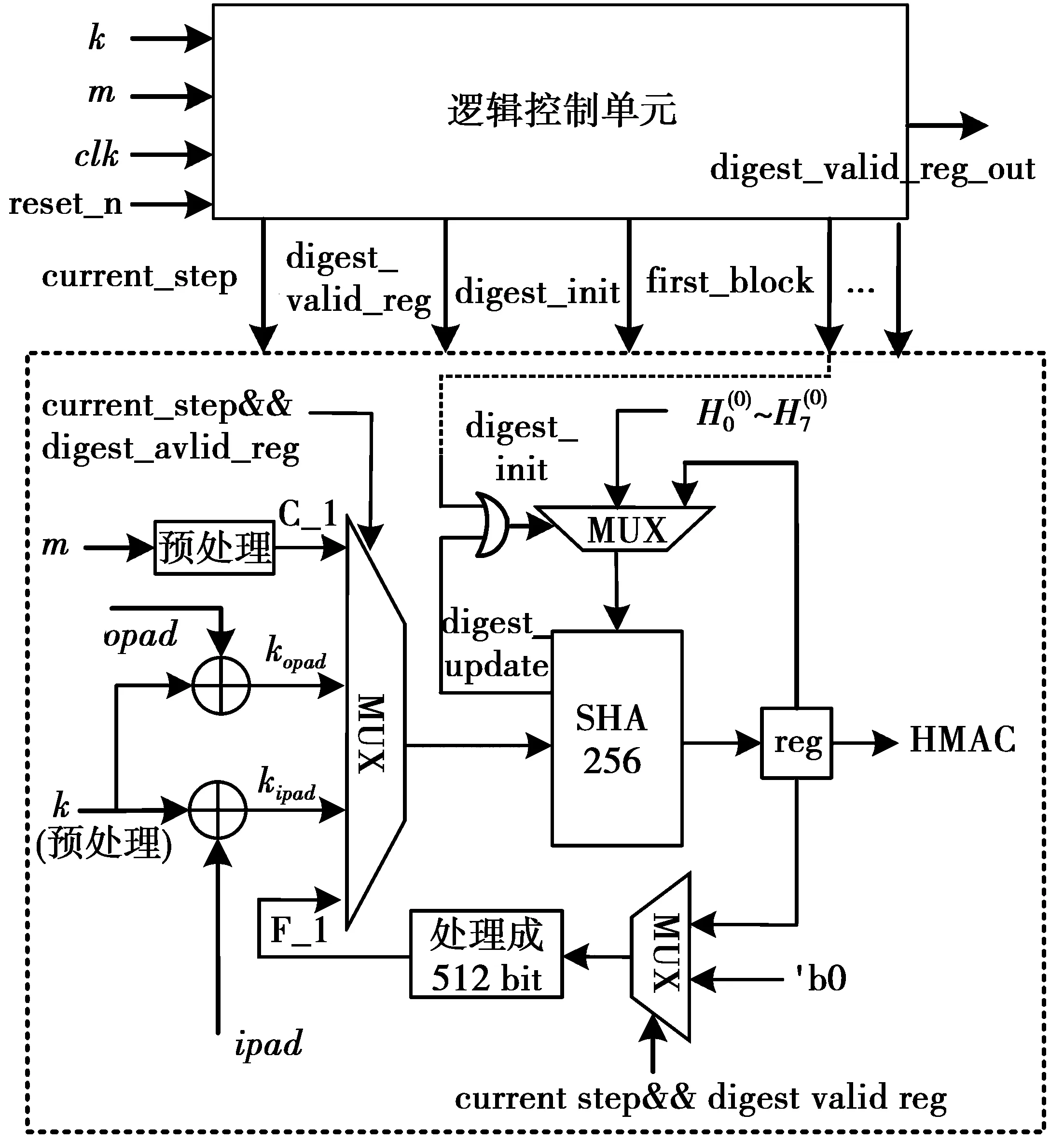

(13)式中:m为输入,k为秘钥,opad和ipad分别为重复的0x5c5c…和0x3636…构成的512 bit常量序列,H为散列函数,本文中选择的是SHA256。HMAC-SHA256实现结构图如图3。

图3 HMAC-SHA256实现结构图

HMAC-SHA256算法步骤如下。

步骤1在k后附加‘0’扩展成512 bit的序列。

步骤2将步骤1处理后的字符串与ipad做异或操作。

步骤3将m拼接到步骤2的字符串后,作为第一次SHA256的输入(需要对输入进行处理成512 bit的整数倍),得到256 bit的输出。

步骤4将步骤1处理后的字符串与opad做异或操作。

步骤5将步骤3的结果拼接在步骤4的序列后,作为第2次SHA256的输入(需要对输入进行处理成512 bit的整数倍),得到256 bit的输出。

3 FPGA设计与验证

在上面算法介绍中,可以看到HMAC-SHA256使用了2次HASH运算。通过对输入的预处理后,2次SHA256运算的最终输入都为1 024 bit的数据,通过将预处理后的数据分成块,得到4个512 bit的小块,对此采用了pipeline的处理方式,使得每一个块可以并行的处理。该算法的FPGA设计系统框图如图4。根据算法的实现结构,可以确定如下几个设计模块:预处理模块,SHA256算法处理模块,逻辑控制模块。本文全局系统时钟(clk)为50 MHz,时钟为上升沿触发。

图4 HMAC-SHA256系统框图

3.1 预处理模块

预处理模块包括对秘钥k的处理和输入消息m的填充。根据HMAC算法标准,密钥在使用前先要附加‘0’扩展成512 bit的序列,并分别和opad和ipad进行异或运算得到kipad和kopad,再作为SHA256的输入块。对输入消息m的填充是使得填充后的m的长度为512 bit的整数倍。在本文中,使用的m的长度为64 bit。填充后的m长度为512 bit,作为SHA256的输入块。

3.2 SHA256算法处理模块

SHA256算法的整体实现框架如图5。主要包括数组W模块、常数k模块、SHA256的核心压缩算法以及一个有限状态机FSM。

1)数组W模块。因使用过的Wi值不再参与后面的计算,所以可以通过复用16个32 bit位宽的寄存器来储存W当前参与运算的值和W接下来要参与运算的值的方式,减小使用面积。W0~W15由512 bit的输入分成16个32 bit得到,剩余的W16~W63由右移、循环右移以及异或运算得到,每一步运算的数据主要通过移位的方式存储在寄存器中。因W16~W63的计算时间小于SHA256的运算时间,所以复用这16个寄存器对最高时钟频率不会产生影响。本模块有一个更新W寄存器的状态机,其中有IDLE和update 2个状态。init=1时,进入IDLE状态,next=1进入update状态(与有限状态机FSM同步进入初始状态和更新状态,以使得W模块和k模块更新同步)。此状态下创建一个对W寄存器更新进行计数的计数器w_ctr_reg,每个clk寄存器更新一次,w_ctr_reg自加1。当计数器计数到63时,进入IDLE状态。

图5 SHA-256算法的整体实现

2)常数k模块。使用组合逻辑,只有一个输入addr和一个输出k。当输入为0~63时,输出分别对应常数K0~K63。

3)SHA256核心压缩算法。采用组合逻辑电路设计。从(4)式可知,最长路径为a=T1+T2,对T1和T2的求解按模块分级,从而缩短了整体的关键路径。变量a~h当前值和更新值,H0~H7当前值和更新值寄存在32个32 bit的寄存器。寄存器分别是a_reg~h_reg、a_new~h_new、H0_reg~H7_reg、H0_new~H7_new。复位时候,给寄存器赋初值。当digest_init==1,H0(0)~H7(0)赋值给H0_new~H7_new。变量a~h一个clk更新一次,更新64次则完成前一个512 bit块的计算。此时,digest_update==1, 执行(11)式的计算,将当前寄存器存储的值与开始参与运算的散列值相加。当(state_init && first_block)==1,H0(0)~H7(0)赋给a_new~h_new。当(state_init && !first_block)==1,将第一个块的输出H0_reg~H7_reg赋值给a_new~h_new。当state_update==1,执行(4)式的运算。

4)有限状态机FSM。有3个状态,分别是初始状态IDLE、寄存器更新状态ROUND以及寄存器更新完成状态DONE。系统复位时为IDLE状态,init=1,next=0,一个clk后会进入到ROUND状态,此时init=0,next=1,此状态下创建一个对k寄存器更新进行计数的计数器c_ctr_reg,每个clk寄存器更新一次,c_ctr_reg自加1。将c_ctr_reg与addr相连,而w_ctr_reg与c_ctr_reg 2个计数器是同步且计数值相等,从而满足(5)式的T1计算要求。当计数器计数到63时,FSM进入DONE状态,digest_update==1,digest_valid_reg==1,表示此次输入的数据块更新完成。

最终输出为256 bit的摘要digest。

3.3 逻辑控制模块

在本模块中,参见图4,主要有一个4选1路选择器和2个2选1路选择器,以及一系列的逻辑控制信号,其中,主要的current_step && digest_valid_reg和digest_init || digest_update为多路选择器控制信号。

current_step==0 && !digest_valid_reg对应选择kipad。current_step==0 && digest_valid_reg对应选择C_1。同时在2选1多路器中选择本次SHA256的输出,处理成512 bit作为4选1多路器的另一输入F_1。current_step==1 && digest_valid_reg对应选择kopad。current_step==2 && digest_valid_reg对应选择F_1。在第一次SHA256运算中,计算前一个512 bit输入块时,会产生一个脉冲标志位first_block。同样在第二次SHA256运算中,计算前一个512 bit输入块也会产生脉冲标志位first_block,first_block与digest_init连接。digest_init==1,SHA256输出寄存器初始化为H0(0)~H7(0),digest_update==1, 对应选择SHA256的输入为kipad或kopad时的输出。当输出计算结果HMAC(m,k)时,将digest_valid_reg_out信号拉高。

4 仿真和综合

仿真结果如图6,使用的2个输入取自文献RFC4868[9]。输入的“挑战”m为64′h4869205468657265,秘钥k为256′h0b0b0b0b0b0b0b0b0b0b0b0b0b0b0b0b0b0b0b0b0b0b0b0b0b0b0b0b0b0b0b0b,Response预设值为256′h198a607eb44bfbc69903a0f1cf2bbdc5ba0aa3f3d9ae3c1c7a3b1696a0b68cf7,输出“应答”为256′h198a607eb44bfbc69903a0f1cf2bbdc5ba0aa3f3d9ae3c1c7a3b1696a0b68cf7。此后,通过取文献RFC4868提供的多组输入和输出。对计算结果进行对比,通过对比验证,功能正确。

验证是将64 bit的k和256 bit的Response预设值存储到ROM中,单口RAM对m和HMAC的输出“应答”进行缓存,数据的发送和接收通过RS232串口实现。吞吐率为512/64×161.08/2=664.32 Mbit/s。电路实现结果如表1,同时与文献[10]进行比较。

表1 HMAC-SHA256实现结果比较

图6 HMAC_SHA256仿真结果图

5 结 论

本文运用Challenge/Response身份认证的机制应用在BAN的认证领域,完成了该认证所使用SHA256散列函数的HMAC的电路设计和验证。涉及主要设计思想有,串/并转换和pipeline设计,从而一定程度上提高了系统频率。在ED2-115器件上对设计进行综合验证。得到了0.08 mW的功耗、0.95 ms的延时,0.05 mm2消耗面积,所提出的方案具有低功耗、时延小、小面积、性能稳定等优点。