二次集成的高压驱动电路的研制

2019-11-27邢变丽

邢变丽

(陕西华经微电子股份有限公司,陕西 西安 710065)

0 引 言

该驱动电路应用于某整机产品。整机系统中,驱动电路和与之配合的整机外围电路、起转线包一起驱动陀螺转子,并使陀螺转子在3 s内达到预定转速。厚膜混合集成电路采用丝网印刷方法,把各种电子浆料通过漏印网板印刷在陶瓷基板上,经过烧结、阻值激光修调等工序,制成具有预定电性能的膜式厚膜芯板。电容采用贴焊组装,半导体芯片采用专用工艺进行金丝键合微组装,形成具有一定电路功能的混合集成电路,并按照GJB2438A-2002要求,严格进行一系列筛选试验,使产品具有很高的稳定性和可靠性。厚膜电路的主要工艺有成膜工艺、微组装工艺和封装工艺。成膜工艺中,需控制的主要参数有膜层质量、三维布线密度、膜式元件参数的离散性和可调整性、半导体芯片的一致性。设计中主要控制元件装配密度、连接可靠性、电性能功能调整性以及装配工艺通用性。

1 二次集成的必要性

1.1 厚膜混合集成,能够有效保证电路所用元器件的管芯原有可靠性水平

半导体管芯本身可靠性级别很高,平均无故障时间106~109h。但是,在三极管管芯进行塑封的过程中,经过几道加工工序,尤其是塑封件封装,可靠性大幅度降低,可以保证的平均无故障时间只能达到104h。厚膜电路采用芯片微组装,消除了封装过程对元器件可靠性的影响,也消除了具体封装形式对元器件管芯原有可靠性水平的束缚。

1.2 散装电路的厚膜集成是整机产品一致性、标准化批产的需求

散装电路的装配、维修和更换,需要操作和控制的元器件及其参数数量大,电连接焊点多,复杂程度高。它的电路调试需要操作到各个元器件及其具体参数。由于操作人员水平、责任、素质等影响,很难使元件级的参数达到较高的一致性和稳定性。厚膜电路采用统一工艺,全过程质量控制,大量专业标准设备进行加工组装,电路工艺和参数一致性好、稳定性高。大量元件集成为一个标准器件,方便整机装配、调试、维修和更换,提高了整机产品批产的一致性和标准化。

1.3 厚膜集成化是整机缩小体积、降低重量的有效途径

散装电路板所用的元器件都是已封装的元器件,体积比内芯大得多。以三极管为例,半导体三极管管芯体积本身只有1 mm×1 mm×0.1 mm,重量毫克级,几乎可以忽略。封装完成后成为TO-220结构,体积增大到10 mm×15 mm×4.5 mm,而且不计算引脚长的引线,体积增大了6 750倍,重量增加千倍。厚膜集成电路直接使用管芯组装,电阻及导带采用厚膜平面印刷烧结工艺,大幅度降低了产品体积和重量,有利于整机微型化。

1.4 厚膜集成化是整机提高电磁兼容性和热稳定性的有效途径

散装电路板所用的元器件都暴露在外,处理不当易产生电磁干扰,也易受到其他电路的干扰。电路板的各个元件本身参数有异,且根据位置不同,功率元件各自独立。功率工作元件发热升温,与非功率工作元件的温差很大,易产生更大的参数不对称。PCB板热传导性差,热点孤立,往往形成发热正反馈,发热件越来越热,直至烧毁,难以保障整个电路的热稳定性。厚膜电路采用金属封装,热稳定性好,具有更优的电磁兼容特性。

综上所述,厚膜混合集成电路具有优越的安全性、稳定性和可靠性,是军工单位提升整机产品质量、提高可靠性水平的有效措施。

2 产品描述和分析

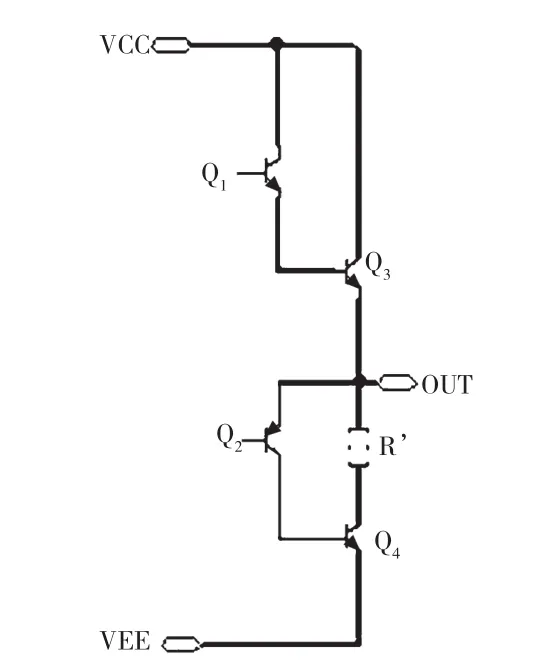

主要的技术指标如下:电源电压+20 V,-20 V;输入方波信号±20 V/100 Hz;输出方波的高、低电平电压的绝对值≥17 V;输出方波的上升、下降时间≤230 μs;带载能力≥3 A;工作温度为-55~+125 ℃。该产品属于厚膜混合集成电路,交付用户后还需要二次组装。集成电路能配合外围电路和起转线包一起驱动陀螺转子正常起转,并且在3 s内使陀螺达到预定转速[1]。电路原理图如图1所示。

驱动电路采用成熟的厚膜混合集成工艺技术,产品在军标线上生产,生产线获得QML认证;产品质量严格按GJB2438A-2002《混合集成电路通用规范》和《质量保证大纲》要求进行控制;产品采用双列直插金属外壳,平行缝焊封装。根据功率电路及工艺要求考虑,引脚从底座两侧面引出;壳体材料使用可伐材料,封装后可获得优良的气密性;壳体表面镀镍,增强对环境的适应能性;腔体式结构有助于防止组装过程中对电路造成损伤。驱动电路在使用时可根据实际输出功率外接适当的散热器,确保产品工作时外壳最高温度不超过105 ℃。如图1所示,驱动电路的工作原理是VIN1和VIN2输入反向调制方波,此时功率三极管Q3、Q4与Q7、Q8分别导通,OUT1、OUT2分别输出相应的调制方波,驱动外围负载工作。驱动电路的控制电路由两部分组成。在版图设计方面,为减少对两部分电路的影响差异和散热要求,产品平面布图采用较为对称的布图方式。在热分布设计上,通过大电流的区域采用导带覆铜设计,降低热损耗,提高可靠性[2]。

图1 电路原理图

3 产品工艺

3.1 主要工序简述

3.1.1 成 膜

通过丝网印刷、烘干、烧结以及激光修调等技术,在陶瓷基板上制做厚膜互连线和厚膜电阻。

3.1.2 粘 接

将裸芯片用导电胶粘接到厚膜芯片上,按图纸位置放置于粘结剂上。需要注意,粘结剂不能翻上管芯表面,不能对管芯造成任何污染。

3.1.3 键 合

金丝球焊或超声压焊将金丝或硅铝丝键合到器件及厚膜导体上,实现电路互连。常用的压焊金丝直径为25 μm,硅铝丝直径为100 μm。

3.1.4 封 装

封装是通过平行缝焊技术实现产品的密封封装,满足GJB2438的要求。

3.1.5 筛 选

产品按照H级军用厚膜混合集成电路的筛选工序,可有效剔除早期失效产品,并鉴别批产品质量。

3.2 可靠性预计

根据GJB/Z 299C-2006《国家军用标准电子设备可靠性预计手册》,对产品的可靠性进行理论计算和预计,预计该产品平均故障间隔时间为2.36×105h。

4 研制过程

4.1 样品研制情况

该产品的协议签订后,随即进行了方案设计、方案论证以及方案评审,并做了大量相关的基础实验。用户及时提供了相关技术细节要求和使用环境的详细资料,并在相关技术如驱动负载、控制程序、电路工作外围环境、体积要求等技术方面给予充分说明,积极配合,全力支持,推进了研制进度。3次向用户提供产品样品,分别解决了产品的启动问题、大电流驱动问题以及热功耗问题。最终,第3次样品完全达到了协议的技术指标,满足了使用要求。

4.2 技术难点和解决

技术难点是启动瞬间的大电流驱动问题。

4.2.1 问题发现

给客户送去6只样品,检测加电时有一只损坏。开壳后测量发现,功率晶体管Q3、Q4损坏,损坏部位是Q3的be结、Q4的be结和ce结。问题所在驱动电路主功率回路如图2所示。

4.2.2 分析及结论

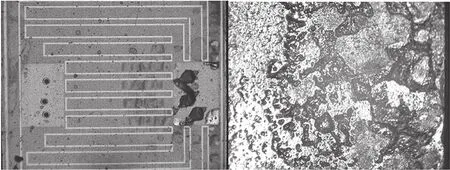

Q3和Q4都是大功率管,IC电流最大可达到7 A。芯片组装采取再流焊工艺,即将功率管的c极通过再流焊与基片上的焊盘相连,b极和e极通过压焊连线和内部厚膜导带连接。通过100倍显微镜下观察、分析,发现功率管Q4击穿在先,随后导致Q3损坏。损坏芯片显微照如图3所示。

主功率回路包括厚膜导带、压焊丝、功率管芯片和再流焊焊锡层4个环节。经过分析和试验,得到以下结论:(1)功率管芯片压焊部位缺损性烧毁,说明试验中电流很大,很可能达到功率管的极限电流;(2)主功率回路上,再流焊焊锡层等效电阻是关键因素,需要进一步改进。再流焊焊锡层应均匀、薄而紧密且无气隙,等效电阻(R')极小,否则VR压降增大,导致大电流不再大部流过Q4,而是经过处于饱和状态的Q2的ce结到Q4的be结进入Q4的发射极,使Q4的be结烧毁。Q3亦然。

图2 主功率回路(R'为等效电阻 )

图3 100倍显微镜下损坏芯片显微照(正反面)

4.2.3 解决措施

针对这个因素进行工艺细节改进,微调产品版图,改进并细化再流焊工艺,形成了无空隙再流焊工艺。产品中的大功率管发热量大,必须保证再流焊焊锡层应均匀、薄而紧密且无气隙,因此需要X射线照相。内部导带、压焊连线以及再流焊的电流容量达到7~10 A水平,确保了启动和工作电流容量的要求。

5 产品的特点

驱动电路产品具有驱动能力强、响应速度快、体积小、重量轻和可靠性高等特点。产品采用厚膜混合集成工艺技术和微芯片键合互连组装工艺,充分保证了芯片的原有可靠性参数,达到了国内领先水平。

6 结 论

驱动电路产品经过用户检测和试用,各项技术性能指标满足使用要求,目前已批量生产应用。