4 Bit 100MS/s的两步式模数转换器设计

2019-11-20魏一方田鑫沈福良周柯港

魏一方 田鑫 沈福良 周柯港

【摘 要】在科技发展迅速的社会,电子产品越来越多,数字信号的优势在计算机、无线通讯、医疗等领域体现得越来越明显。而模拟信号到数字信号的转变成了各个领域研究的焦点,随之产生了各种形式的数模转换器(Analog-to-Digital Converter)。论文设计了一个4bit 100MS/s的两步式模数转换器(Two-Step ADC),运用底极板采样、格雷码转换、D-触发器延时等技术设计减法电路、逻辑组选择等电路。元件采用65nm CMOS工艺,当输入信号频率为100MHz时,输出信号噪声失真比(SNDR)为24.55dB。

【Abstract】In the society with the rapid development of science and technology, more and more electronic products are produced, and the advantages of digital signals are more and more obvious in the fields of computer, wireless communication and medical treatment. The conversion from analog signal to digital signal has become the focus of research in various fields, with the emergence of various forms of the analog-to-digital converter (ADC). In this paper, a 4 bit 100MS/s two-step analog-to-digital converter(Two-Step ADC) is designed. The subtraction circuit and logic group selection circuit are designed by using the techniques of bottom plate sampling, Gray code conversion and D flip-flop delay. The component adopts 65 nm CMOS technology. When the input signal frequency is 100 MHz, the output signal noise distortion ratio (SNDR) is 24.55 dB.

【關键词】Two-Step ADC;底极板采样电路;格雷码;子ADC;减法器电路

【Keywords】Two-Step ADC; bottom-plate sampling circuit; Gray code; sub-ADC; subtractor circuit

【中图分类号】TN79+2 【文献标志码】A 【文章编号】1673-1069(2019)09-0164-02

1 工作原理

两步式模数转换器(Two-Step ADC)[1]的整体结构是两个子ADC的串联结构,假设两个子ADC的有效位数分别为N1、N2,则总共需要的比较器为2N1+2N2-2,而相同位数Flash ADC需要2N1+2N2-1个比较器,相对而言数目大为减少。输入信号通过底极板采样电路采样后保持稳定,把信号传给第一级子ADC进行比较,输出的温度计码通过编码电路转换成位二进制码,二进制码通过逻辑选择电路和DAC电路控制减法电路,确保在保持周期内对稳定的保持信号进行减法操作,把减去的信号输送到第二级ADC进行位解码。需要延时系统把第一级子ADC的结果保持到第二级子ADC的工作时间。最后通过D-触发器延时第一级子ADC的二进制码和第二级ADC二级制码组合输出。

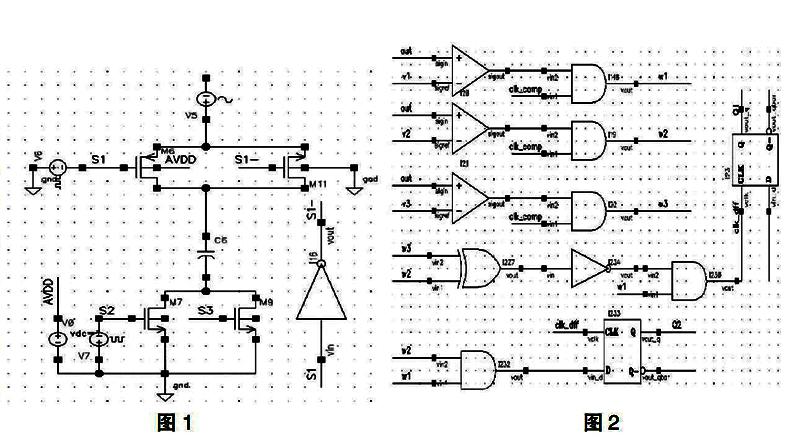

2 采样/保持电路(S/H)

采样/保持电路是整个ADC最前面的电路,负责把模拟信号采入,由于开关的电荷注入效应,单MOS采样/保持电路很难达到较高的性能,所以本文中采用PMOS和NMOS并联结构。为解决开关的电荷注入效应,可以采用底极板采样技术。底极板采样技术(bottom-plate sampling)指利用开关的导通时间,使电荷注入与输入信号无关,其中涉及控制开关开断则是利用了non-overlap clock技术[2]。电路如图1所示。

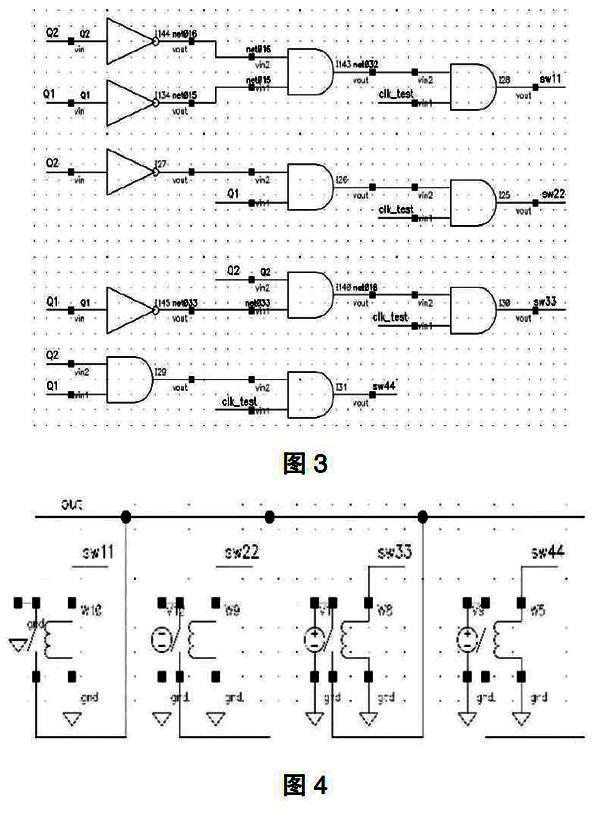

3 子模数转换器(子ADC)

量化电路分为两个部分,比较器和转码器。就比较器而言,多个比较器可以组成得到温度计码,而由于温度计码不能输入DAC做减法,也无法控制减法器的开关,所以需要把温度计码输入编码电路中转换为二进制码。编码电路由组合逻辑电路组成,如图2所示。编码过程中,比较器的输入电压和基准电压相差比较小时,会使比较器出现亚稳态状态[3],从而产生数字失真,此问题可以用格雷码解决。

4 选择减法电路

选择减法电路包括开关选择电路和减法电路。开关选择器如图3所示,其作用是用逻辑组合电路判断第一级子ADC的输出结果,不同的精度要选择不同的减法电路,以4 bit为例,减法器如图4所示,其基准电压由一组DAC确定,分别确定电压为-0.25V、-0.5V和-0.75V。

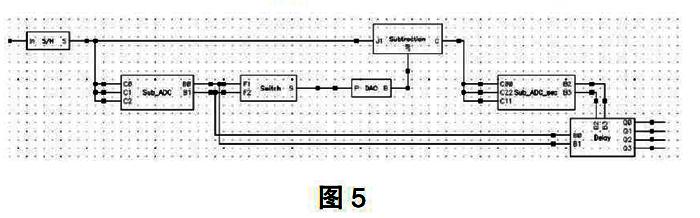

5 电路结构

把采样保持电路(S/H)、子模数转换器(Sub-ADC)、选择器(Switch)、减法器(Subtraction)模块化以后其总的电路结构如图5所示,延时器(Delay)由一组D-触发器组成。

6 仿真结果

在4 bit ADC的之后加上一个D-触发器可以消除前一级子ADC的变化对后一级的影响,在输出连接一个理想DAC后可以判断ADC的SNDR。其输入输出波形如图6所示。从图7可以看出,在输入频率是100MHz时SNDR为24.5540dB。接近于理想值。

7 结论

本文在65nm CMOS工艺基础上,设计了一个4 bit Two-Step ADC,在100Mhz的工作频率下仿真出来的SNDR≈24.5540dB,接近于理想值。在量化过程中运用了少量的比较器,并且把两级ADC的工作时间分开,所以在功耗和精度方面表现优异。

【参考文献】

【1】Shu Y S , Song B S . A 15-bit Linear 20-MS/s Pipelined ADC Digitally Calibrated With Signal-Dependent Dithering[J]. IEEE Journal of Solid-State Circuits,2008,43(2):0-350.

【2】Marques A, Peluso V, Steyaert M, et al. A 15-bit 2 MHz Nyquist rate Δ Σ ADC in a 1 μm CMOS technology[C]//European Solid-state Circuits Conference.1997.

【3】Kang J J, Flynn M P. A 12b 11MS/s successive approximation ADC with two comparators in 0.13μm CMOS[C]//Symposium on Vlsi Circuits.2009.