硅通孔转接板关键工艺技术研究

——TSV成孔及其填充技术

2019-11-14刘晓阳陈文录

刘晓阳 陈文录

(江苏无锡35信箱,214083)

0 引言

随着电子产品向小型化、高性能、高可靠等方向发展,系统集成度也日益提高。当前的中央处理器(CPU)芯片封装大都采用有机基板(载板)倒装(FC)封装形式,但随着芯片尺寸不断增大、凸点尺寸和节距的缩小导致热膨胀系数(CTE)兼容性问题无法避免,解决途径有两个方面:要么降低有机基板CTE以匹配芯片,要么采用缓冲层即通过转接板或称内插板(interposer)解决。降低有机基板的CTE是有局限的,因此利用转接板作为缓冲层是较佳的解决途径。采用硅通孔(TSV:Through Silicon Via)转接板进行的封装称为2.5D封装,2.5D封装的TSV转接板本身仅起互连作用,将有机基板与硅基TSV转接板互连再与芯片互连的堆叠结构称为2.5D封装。采用TSV转接板的2.5D封装与2D封装相比,有如下优势:

第一、转接板与芯片都属于硅基同质集成,材料性能相容性好;

第二、转接板通过再布线将芯片凸点节距放大,从而大大降低有机基板布线难度;

第三、转接板在芯片和有机基板之间形成缓冲,减少因形变对芯片的损伤;

第四、转接板的制造工艺与集成电路的再布线工艺兼容;

第五、硅基TSV转接板的制造及2.5D封装技术为实现3D集成奠定基础。

由于实现CPU与存储器3D集成仍然存在诸多技术瓶颈,采用TSV转接板的2.5D封装是实现3D集成封装的过渡解决方案,目前成为国内外研究焦点之一,TSV转接板的典型结构示意图(如图1)。

图1 转接板典型结构示意图

TSV转接板结构设计与其工艺设计关系密切,作为转接板的TSV技术而言,与在有源器件上的Via First工艺类似,采取先刻蚀孔,再填充金属的工艺,本文所研究的金属是铜。设计这种工艺路线的关键点在于TSV成孔时的孔深均性和电镀均匀性控制,图2所示为本文设计并优化的典型TSV转接板的制造工艺流程(如图2)。

从图2中可以看出在TSV转接板的制造工艺中存在许多技术难题,包括:TSV形成、高深宽比孔电镀、圆片减薄、化学机械抛光(CMP)、薄片拿持、布线层的制作等等[1][2]。

本文转接板TSV孔径小于50 μm,高度为200 μm,主要针对TSV成孔及其填充技术进行研究。

1 TSV成孔及其填充工艺设计及解决路线

TSV深孔刻蚀、绝缘层沉积、扩散阻挡层和种子层沉积、深孔电镀填充及其表面平坦化工艺等均为TSV形成必要的过程,关键点在于高深宽比的深孔刻蚀及其填孔工艺,本文通过工艺优化,要解决6:1以上深宽比的深孔刻蚀及其填孔工艺。解决方案如下:

(1)高深宽比TSV深孔刻蚀工艺:深反应离子体刻蚀(DRIE)工艺和激光钻孔均可以在硅衬底上制作深孔,本文采用优化的Bosch刻蚀工艺,利用其刻蚀速率快、各向异性刻蚀深宽比高的特点,优化刻蚀速率以获得优质的TSV孔;

图2 TSV转接板工艺流程图

(2)TSV侧壁绝缘层制备工艺:由于硅衬底是半导体材料,所以必须在硅衬底与铜TSV之间制作绝缘层,TSV深孔内的侧壁绝缘层一般使用SiO2,与原位生长的方法不同,为了获得均一、致密的SiO2,本文采用PECVD(Plasma enhanced chemical vapor deposition等离子增强化学汽相沉积)的方法来获得致密的绝缘层,保证绝缘的可靠;

(3)扩散阻挡层、种子层沉积:为了阻挡铜离子向硅衬底中扩散,需要沉积一层Ti作为阻挡层,再沉积一层铜作为种子层,为下一步电镀填充通孔的进行做准备。沉积种子层的质量,转接影响电镀填孔的质量,特别是种子层的均匀性和覆盖率,将直接影响填孔电镀时的电流密度分布;

(4)TSV深孔电镀填充工艺:为了均匀填充TSV深孔,需要采用由底向上(Bottom-up)的电镀方法,而高深宽比的TSV深孔,电镀药液很难渗透到孔底部,更难以发生溶液交换从而形成良好填充,除了需要采用特殊的电镀加速剂和抑制剂,还必须控制好电流、浓度、温度等电镀参数,须要队所有因素、参数进行一系列优化匹配。借助仿真工具,将理论与实验进行反复验证结合,从而得出优化的电镀参数;

(5)CMP(Chemical Mechanical Polishing)平坦化工艺:电镀填孔过程中,衬底表面也会沉积上铜,这层铜必须去除掉,单纯采用化学方法会使填孔的铜同时被除去,采用机械方法可能会损伤衬底,因此,采用化学和机械相结合的方法,将二者取长补短。

2 TSV成孔及其填充制造工艺

TSV制造工艺与传统的CMOS(Complementary Metal Oxide Semiconductor互补型金属氧化半导体)、BJT(Bipolar Junction Transistor双极结晶体管)等主流的半导体表面器件的制作工艺不完全兼容,需要对高深宽比的TSV刻蚀工艺、高台阶覆盖率的绝缘层淀积工艺和粘附种子层沉积工艺、高深宽比TSV的无缝填充技术等进行研究。

2.1 TSV蚀刻工艺

TSV刻蚀将形成高深宽比的盲孔结构,其形貌、尺寸及侧壁粗糙程度都将对后续工艺产生影响。当前,业界采用Bosch工艺技术来获得高深宽比的盲孔。本文基于2.5D转接板对工艺集成的要求,对深硅刻蚀工艺进行优化和再开发,研究了低成本、高质量的TSV深硅刻蚀解决方案。

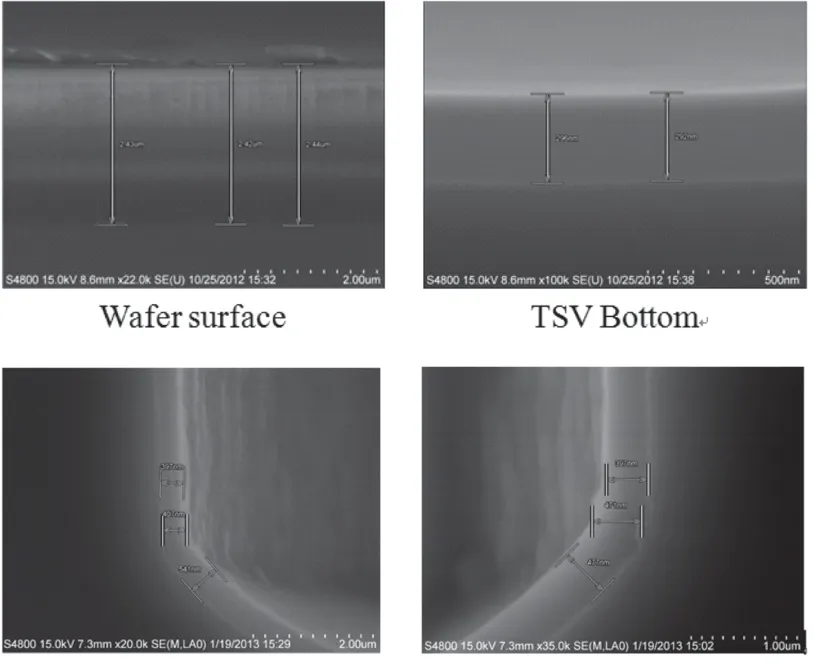

采用Bosch刻蚀工艺进行TSV刻蚀,最终光刻和刻蚀的关键尺寸偏差1 μm以内,最高深宽比可以接近10:1。从图3TSV孔的SEM图片数据可以看出,样品最高深宽比达到9:1,孔径偏差控制在10%以内,而刻蚀的侧壁棱线深度0.28 μm,刻蚀孔的深度整体均匀性很好(如图3)。

图3 利用Bosch刻蚀工艺完成的TSV形貌

Bosch刻蚀工艺利用C4F8反应产生聚合物进行侧壁保护,从而实现高深宽比的盲孔结构,这些非挥发性的聚合物在保护侧壁的同时也会做为刻蚀残留物存在于晶圆表面和TSV孔内。由于刻蚀反应腔室内环境复杂,刻蚀工艺时间长,刻蚀过程产生的聚合物还可能和光刻胶混合,形成更为顽固的残留物,随着TSV深宽比的提高,对TSV清洗工艺提出了更加苛刻的要求。在TSV清洗工艺研究过程中,开展了基于兆声波工艺的高深宽比TSV清洗技术研究,利用高频的兆声波改善清洗药液在TSV孔内的浓度分布,并利用兆声波能量对残留物进行物理清洗[3]。

本文所需6:1 TSV 刻蚀工艺刻蚀后贝壳状锯齿小于80nm,刻蚀后对TSV清洗工艺进行优化,调整兆声波频率、能力及温度,清洗后未发现残留物(如图4)。

图4 兆声波清洗后TSV孔内未见异常

2.2 绝缘层淀积

在导电材料填充之前,为了实现TSV与衬底的隔离,需要首先在侧壁生长绝缘层、扩散阻挡层及粘附层等材料。绝缘层主要选择氧化硅材料,可以使用原位热氧化或者等离子增强化学汽相淀积(PECVD)等工艺制作,具体选择需要根据基片的情况,看是否允许高温工艺。热氧化可以实现深孔的最好台阶覆盖,但需要使用上千度的高温,这在很多后道工艺中是不允许的。PECVD作为绝缘层淀积方式,但要实现高深宽比结构的较好台阶覆盖,存在很大难度,最主要是沉积均匀性问题,本文通过优化沉积工艺参数,使用液体反应源(一般为TEOS:Si(OC2H5)4正硅酸乙酯),工艺温度将不超过400 ℃。

图5所示为绝缘层淀积采用PECVD工艺,深宽比为6:1的 TSV孔,绝缘层台阶覆盖率约为16.7%,最薄弱点SiO2厚度为200 nm(如图5)。

图5 TSV绝缘层淀积效果

2.3 阻挡层和种子层工艺

采用铜作为填充导体进行TSV填充,在绝缘层制作完成之后,还需要制作扩散阻挡层、粘附层以及电镀种子层。TSV电镀阻挡层肩负着阻挡铜向转接板衬底硅中扩散和增加铜与硅之间粘附性的双重任务。阻挡层工艺的好坏除了直接影响种子层粘附效果,还会影响整个2.5D封装集成系统在使用中的性能稳定。

扩散阻挡层及粘附层主要使用Ti、TiN、Ta、TaN等材料,本文拟采用钛做为阻挡层材料,制作方式一般使用物理汽相淀积(PVD)的方式,为实现高深宽比结构的连续覆盖,一般需要使用离子化PVD设备。电镀种子层也是铜材料,是后续电镀的基础,需要对侧壁连续覆盖,同样需使用离子化PVD设备来实现。

由于PVD工艺本身的限制,在深宽比较大时,很难实现薄膜的连续覆盖,目前还使用湿法制作工艺,如化学镀、电接枝(ElectroGrafting)等技术,实现薄膜的低成本、高性能覆盖,但这些技术目前还不成熟,还需要进一步的研究和评估。本文通过改进PVD工艺,提高PVD的渗透能力,从而使其适用于较高深宽比的TSV孔种子层的沉积。

传统的PVD设备无法对高深宽比TSV孔内进行有效的淀积,本文提出了低成本的电镀阻挡层和种子层制备方案,主要基于对传统PVD设备的改善进,包括优化靶材及其气相成分比例、浓度,优化温度、压力等参数。6:1 TSV转接板采用Ti 500nm Cu 2 μm PVD沉积目标条件,经过FA检查及电镀工艺验证,TSV底部电镀和粘附效果良好(如图6)。

图6 TSV PVD种子层淀积效果SEM

2.4 TSV电镀及CMP工艺

电镀工艺是实现TSV填充,实现2.5D封装TSV转接板电流、信号通路的关键步骤,填充材料的选择和填充效果的好坏将直接影响TSV结构的电学性能和可靠性。本文采用电镀铜技术实现TSV的金属填充。电镀填充质量主要取决于镀液成分配比及工艺控制参数,本文结合数值仿真开展电镀工艺研究。研究TSV电镀的原位应力测试方法,探索镀层的应力产生和演变机理,通过设计应力传感器阵列,对TSV周围的应力分布进行实时测量,通过有限元仿真和理论反算,获得TSV孔内镀层应力[4]~[8]。

6:1 TSV电镀工艺均基于Ti 500 nm Cu2μm PVD条件下的种子层,分别采用EBARA和NEXX药水体系电镀。从图7结果显示两种药水体系均能实现高深径比的TSV填充,EBARA样品界面金相图片显示填充量为85%左右时,填充部分基本无空洞,NEXX样品俯视图显示电镀填充饱满。经过多次试验测试比对和良率统计,本文TSV样品电镀填孔采用EBARA药水体系(如图7)。

平坦化工艺主要是去除电镀后晶圆表面的铜并对TSV表面进行整平。目前,这一过程是通过使用抛光设备,经过抛光液的固体磨料机械磨削结合化学成分腐蚀实现。抛光机、抛光液和抛光垫构成CMP工艺的三大因素,其性能和相互匹配决定了CMP工艺能达到的表面平坦化水平。本文采用国产的高去除效率的铜抛光液,并结合TSV电镀后的退火工艺研究电镀面铜去除和平坦化工艺。

转接板TSV电镀后,采用第一次CMP工艺去除晶圆面铜,保证TSV与wafer表面的粗糙度和TSV表面铜的平整度,降低退火后二次CMP的工艺难度。电镀后晶圆表面铜层厚度约为3.6 μm,CMP工艺调试采用应用材料Mirror系列设备。采用A21和U3000两种浆料,采用相同的研磨参数,对表面粗糙度进行测试,U3000研磨后的粗糙度和平整度优于A21(如图8)。实验发现退火前后塑性形变不大,不大于1 μm,退火温度为350℃时,TSV二次塑性比较稳定。具体实验数据如图9。因此晶圆表面的铜层去除后对晶圆进行350 ℃退火处理,释放TSV铜柱的应力,减轻在后续工艺过程中TSV的塑性形变。第二次CMP对退火后TSV塑性形变引起的TSV台阶高度和TSV表面粗糙度进行修复,保证后续工艺质量(如图9)。

图7 电镀调试工艺结果

图8 CMP工艺后晶圆表面对比

图9 CMP后两次退火前后TSV涨出对比

3 小结

本文基于高性能CPU封装对转接板的要求制定了工艺集成方案,并根据工艺集成方案进行各单项工艺的开发,成功实现了高深宽比TSV刻蚀、绝缘层淀积(CVD)、粘附层种子层淀积(PVD)、TSV的无空洞填充等工艺,成功实现了TSV结构。