锁相环环路特性新型分析和优化方法研究

2019-10-18张堉萌阴亚东张利红

张堉萌,阴亚东,张利红

(1.福州大学 物理与信息工程学院,福州 350108;2.福建江夏学院 电子信息科学学院,福州 350108)

锁相环(Phase Locked Loop,PLL)是现代无线电子 系统中的核心部件,可实现纯净频率源、高频时钟恢复和频率调制解调等功能,广泛用于各种技术领域中[1-2]。虽然锁相环技术诞生已久且业界研究成果很多,但由于锁相环元部件众多且环路特性复杂,如何优化锁相环环路而使其在稳定性、锁定时间、相位噪声和杂散干扰等性能指标达到最佳仍然是当前锁相环研究的关键之一。

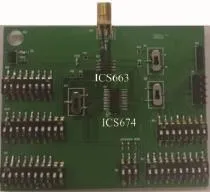

本文将首先对电荷泵Ⅱ型整数分频锁相环进行理论推导,将依次对稳定性、锁定时间和相位噪声杂散等进行分析,以获得锁相环环路的优化方法;进而,利用MATLAB仿真工具对分析结果加以建模仿真验证;最终基于锁相环芯片ICS663和分频器芯片ICS674完成一款锁相环电路的设计,进而测试不同环路参数下的锁定时间、相位噪声和杂散抑制等性能指标。最终的测试结果与理论分析结果相吻合,验证了理论分析的正确性。

1 锁相环环路特性的理论分析

1.1 稳定性优化分析

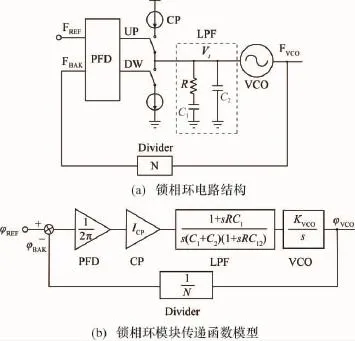

图1(a)所示为电荷泵型Ⅱ阶整数分频锁相环电路结构,其主要由鉴频鉴相器(Phase Frequency Detector,PFD),电荷泵(Charge Pump,CP),环路滤波器(Loop Filter,LPF),压控振荡器(Voltage-Controlled Oscillator,VCO)和分频器(Divider)等构成。锁相环以负反馈形式利用VCO输出信号FVCO经过分频产生的信号FBAK与输入参考信号FREF之间的相位比较结果,对FVCO进行频率调整而使 FBAK频率相位与FREF趋于一致从而进入锁定状态。当进入锁定状态时,锁相环输出信号FVCO频率fVCO=NfREF,其中N为分频器分频系数,fREF为FREF的频率,因此fREF决定了整数分频锁相环的最高频率分辨率。

图1 锁相环电路结构和传递函数模型

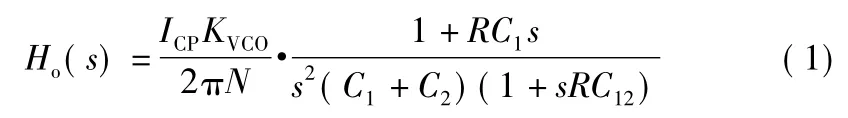

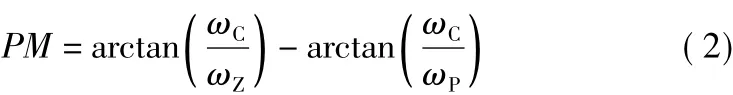

电荷泵型Ⅱ阶整数分频锁相环环路传递函数模型如图1(b)所示。其为典型3阶负反馈系统,因而可能存在稳定性问题。其环路开环传递函数表示为

式中,ICP/2π为PFD和电荷泵传递系数;KVCO为VCO的电压频率转化系数;C12=C1C2/(C1+C2)。从式(1)可以看到,PLL开环传递函数包含了一个零点ωZ=1/RC1和一个非零极点ωP=1/RC12。

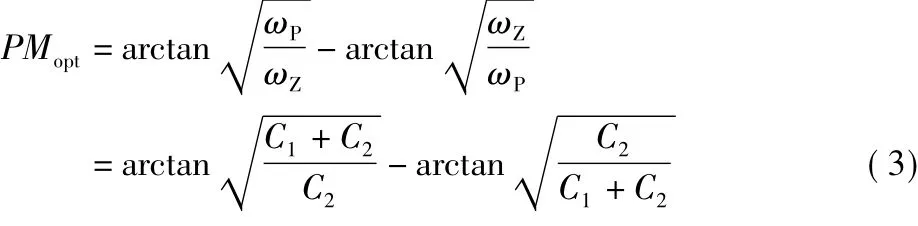

从稳定性角度出发,当使 Ho(s )为1时的截止频率ωC处于ωZ和ωP之间时,环路稳定与否关系密切。当ωC变化时相位裕度可表示为

分析式(2)可知,在零极点固定的情况下,当 ωC=

从式(3)可知,PMopt与LPF中的电容的比值有着密切关系。工程上一般取PMopt=60°能够获得较好的环路性能,可求得C1/C2≈13,此时环路滤波器参数为

1.2 锁定时间优化分析

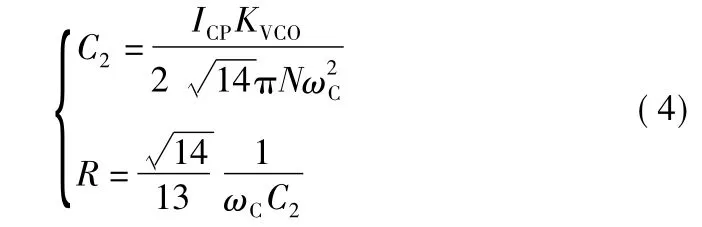

锁定时间(tlock)亦称为稳定时间,是反映PLL性能的重要指标。现有研究成果为简化分析过程视PLL整个锁定过程为线性变化过程,单纯地通过求解PLL闭环传递函数的阶跃响应而得到锁定时间[3-5]。当锁相环初始频率/相位差较小时,该模型能够较为精确地描述锁定时间,但初始频率/相位差较大时,其得到的锁定时间与实际情况之间存在较大误差。图2为相同环路参数下锁相环线性模型与考虑非线性特性的真实行为级模型两种情况下锁定时间对比。从图可知,单纯采用线性模型获得的锁定时间与实际情况存在明显误差。因此,有必要深入分析锁相环环路特性,提出更精确的环路锁定时间计算模型。

图2 线性模型和行为级模型的仿真锁定时间对比

通过研究发现,PLL锁定时间tlock可分为两个阶段:①当反馈信号FBAK与参考时钟FREF之间频率/相差较大时,PFD输出将饱和而驱使PLL进入非线性状态;②当误差小于一定范围时,PFD退出饱和状态,此时可近似认为PLL处于线性状态。因此,PLL锁定时间应分为两部分:

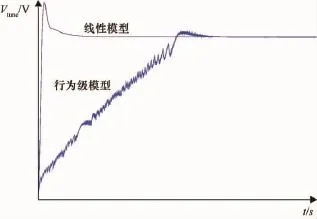

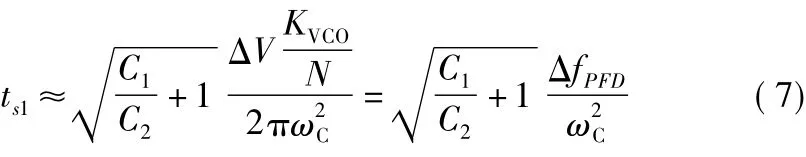

式中,ts1和ts2分别对应非线性和线性两个阶段所持续的时间。当PFD输出饱和时电荷泵将对LPF中的电容进行持续充电/放电,因此ts1可表示为

式中,ΔV为初始状态最终锁定状态下VCO控制电压之间的差值。在最佳环路相位裕度状态下即ωC=

式中,ΔfPFD为非线性阶段PFD输入端的初始频率误差。而线性状态下的锁定时间可表示为[1]

式中,ϵ为线性阶段PFD输入端初始相位误差。对比式(7)和式(8)可知,两种模型下锁定时间存在明显差异:非线性模型中锁定时间与ω2C成反比,而线性模型中锁定时间只与ωC成反比。

1.3 相位噪声与杂散优化分析

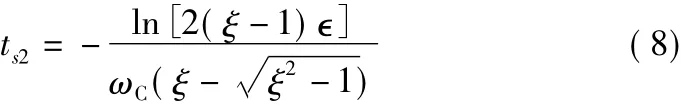

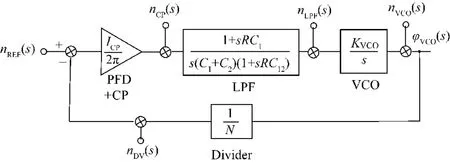

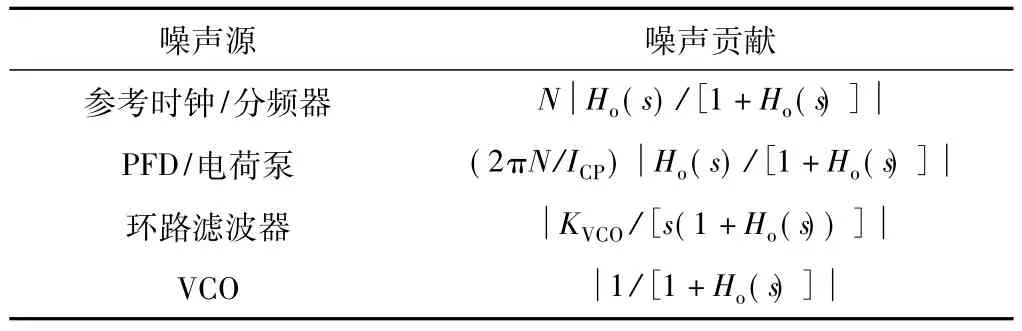

相位噪声是评价锁相环性能优劣的重要指标,因此考察锁相环环路对其输出相位噪声的影响至关紧要[6-9]。图3为PLL的相位噪声模型,其噪声来源包括了输入参考时钟相位噪声nREF(s)、电荷泵中电流噪声nCP(s)、环路滤波器中电压噪声nLPF(s)、压控振荡器相位噪声nVCO(s)和分频器相位噪声nDV(s)等5个部分,最终的输出总相位噪声为各噪声贡献之功率和。通过推导分析可得到PLL环路中各种噪声对总噪声的贡献如表1所示。从中可知,除VCO相位噪声在环路中呈现高通特性外,其他模块噪声均在环路中表现为低通特性。考虑到实际电路中VCO噪声往往起主导作用,因此需要尽可能地提高ωC来抑制VCO噪声从而改善PLL相位噪声指标。

图3 锁相环噪声模型

表1 各噪声贡献的函数表达

此外,由于PFD和电荷泵的失配等非理想特性,当环路锁定时PLL实际上将处于动态平衡状态,其电荷泵仍将进行周期性的充放电,从而使PLL输出中包含参考杂散(Reference Spur,RS)成分而恶化相位噪声指标。该杂散干扰可以看成在电荷泵输出电流上叠加了频率为参考时钟频率fREF的周期性冲击脉冲iSPR(t)。

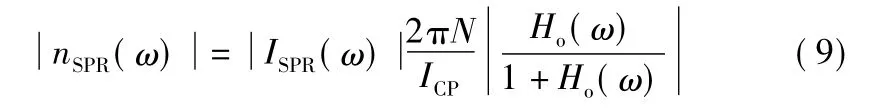

RS可视为PFD/电荷泵噪声而在环路中表现为低通特性。根据3阶锁相环环路特性,最终输出中杂散的噪声贡献可表示为

其中,ISPR(ω)为iSPR(t)的傅里叶变换频域变换形式。为抑制杂散干扰,通常杂散频率ωREF应当满足ωREF>>ωP>ωC[7-9]。则杂散对PLL输出的影响可表示为

虽然式(10)指出降低ωP/ωZ可降低杂散强度,但通常需要保持较高的ωP/ωZ,以确保环路具有较好的相位裕度。另一方面可知,杂散强度与ωC/ωREF项的平方成反比,降低ωC/ωREF可以有效地抑制杂散干扰。

综合以上分析可知,锁相环环路截止频率ωC对锁相环性能具有重要影响。从相位噪声指标出发,提高ωC可有效的抑制Ⅱ型锁相环中占主导的VCO噪声,同时迅速地缩短锁定时间;然而ωC的提高将严重削弱锁相环的杂散抑制能力。综合考虑,ωC≈(1/5~1/10)ωREF是较为合理的取值范围。

2 锁相环仿真验证

2.1 稳定性的仿真验证

基于MATLAB仿真平台,构建了锁相环开环和闭环模型,选取输入参考信号为100 kHz,分频比为200,则最终输出为20 MHz;同时根据芯片IC663指标选择了 ICP=2 μA,KVCO=2π ×200M rad/V;为使环路 ωC=2π ×2k rad·s-1,PM=60°,根据前文推导结果可计算滤波器参数为R=23 kΩ,C1=90 pF,C2=7 pF。将以上参数代入MATLAB锁相环模型中计算可知,其中ωC=12.5 krad/s,PM=60°,仿真结果与计算结果一致。

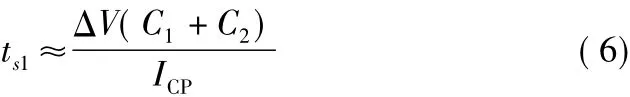

2.2 锁定时间与杂散的仿真验证

基于MATLAB构建了锁相环行为级电路模型,通过改变环路带宽和输入参考信号频率,获得如图4所示的PM一致而ωC和fREF不同时环路LPF输出电压的瞬态仿真结果。图中(a)和(b)的ωC相同,而(a)的fREF为(b)的一半,这意味着(a)的初始频率/相位差亦为(b)的一半,而仿真结果显示其锁定时间(1.8 ms)也大致为(b)的一半(4 ms)。在fREF保持不变情况下,对比(a)和(d)两条曲线可知,ωC降低一半时锁定时间则延长至4倍。同时,对比(b)和(c)两条曲锁定时间基本一致。这些仿真结果均与前文分析结果吻合。

图4 各种参数下的锁定时间仿真结果

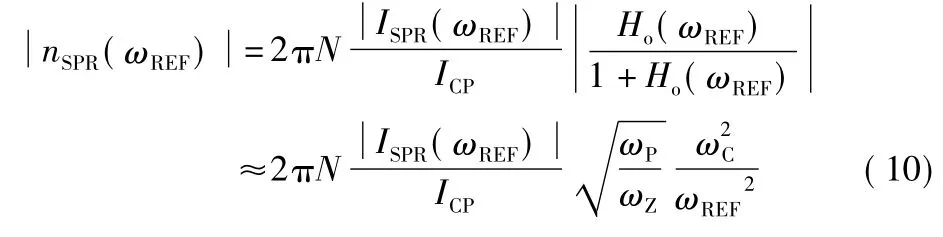

图5 为4种情况下PLL输出信号的频率变换,可以看到(a)情况下杂散强度最大达-58.2 dBc;而在散强度下降6 dB为-64.2 dBc;(b)和(d)由于 ωC/ωREF相同且为(a)的1/2,因而其杂散强度下降12 dB均为-70 dBc;从中可以发现,仿真结果与前文推导一致。

图5 各种参数下杂散强度仿真结果

2.3 相位噪声仿真验证

相位噪声仿真验证中,通过IC663芯片手册获取了VCO的噪声数据[10],同时其他噪声采用热噪声模拟其他噪声源。图6所示为不同环路下相位噪声仿真结果。其中图6(a)为其他参数不变,ωC变化时PLL相位噪声仿真拟合曲线。由于VCO噪声的主导作用,ωC越小,PLL带内相位噪声越明显;另一方面PLL带外噪声却基本保持不变;这与前文中锁相环噪声分析基本一致。通过仿真发现,ωC不变时不同分频比N(图6(b))或不同电荷泵电流ICP(图6(c))的锁相环相位噪声特性基本保持不变。综上可知,在VCO噪声其主导作用下,PLL输出相噪特性基本只取决于ωC。

图6 环路参数变化对锁相环相位噪声影响的仿真结果

3 电路设计与测试验证

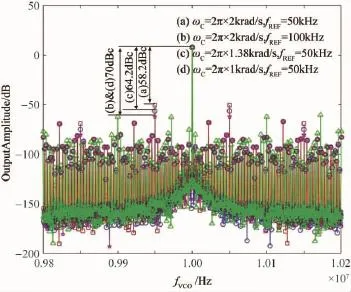

基于锁相环ICS663芯片和分频器芯片ICS674设计了PLL电路并制作了PCB板,其实物如图7所示。其中锁相环的分频系数、环路滤波器参数均通过板上开关切换进行更改。

图7 锁相环电路PCB实物照片

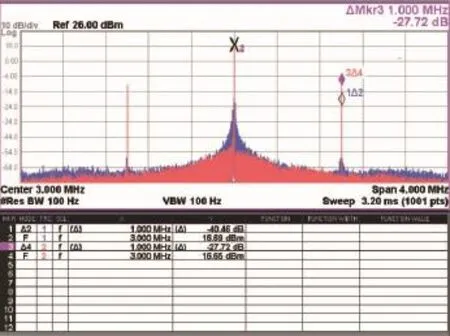

由于实际电路中,输出参考信号的高次谐波很容易耦合至PLL输出中,从而影响杂散的测试。为了减少这种谐波干扰,测试中设置分频系数为3(IC674分频系数必须不小于3),以使PLL输出频率尽量接近参考频率,而此时参考频率设置为fREF=1 MHz。然后分别测试了 ωC为2π×5k rad/s和 ωC=2π ×10k rad/s两种情况下的杂散强度,如图8所示。由图可知,ωC=2π×5k rad/s时杂散强度为-40.46 dB而ωC=2π×10k rad/s时杂散强度升高为-27.72 dB,升高约为12.7 dB,测试结果与式(10)预测基本相符。

图8 不同ωC时杂散测试结果

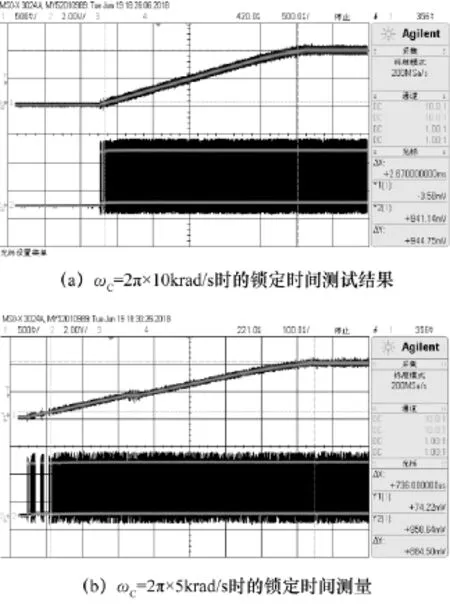

利用Agilent MSO3024示波器测试了以上两种ωC下的锁相环启动过程中LPF输出电压变化情况,其测试结果如图9所示,从图中可以看到锁定时间由736 μs延长延长了约4倍至2.76 ms,证明了锁定时间与ωC成反比。

最终利用Agilent N9020A信号分析仪完成了PLL相位噪声的测试。图10(a)为不同ωC下相位噪声测试结果,从图中可以看出ωC越高则带内噪声越低,而带外噪声基本一致。由于无法改变ICS663芯片内部参数,因而本论文选择通过改变ICS674分频系数来测试ωC相同而分频系数N不同时的相位噪声特性,其结果如图10(b)所示。可以看到,当N在50/100/200之间发生变化时,PLL输出相位噪声输出结果基本保持不变,以上结果均与分析及仿真结果吻合。

4 结束语

首先对Ⅱ型电流泵整数分频锁相环环路特性进行了分析推导,推导结果显示合理选择环路滤波器电容比值可使相位裕度实现最优化,锁定时间与环路截止频率ωC平方成反比,杂散强度与(ωC/ωREF)2成正比等重要结论。进而开展了基于Matlab的锁相环环路仿真验证和基于锁相环芯片ICS663的锁相环电路设计与测试工作,仿真结果与实际电路测试结果均与本文锁相环理论分析结果相符。

图9 不同ωC下锁定时间测试结果

图10 相位噪声测试结果