下变频多速率处理器在频谱感知中的应用

2019-10-08聂梦雅

聂梦雅

摘 要:为了提高认知无线电的感知速度,实现频谱感知的及时性,文章提出利用FPGA极强的实时性和并行处理能力对接收到的数据在融合之前先进行快速处理,主要包括A/D转换器、数控振荡器、抽取器、高速数字滤波器等,最大限度地提高了数据处理的速度。

关键词:认知无线电;现场可编程逻辑门阵列;多速率;下变频

在移动通信迅速发展的今天,人们对频谱资源有越来越大的需求。由于固定的频谱利用率一直非常低,Mitola Joseph博士[1]提出了认知无线电这一解决问题的有效技术手段。

认知无线电主要是指无线终端设备具有了一定的智能或认知能力,能够通过检测、分析、学习、推理和规划周围无线环境的当前状态以及历史情况,利用对应的结果来调整自己的传输参数,使用最合适的频谱资源完成无线传输。这就使得在智能检测的最初环节要尽可能地准确和尽可能地快,一旦数据被采集,那么数据处理的速度就会成为决胜的关键。本文使用了现场可编程逻辑门阵列(Field Programmable Gate Array,FPGA)对采集到的数据首先进行预处理,然后在送往融合准则[2]处,减少了融合时数据量太大导致的延时。

1 多速率接收系统的基本结构

多速率[3]直接定义为对采样后的离散序列进行重新采样,但是接收器接收到的信号为高频信号,所以数据处理之前,需要使用混频的方式把高频信号降速到中频上来。当转换完成后,对其进行抽取和滤波。

1.1 混频器的实现

据上所述,把射频信号降到中频上来主要使用到了混频器,而混频器的主要作用就是把射频信号叠加到本振信号上,所以本振信号的产生就是混频的关键,本文采用的是坐标旋转数字计算方法(Coordinate Rotation Digital Computer,CORDIC)。

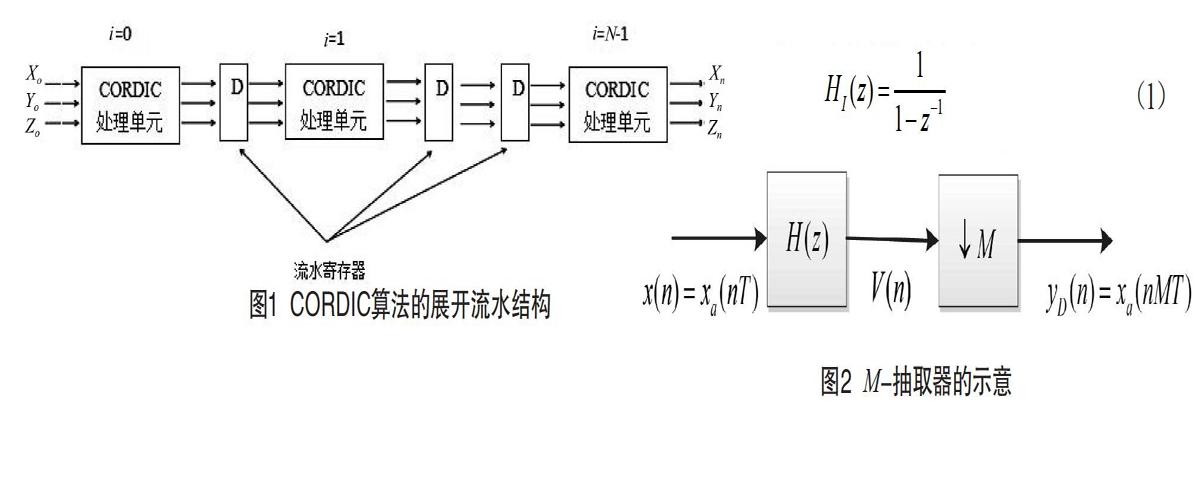

本文CORDIC采用的是展开流水结构,框架如图1所示。它是以占用较多的硬件资源为前提,对原有的展开结构增加流水寄存器,有效缩短关键路径,使得关键路径的长度由紧缩结构[4]的N个CORDIC处理单元变为1个CORDIC处理单元,在最大程度上提高了系统的处理速度。

1.2 整倍抽取滤波器

下采样[5]的主要目的是降低信号的采样频率,主要步骤叫作抽取,主要方法是把原来的采样数据每隔M-1个取出1个,形成新的采样序列。把M叫作抽取因子,要求其取值为大于1的整数。为了实现这一过程,采用M﹣抽取器,如图2所示,其中,输入采样率为f=1/T,输出采样率为f=1/(MT)。

当输入信号x(n)为非带限信号时,被抽取后就容易发生信号频谱混叠,使得原始序列x(n)不能从叠加信号YD(eiω)中恢复出来。所以,为避免这种情况的发生,信号x(n)的带宽须设定在[-π/M,π/M]范围内。所以通常在抽取之前对其低通滤波以达到抗混叠的目的。根据抽取恒等式3:信号先通过滤波器H(zM)再经过M抽取与先进行M抽取再通过滤波器H(zM)是等效的。

1.2.1 CIC抽取滤波器

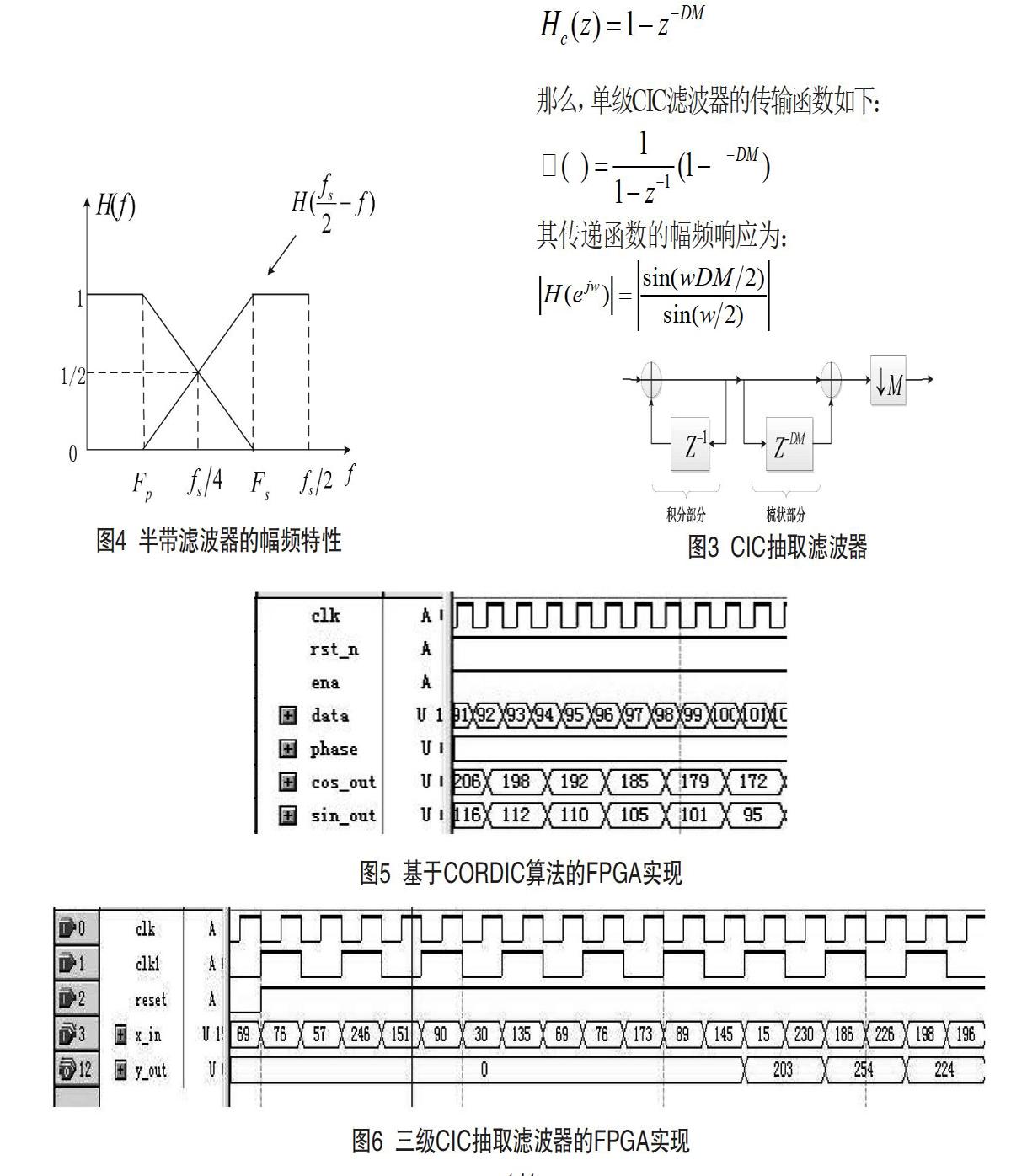

级联积分梳状(Cascade Integrator Comb,CIC)滤波器[6],首先,使用积分器;其次,使用梳状滤波器。CIC由这两部分串联构成,如图3所示。CIC滤波器作为典型的低通滤波器,其具有以下特征:(1)滤波器系数均为1,在实际设计时不用对系数进行存储,很大程度上节省了存储单元,使得滤波运算用不到乘法器,仅需要加法器和累加器。(2)从结构规则来说,可灵活设置抽取因子而不影响整体结构。

例如,当级数N=1时,积分器使用了反馈系数为1的单极点无限脉冲响应滤波器(Infinite Impulse Response,IIR)滤波器,其传输函数如下:

梳状器是一个对称的有限脉冲响应滤波器(Finite Impulse Response,FIR)滤波器,其传输函数如下:

那么,单级CIC滤波器的传输函数如下:

其传递函数的幅频响应为:

1.2.2 FIR半带抽取滤波器

当FIR滤波器[7]在多速率的高速信号处理时,如果实际中阶数和计算量很大,就会使得设计和实现滤波器变得更加困难。在实际应用中,通常先对输入信号进行滤波和提取,并可多次实现,因此,每次都降低了采样率。同时,降低了各阶段抗混叠滤波器的要求。半带滤波器作为一种高速有效的滤波器,特别是对实现数字下变频有着非常好的作用,其简化的频率特性如图4所示。

半带滤波器阻带与通带是相对称的,这表示阻带波动是等于通带波动的;阻带和通带的边频是关于fs/4对称的,有Fp+Fs=fs/2。为了保证FIR滤波器的线性相位要求其系数必须具有偶对称性。即要求h(n)=h(N-1-n),N表示阶数,设为奇数。另外,除中心点系数n=(N-1)/2+1外,所有的h(n)的偶数系数均必须为0。根据半带滤波器的特性:一半系数为0以及FIR滤波器的对称性,使得滤波器的乘法倍数为1/4,加法倍数为1/2,同时,存储系数的存储器也变成1/2,使得数字信号的实时处理具有更高的效率。

1.3 滤波器组

滤波器组表示的是一组滤波器,它们使用同一个输入,然后得到一组输出,称为分析滤波器。当信号x(n)经过分析滤波后,成为N个子带信号。每个子带信号的带宽是原来的1/N,因此,信号速率降低为原来的1/N。实际应用中,通过对分析滤波器组的研究,增加一个N倍抽取滤波器,可达到这一目的。分析滤波器的作用就是将原始信号分成若干个子带,同时,在抽取前完成抗混疊滤波。

1.4 FIR滤波器

在抽取滤波完成之后,还需要使用两个固定系数的滤波器进行常规的滤波。本文主要使用FIR滤波器,优点是精确和严格的相位特性。由有限个采样值组成,在每个采样时刻完成有限个卷积运算,使得其幅频特性不固定,可以满足各种需求。

本文FIR低通滤波器采用窗函数法设计,其参数如下:阶数为60,通带带宽为0.35,采样率为50 KHz,带通带宽为10 KHz,阻带带宽为12.5 KHz。此滤波器主要采用并行结构,可以在一个周期内完成一次滤波,但由于占用大量的乘累加器,使得延时较大,要求工作频率较低,所以在完成抽取后进行滤波比较合适。为了提高运算速度,也可以把寄存器加进去,形成流水线结构,并复用乘加器来节省资源。

2 下变频的实现结果与分析

本文主要是用Verilog语言编程[8],Quartus Ⅱ软件进行仿真,并且使用Matlab软件对仿真结果进行比对并显示,使得结果看起来更加清晰。

2.1 混频器的实现

时钟频率用clk表示;使能分别用rst_n和ena表示;频率控制字用data表示;初始相位用phase表示,其值设为0;输出为sin_out和cos_out,如图5所示。

2.2 抽取滤波器的实现

根据上述方法,为了尽可能地增加数据处理的速度,并且保证保留原始信息,本文采用4倍抽取。其中,2倍抽取来自CIC滤波器,为了改善单级滤波器的性能,本文使用了三阶滤波器,其结果如图6所示。

另外,2倍抽取来自半带抽取滤波器,其主要参数为阶数:8、位宽为16。要求滤波器系数b=[0,-0.109 5,0,0.319 4, 0.500 0, 0.319 4,0,-0.109 5,0],由于硬件描述语言不能处理小数,所以本节进行16 bit的量化,系数b=[0,-3 588,0,10 466, 16 384,10 466, 0,-3 588,0],半带抽取滤波器的功能仿真如图7所示。

2.3 综合实现

本文使用减幅信号作为输入,首先,使用滤波器组中的分析滤波器中的高通和低通滤波器得到两个子带信号;其次,对子带信号进行CIC抽取和半带抽取;最后,通过一个60阶FIR低通滤波器进行综合仿真。为了得到更加简洁的结果,把数据导入Matlab,得到结果如图8所示。

3 结语

本文主要使用FPGA和Matlab两个软件,对接收到的频谱数据进行下变频处理,使得这些数据能够在保持原有信号特征的基础上,最大限度地减少数据量,使得计算变得更加迅速,能够满足实时處理的要求。

[参考文献]

[1]MITOLA J.Cognitive radio:an integrated agent architecture for software defined radios[D].Stockholm:Royal Institute of Technology(KTH),2002.

[2]温志刚.认知无线电频谱检测理论与实践[M].北京:北京邮电大学出版社,2011.

[3]高亚军.基于FPGA的数字信号处理[M].北京:电子工业出版社,2012.

[4]田耘,徐文波,张延伟,等.无线通信FPGA设计[M].北京:电子工业出版社,2008.

[5]谢海霞,孙志雄.多速率信号处理系统设计与实现[J].电子设计工程,2018(5):132-137.

[6]刘兴举.基于FPGA的软件无线电上下变频技术的设计研究[J].无线互联科技,2015(5):16-17.

[7]SHEHEE,CROWDER,RUDISILL.Determination of filter pore size for use in HB line phase II production of plutonium Oxide[J].Separation Science and Technology,2015(17):2798-2802.

[8]夏宇闻.Verilog数字系统设计教程[M].北京:北京航天航空大学出版社,2008.