基于混合SETMOS 结构的超前进位加法器

2019-09-23曲航刘德州周海力侯兴华

曲航,刘德州,周海力,侯兴华

(中国船舶工业系统工程研究院,北京,100094)

0 引言

在集成电路中,加法是最重要的一种逻辑运算。 通过按不同的方式组合加法器模块,我们能实现诸如快速加法器之类的许多功能,而增加运算速度并减少基础加法器电路的复杂程度在实际设计集成电路时非常重要。虽然基于MOS工艺的加法器等电路广泛应用于现代电子行业,但随着器件小型化及提升运行速度的需求越来越旺盛, MOS 工艺的局限性逐渐凸显了出来,例如其最小仅能达到几百微米级,且具有量子效应和对微小电流不敏感等特性。另外,继续在已经开发到极限MOS 器件上继续拓展新应用的经济效益很低[1]。

相比之下,单电子晶体管(Single-electron Transistor,SET)则拥有极低功耗、更小的纳米级工艺制程、以及实现更多的逻辑功能等巨大潜力,这是由于其在缩小空间的同时还拥有其独有的库伦阻塞效应。然而目前纯粹的SET 器件因灵敏度极高而很容易受干扰,并且必须在较低温度下才能展现良好的电流特性,甚至不能在一般室温条件下正常运转。因此,当前最好的解决方法是将SET 和MOS 工艺结合起来制成一种全新的SETMOS 混合电路,如此便可最大限度地降低SET 器件固有的缺陷。

本文首先将通过基础SETMOS 混合逻辑电路构建一个加法器,然后在此基础上发展出一种全新的超前进位加法器(carry look-ahead adder, CLA) ,以此来替代传统的由全加器组成的加法器,并提高了电路的可靠性及运算速度。

1 SETMOS 基础逻辑门电路

1.1 单电子晶体管

SET 晶体管结构包含2 个隧道结和数个电容。通常意义上, SET是由源极、漏极、1个夹在2处隧道结之间的“岛”、以及控制岛内电子数量的门电容所组成的。SET 结构在纳米级的电路下具有良好表现,因为它可以基于库伦阻塞定律精准地将微小的电子一个接一个地传导,如此便可精细控制电流并降低功耗。

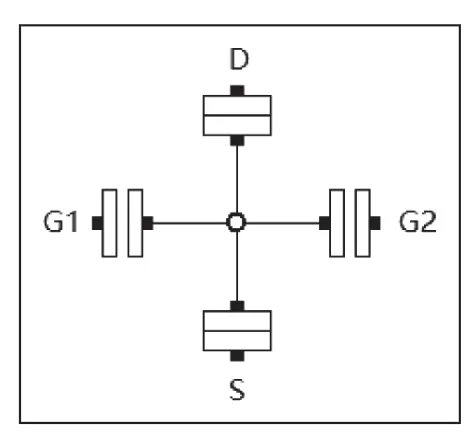

与MOS 管一样,SET 管也存在源极、漏极和栅极,不同的是后者的源极、漏极为隧道结,而栅极则是集成在SET 管中的电容。通常SET可以包含单个或多个电容,即拥有单个或多个栅极[2]。图1 展示了一个双栅SET 管的电路结构,本文主要采用双栅SET 来组合电路。

图1 双栅SET 管

1.2 纯SET 结构门电路的局限

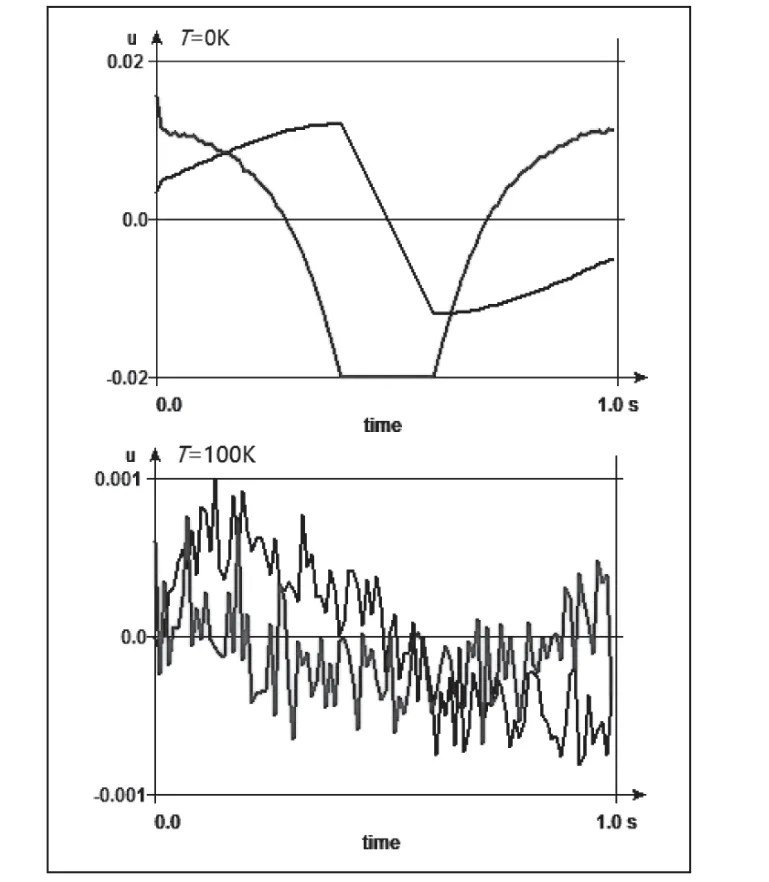

然而,SET管对背景电荷等许多类型的干扰都极为敏感;更有甚者,SET 管只有在温度极低的情况下才能运行良好,在常温下工作时则会功能紊乱,这是由于SET 器件工作时所产生的库伦震荡现象会随着温度升高而幅度逐渐减小甚至几近消失。相关研究表明SET 管的理想运行温度十分接近绝对零度[3],至少得保持在比较接近绝对零度的条件下方可维持功能。图2 展示了软件仿真的一种纯SET 非门分别在0K(-273.15℃)和100K(-173.15℃)时的特性曲线[4],从中可以看到SET 电路在远远低于0℃时就已经出现了严重的失真现象,且电压幅度范围也大为缩水。上述问题极大限制了SET 元器件在实际复杂条件下的应用。

图2 纯SET 非门电路在不同温度下的特性曲线

与SET 相比,MOS 的对外敏感度和输出阻抗更低,但电压增益却很高,且作为常用器件的MOS 拥有良好的可靠性与环境适应性。这两类器件在直观的对外接口和整体功能上都十分相似,具备协同使用的条件。将它们融合起来一定程度上既可结合二者独有的优点,又能降低双方各自的缺陷。特别是对于SET 来说,MOS 良好的温度承受能力具有无与伦比的补偿作用[5]。

1.3 SETMOS 混合非门电路单元

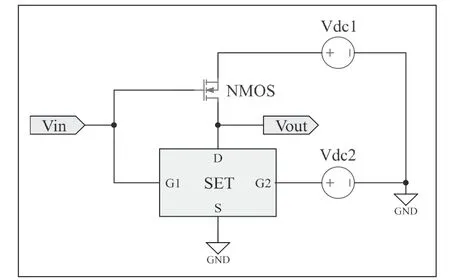

图3 演示了一种基于SETMOS 混合工艺构建的反相器,即非门。其中Vin表示输入电压,Vout表示输出电压。功能上它等同于纯粹的MOS 非门,但电路上则将下拉MOS 晶体管替换成了1 个SET 管[6]。

图3 SETMOS 混合器件构建的非门

图中的SET 选用了MIB 提供的双栅模型[7],其相关 参 数 设 置 如 下:CG1=CG2=0.3aF,CD=CS=0.3aF,RD=RS=1MΩ。其中CG1、CG2为栅极电容,CD为漏极电容,CS为源极电容,RD为漏极电阻,RS为源极电阻。而SETMOS结构中的MOS 应选用NMOS 来与SET 相匹配[8],本文选用的是CMOSP18 模型。MOS 管的相关参数设置如下:W=500nm,L=180nm。其中W、L 分别为MOS 管沟道的长度和宽度。此外,通常需要提供不低于300mV 来启动CMOSP18 模型。这里设置Vdc1=365mV,Vdc2=750mV。

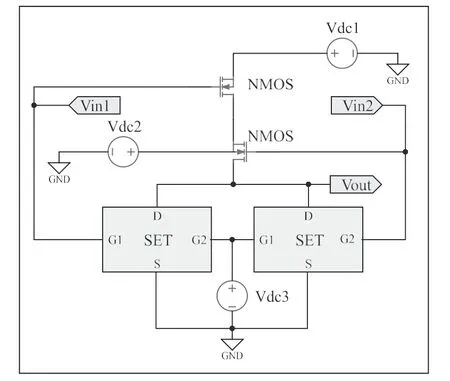

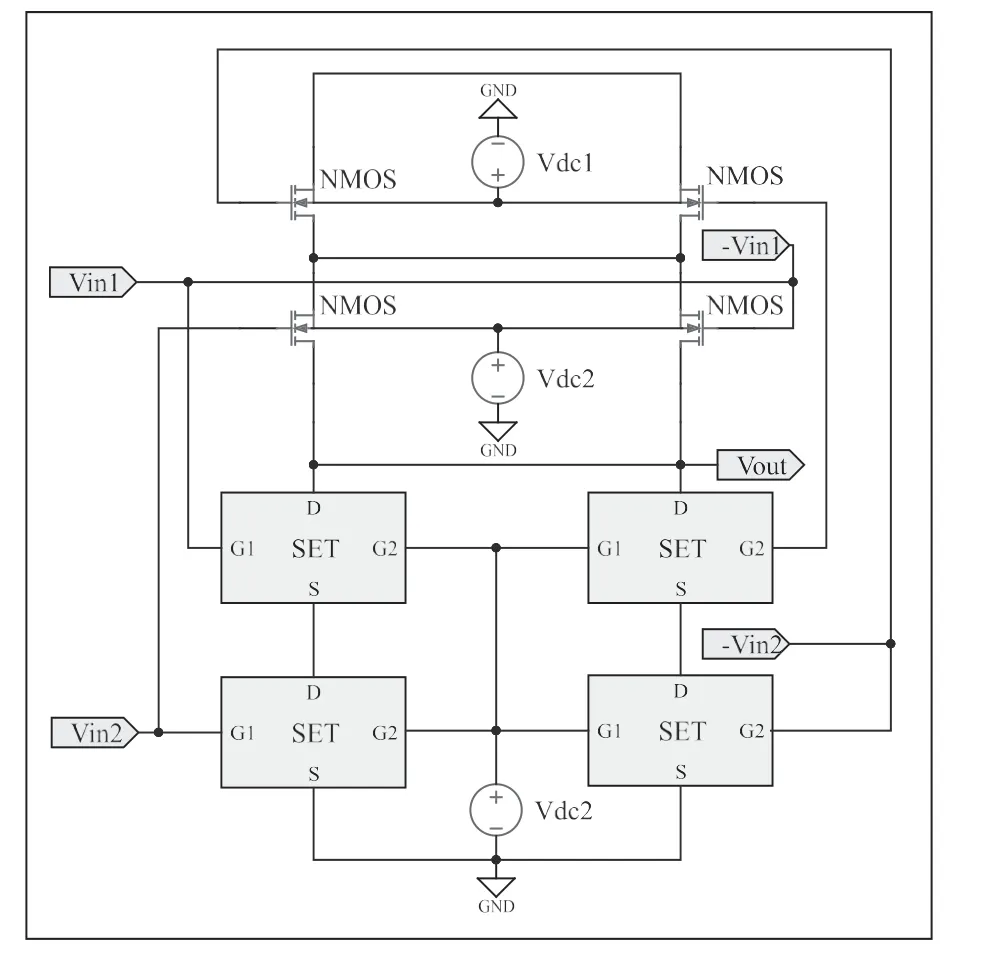

图4 SETMOS 与非门

与同类MOS 电路结构相比,这种设计方式显著降低了非门的总功耗(约几百pW)和传输延迟时间(低于100ns)[9]。

图5 SETMOS 或非门

图6 SETMOS 异或门

1.4 其他混合逻辑电路单元

同理,我们可以创造出其他由混合器件构建的与非门、或非门和异或门,其电路原理分别如图4、图5、图6 所示。在SETMOS 与非门中,设置Vdc1=365mV,Vdc2=750mV,Vdc3=750mV;在SETMOS 或非门中,设置Vdc1=750mV,Vdc2=750mV,Vdc3=365mV;在SETMOS 异或门中,设置Vdc1=750mV,Vdc2=750mV,Vdc3=365mV。

将SETMOS 非门与上述与非门、或非门串联起来,就可以得到SETMOS 结构的与门、或门等其他混合逻辑电路。

SETMOS 门电路同常规门电路一样,可以加以组合连接从而形成能执行更复杂功能的集成电路。但需要注意,在一条电路线路中不要同时串联过多的SETMOS 门,因为SETMOS 电路的输出有时会有几毫伏甚至十几毫伏的衰减,在不添加任何放大电路的前提下,串联SETMOS 电路中的衰减经过叠加后会变得很可观,导致传输线路后方的门电路从前方电路得到的输入信号越来越微弱,对阈值的设定的精度要求将变得十分苛刻。此外,由于SET 本身容易受干扰的特性并未因与MOS 融合而完全消除,各种形式的干扰也更容易使后方门电路得到的输入波动从而干扰阈值判断。

由于本文讨论的CLA 电路结构具有明显的并行特征,因此通过SETMOS 门电路来构建CLA 可以在很大程度上规避传统加法器在进行多位运算时需要串联许多全加器的问题,电路的可靠性将有所保障。

2 SETMOS 超前进位加法器

2.1 CLA 原理

加法运算经常需要进位,而可以实现单独1 位加法并计算进位的全加器是最基础的加法器之一,同时也是组成其他大多数逻辑运算电路的基本逻辑单元之一。1 个单位全加器可由2 个与门、2 个或非门以及1 个或门组合构建。 若想实现多位相加功能,只需组合数个最基本的单位全加器,也就是把前一位全加器的进位输出与后一位全加器的进位输入串联,如此便生成了脉冲进位加法器。

脉冲进位加法器结构简单却有很多局限,因为如果想要运算得到最终结果,加法器的每一位都需要先从上一位获悉进位结果才能进行本位求和,进而再将本位进位传递给下一位,这种一次只能处理一位数据的运算方式将大幅降低电子器件的运行速度[10]。除此之外,如果直接使用SETMOS 混合设计来实现全加器进而实现脉冲进位加法器,其可靠性更加难以得到保证,因为SETMOS 混合后的电路对外界干扰仍然有一定的敏感性,一旦构成脉冲进位加法器的某一位全加器因受到干扰而产生错误的进位,将会影响到全部后续其他位的运算结果。

为了提高SETMOS 多位加法器的运算速度和电路可靠性,组建具有平行运算结构的超前进位加法器更加合理。本文所展示的例子是SETMOS 结构下的3 位超前进位加法器。

在数学上,加法器第i 位的运算结果Si可由下面公式求得:

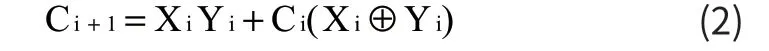

式中Xi和Yi分别表示第i 位的加数和被加数,Ci则表示来自前一位的进位。而第i 位向第i+1 位所提供的进位Ci+1则如下所示:

为了切断进位链,如果设定2 个中间变量Gi和Pi如下:

可得到:

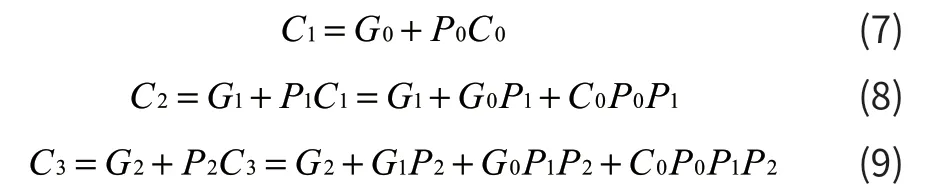

展开公式(6)后,各位的Ci可由下列公式表示:

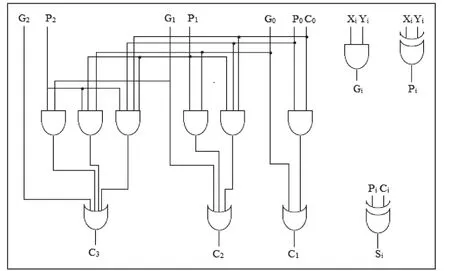

通过公式(3)、(4)、(5)、(7)、(8)、(9)可以设计出3 位CLA 的原理图,具体如图7 所示。

从原理图中不难看出,每一位的进位输入Ci是同时独立生成的,不同位的Ci的与其他位的进位输出Ci+1没有直接关系,因此可以同时生成全部各位的求和。

2.2 基于混合电路的CLA

将先前设计的各SETMOS 逻辑单元带入图7 所示的原理图中,最终我们可以得到采用SETMOS 器件构建的3 位CLA。

图7 3 位CLA 原理图

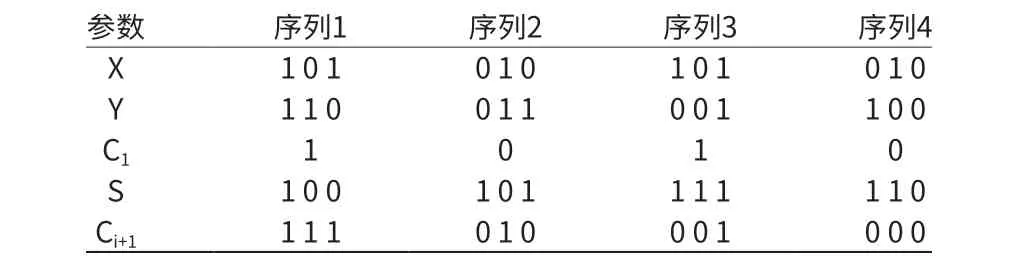

为了验证基于混合SETMOS 结构CLA 的正确性,需对其进行功能性能测试。这里我们通过CADENCE 进行软件仿真,并分别按照表1 中的数值赋予加法器的输入X、Y、C1,它们的大小可以在0V 及100mV(或低于100mV 但高于80mV 的某个值)两个电压值之间选取。其中X、Y 均为矩形脉冲数组,形成多种不同的3 位二进制加数组合对,而C1则表示X、Y 相加时来自第0 位的进位,每一个C1对应一组X、Y。所有的测试均模拟在室温(27℃)条件下进行。

3 测试结果及分析

3.1 功能测试结果

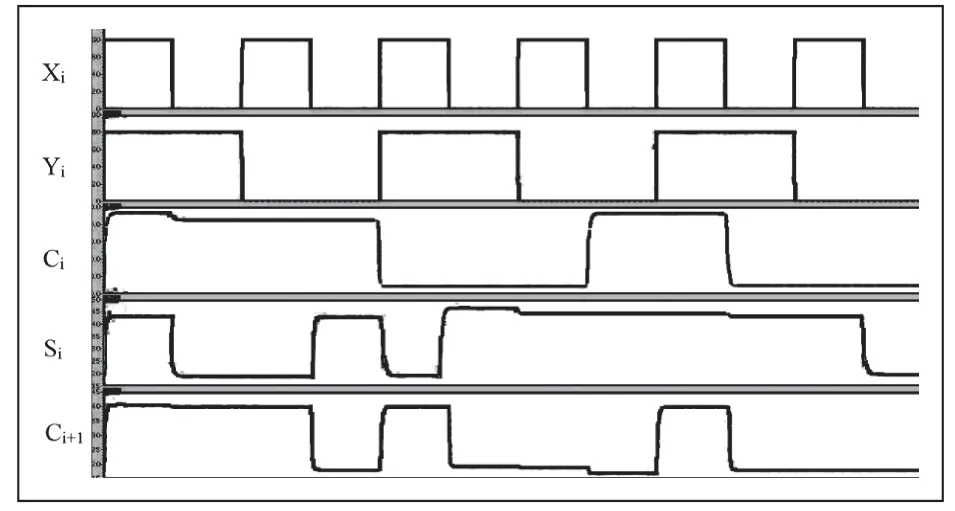

软件仿真的结果如图8 所示,从图中可以看到SETMOS 加法器的脉冲波形基本良好。将测试结果转换成二进制数值的形式后,得到的运算结果如表1 所示。其中Ci表示进行第i 位加法运算时来自之前一位的进位值,S 表示X、Y、C1相加后得到的最终3 位加法运算结果,Ci+1表示第i 位运算后应当向下一位、即第i+1 位输送的进位值。

以序列1 的输入组合为例,加数X 和Y 分别为3 位二进制数1 0 1 和1 1 0,他们在相加时也要同步与来自第0 位的初始进位C1相加,此刻C1等于1。经过SETMOS 架构的CLA 运算后得到的3 位二进制输出结果S 为0 1 1,而每一位运算所产生的的对下一位的进位Ci+1为1 1 1。

总结一下可以简单描述为:X、Y、C1相加后得到了结果为0 1 1 的3 位二进制数值,并继续向3 位CLA 以外的第4 位产生了高电平进位C4。这一结果完全符合加法运算规律,同理其他序列的运算组合经由SETMOS 架构的CLA 得到的结果也完全正确。输出波形上,只要将阈值设置在高低电平中间位置即可妥善将二进制的0、1 区分出来。因此从功能性能的角度来看,SETMOS 混合器件可以在常温下实现超前进位加法计算。

图8 3 位SETMOS 结构CLA 的输入输出脉冲仿真结果

表1 SETMOS CLA测试输入及结果(27 ℃)

3.2 性能提升

(1)电路复杂度:相较于MOSFET, SET 管内已经集成了电容结构,因此在设计SETMOS 混合电路CLA 时不需要额外添加电容,更加便于设计连线。

(2)尺寸:作为纳米电子器件的SET 拉低了混合电路的整体尺寸,同时由于不需要额外添加电容进一步节省了空间。

(3)功耗:3 位SETMOS 结构的CLA 中间及输出电压功耗及发热情况均不高,一般只有几纳瓦甚至更低。

(4)运算速度:与同等复杂程度的MOS 加法器相比,SETMOS 加法器运行速度更快,这是由于每个混合逻辑电路门均比纯MOS 门节省了十几甚至几十纳秒的间隔时间,而基于超前进位加法器的原理,最终总共可以节省4log4N倍的间隔时间,其中N 表示加法器位数。通常3 位CLA 在SETMOS 结构下可以比通常的MOS 加法器快0.6~3.5 微秒。

4 结语

本文所介绍的基于混合SETMOS 晶体管结构的超前进位加法器拥有比常规MOS 加法器更快的运行速度和更小的尺寸,并且通过结合SET 与MOS 两种类型的器件一定程度上弥补了SET 固有的缺陷,使其初步具备实际应用的条件。接下来的研究方向与改进空间主要在于能否实现SET 器件在更加恶劣环境、尤其是高温条件下的正常工作。一旦在温度问题上形成突破,SET 器件将有很大潜力成为下一代集成控制电路的核心部分,实现电子制造设计领域的重大飞跃。