MF200多频中波发射机自适应载波CIC内插滤波器设计

2019-09-17潘杰

潘杰

摘 要:MF200多频中波发射机采用全新的数字调制器技术对音频信号及射频进行处理和分配控制,采用了自适应采样率转换方法对音频信号进行采样率提升同步至载波频域内。针对信号采样率转换及高频音频信号抽样量化失真的问题,采用了CIC数字内插滤波器设计方案。方案对异步采样率转换输出后的音频信号进行固定8倍内插,将音频信号采样率自适应变换到载波频率上,并在调制器音频处理板FPGA上实现。实际测试表明,该方案可以有效解决高频率音频信号抽样量化失真问题,同时,解决了数字调制器中音频信号自适应采样率二次转换问题,可以满足不同载波频率对音频信号采样率转换的需求,进一步提升了发射机的信号失真度指标。

关键词:多频中波发射机 载波频率 自适应采样率 量化失真 CIC内插滤波器

中图分类号:TN931 文献标识码:A 文章编号:1672-3791(2019)07(a)-0003-05

Abstract: The MF200 multi-frequency medium wave transmitter uses the new digital modulator technology to process the audio signal and distribute the radio frequency. The adaptive sampling rate conversion method is used to synchronize the sampling rate of the audio signal to the carrier frequency domain. The CIC digital interpolation filter design scheme is adopted for the problem of signal sampling rate conversion and high-frequency audio signal sampling and quantization distortion. The scheme performs a fixed eight times interpolation on audio signal output by Asynchronous Sample Rate Converters(ASRC), adaptively transforms the audio signal sampling rate to carrier frequency, and implements it on the FPGA of modulator audio processing board. The actual test on the transmitter shows that the scheme can effectively solve the problem of sampling and quantization distortion of high-frequency audio signal. At the same time, the scheme solves the problem of secondary sampling of adaptive sampling rate of audio signal in the digital modulator which can meet the requirements of different carrier frequencies for sampling rate conversion of audio signal and further improved the signal distortion index of the transmitter.

Key Words: Multi-frequency medium wave transmitter; Carrier frequency; Adaptive sampling rate; Quantization distortion; CIV interpolation filter

MF200多频中波发射机数字调制器音频输入信号采用的是标准48kHz采样率信号[1],与笔者所在台中波机房发射机的载波频率不成整数倍关系,考虑到MF200多頻中波机需要满足多个载波频率的播音需求,因此,对不同载波频率下音频信号的采样率转换处理变得尤为重要,其过程也更为复杂。

针对上述问题,在数字调制器系统设计中对音频信号采用了两次自适应采样率转换的方案,通过DSP与FPGA实现上述转换过程。针对第一次异步采样率转换过程中,高频率音频信号抽样出现的量化失真问题,该文设计了CIC数字内插滤波器方案,对异步采样率转换输出后的音频信号进行8倍内插,做第二次采样率转换,从而实现将音频信号采样率提升至载波频率,解决了高频音频信号抽样量化失真的问题。该方案可以满足不同载波频率下音频信号的自适应采样率转换需求,进一步提高了输出调幅波的失真度指标,大大提高了数字调制器音频信号处理的速度和效率。

1 音频自适应采样率转换方案

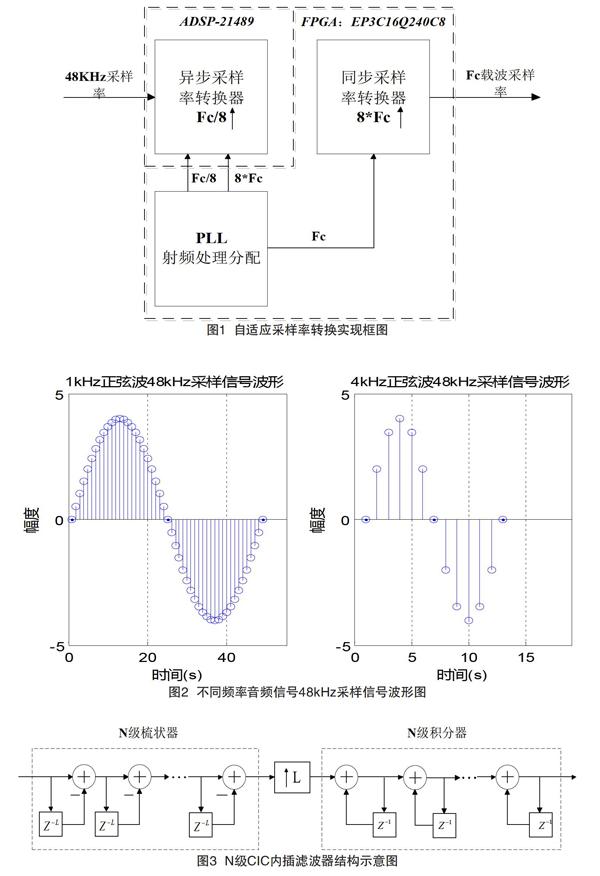

在MF200多频中波发射机数字调制器中,设计的音频信号自适应采样率转换方案如图1所示。其实现过程由音频处理板上的DSP芯片ADSP-21489和FPGA芯片EP3C16共同完成。

具体实现过程如下:DSP首先完成对外部输入音频的48kHz采样率抽样,再利用其内部集成的异步采样率转换器(其异步采样率能够保证在7.75∶1~1∶8比例范围内任意小数倍数的采样率转换)将48kHz采样率音频信号转换到载波频率的8分频上,异步采样率转换的帧频和位频由FPGA处理芯片EP3C16的射频处理分配模块提供。利用射频处理分配模块得到的1/8×Fc频率(Fc为载波频率)分量,可以将音频信号的采样率变换到载频的8分频频率上,在FPGA芯片中再对音频数据进行8倍采样率数据转换,从而得到以载波频率采样率的音频数据,完成整个音频自适应采样率转换过程。

2 高频率音频信號量化失真问题

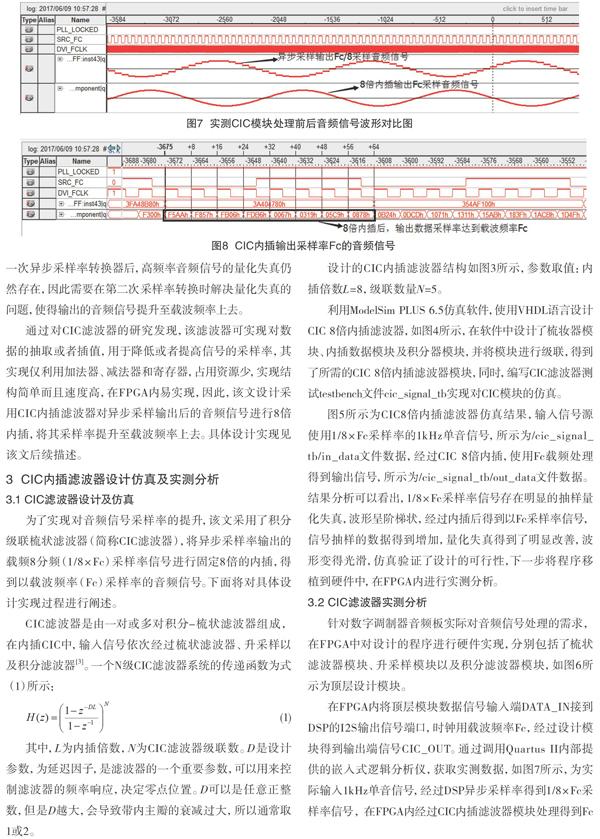

由于在DSP采用了标准的48kHz采样率对外部输入音频进行AD采样,因此,当随着音频信号频率的提高,采样的点数越少,不可避免地会出现采样信号的量化失真,如图2所示,为1kHz正弦波和4kHz正弦波采用48kHz采样率抽样得到的信号波形,可以看出4kHz正弦波得到的采样信号点数相比1kHz采样信号点数明显减小,量化失真增大。经过第一次异步采样率转换器后,高频率音频信号的量化失真仍然存在,因此需要在第二次采样率转换时解决量化失真的问题,使得输出的音频信号提升至载波频率上去。

通过对CIC滤波器的研究发现,该滤波器可实现对数据的抽取或者插值,用于降低或者提高信号的采样率,其实现仅利用加法器、减法器和寄存器,占用资源少,实现结构简单而且速度高,在FPGA内易实现,因此,该文设计采用CIC内插滤波器对异步采样输出后的音频信号进行8倍内插,将其采样率提升至载波频率上去。具体设计实现见该文后续描述。

3 CIC内插滤波器设计仿真及实测分析

3.1 CIC滤波器设计及仿真

为了实现对音频信号采样率的提升,该文采用了积分级联梳状滤波器(简称CIC滤波器),将异步采样率输出的载频8分频(1/8×Fc)采样率信号进行固定8倍的内插,得到以载波频率(Fc)采样率的音频信号。下面将对具体设计实现过程进行阐述。

CIC滤波器是由一对或多对积分-梳状滤波器组成,在内插CIC中,输入信号依次经过梳状滤波器、升采样以及积分滤波器[3]。一个N级CIC滤波器系统的传递函数为式(1)所示:

其中,L为内插倍数,N为CIC滤波器级联数。D是设计参数,为延迟因子,是滤波器的一个重要参数,可以用来控制滤波器的频率响应,决定零点位置。D可以是任意正整数,但是D越大,会导致带内主瓣的衰减过大,所以通常取1或2。

设计的CIC内插滤波器结构如图3所示,参数取值:内插倍数L=8,级联数量N=5。

利用ModelSim PLUS 6.5仿真软件,使用VHDL语言设计CIC 8倍内插滤波器,如图4所示,在软件中设计了梳妆器模块、内插数据模块及积分器模块,并将模块进行级联,得到了所需的CIC 8倍内插滤波器模块,同时,编写CIC滤波器测试testbench文件cic_signal_tb实现对CIC模块的仿真。

图5所示为CIC8倍内插滤波器仿真结果,输入信号源使用1/8×Fc采样率的1kHz单音信号,所示为/cic_signal_tb/in_data文件数据,经过CIC 8倍内插,使用Fc载频处理得到输出信号,所示为/cic_signal_tb/out_data文件数据。结果分析可以看出,1/8×Fc采样率信号存在明显的抽样量化失真,波形呈阶梯状,经过内插后得到以Fc采样率信号,信号抽样的数据得到增加,量化失真得到了明显改善,波形变得光滑,仿真验证了设计的可行性,下一步将程序移植到硬件中,在FPGA内进行实测分析。

3.2 CIC滤波器实测分析

针对数字调制器音频板实际对音频信号处理的需求,在FPGA中对设计的程序进行硬件实现,分别包括了梳状滤波器模块、升采样模块以及积分滤波器模块,如图6所示为顶层设计模块。

在FPGA内将顶层模块数据信号输入端DATA_IN接到DSP的I2S输出信号端口,时钟用载波频率Fc,经过设计模块得到输出端信号CIC_OUT。通过调用Quartus II内部提供的嵌入式逻辑分析仪,获取实测数据,如图7所示,为实际输入1kHz单音信号,经过DSP异步采样率得到1/8×Fc采样率信号,在FPGA内经过CIC内插滤波器模块处理得到FcFc采样率信号。通过图7中实测波形分析可以看出,未经过CIC前的音频采样信号有明显的失真,呈阶梯状,对最终功放模块合成输出调幅波失真有较大的影响。经过CIC后音频信号采样率提升至载波频率,信号波形阶梯状得到了明显改善,曲线变得光滑,进一步提高了输出调幅信号的失真度指标(见图8)。

4 结语

该文针对MF200多频中波发射机数字调制器系统中音频信号处理模块出现的信号采样率转换及高频音频信号抽样带来的量化失真问题,利用多倍内插滤波器方法解决采样率转换问题。方案主要设计了CIC数字内插滤波器,将DSP异步采样率转换得到的1/8×Fc采样率音频信号通过8倍CIC内插,进行二次自适应采样率转换,实现了将48kHz采样率的音频信号提升至载波频率。实测结果表明,该方案有效地解决了数字调制器对于音频信号采样率转换的问题,同时解决了高频音频信号抽样量化失真的问题,可以满足不同载波频率对音频信号采样率转换的需求。方案进一步提升了MF200发射机的信号失真度指标,对于实际播音需求具有重要的意义。

参考文献

[1] 徐帮辉,聂志龙,肖秋华,等.MF-200多频中波发射机的研制[A].2014国际传输与覆盖研讨会论文集[C].2014.

[2] 陈向东,吴祎,韩向兵.DAM发射机音频量化盈亏补偿初探[J].中国传媒科技,2013(24):119-120.

[3] 卢笛.基于FPGA的多速率数字信号上下变频的实现[D]. 西安电子科技大学,2012.

[4] 崔成华,向涛,王园园.基于MATLAB的CIC滤波器设计[J].中国无线电,2015(9):47-48.

[5] 周润景,图雅,张丽敏.基于Quartus II的FPGA/CPLD数字系统设计实例[M].北京:电子工业出版社,2007.

[6] 胡广书.数字信号处理[M].北京:清华大学出版社,2003.

[7] 夏宇闻.复杂数字电路与系统Verilog HDL设计技术[M].北京:北京航空航天大学出版社,2002:137-170.