基于FPGA的多路Cameralink数字图像光纤传输系统

2019-09-13白金成

白金成

(中国科学院 长春光学精密机械与物理研究所,吉林 长春 130033)

1 引 言

随着无人机行业的快速发展,航空光电吊舱作为机载的重要侦查设备,在目标捕获、跟踪、识别等领域得到了广泛的应用[1]。航空光电吊舱的跟踪[2]、识别是通过对高可靠性的数字图像实时处理实现的,因此高速可靠的图像传输是影响其跟踪、识别等性能优劣的重要指标之一。

传统的航空光电吊舱大多采用导电环进行Cameralink协议[3]的数字图像传输,存在传输带宽低、抗干扰性差、配线复杂等问题,后期的错误排查也非常困难[4]。数字图像的传输问题一定程度上制约了光电吊舱的发展。光纤传输由于抗干扰能力强、带宽高、易敷设、寿命长等特点被广泛应用于数据传输方面,利用光纤传输数字图像,可以克服传统导电环传输数字图像的诸多缺点,很大程度提高了数字图像传输的抗干扰能力和可靠性[5]。

目前,许多航空光电吊舱的数字图像都采用光纤传输的方式,例如基于MAX9259/MAX9260的光纤传输,虽然开发速度快,但是灵活性不强且传输带宽有一定的限制[6],并且目前很多光电吊舱的数字图像光纤传输都是单通道的,无法满足多路图像的同时传输[5,7],随着数字相机的频率越来越高,传输的数据量越来越大,航空光电吊舱对数据传输的要求越来越高[8],本文设计了数字图像光纤传输系统,利用单根光纤传输多路Cameralink数字图像,以FPGA为核心处理芯片,采用Aurora 8 B/10 B协议,并结合HTW0402HTW4002光模块实现多路Cameralink数字图像的光纤传输。

2 FPGA光纤传输系统设计

2.1 系统硬件结构设计

系统硬件结构如图1所示。本系统选用FPGA作为系统控制处理核心,结合图像编解码芯片及光模块实现多路Cameralink数字图像的光纤传输。

图像编解码:输入的图像为LVDS的Cameralink数字图像,利用解码芯片DS90CR286MTD将LVDS信号转化为28位并行TTL信号,其中包括24位数据、1位帧同步和1位像素时钟信号、2位行场同步信号。在接收端,采用编码芯片DS90CR285MTD完成相反的工作,将FPGA输出的28位并行TTL信号转换为LVDS图像信号,还原输入的原LVDS的Cameralink数字图像。

FPGA控制处理器:FPGA作为光纤传输系统的核心处理器件,实现整个系统时钟的控制、数据处理、串并转换的信号控制等功能。在发送端,FPGA接收经解码单元转换后的并行数据,根据相机输出时钟的具体情况,对数据做相应处理,并产生控制信号,将处理后的数据及控制信号进行并转串的操作;在接收端,FPGA根据串并转换单元的信息,解出相机的时钟信号,并还原数据及行、场同步信号传输给视频采集设备。

图1 系统结构硬件框图Fig.1 Hardware block diagram of system structure

收发光模块:光模块负责光信号与电信号的相互转换。本系统选用的是中航光电的型号为HTW4002(发送)/HTW0402(接收)的光模块,该型号光模块是一款高性能的4路CWMD光模块,单通道最大传输速率为10.312 5 Gb/s,可用于10 km内光互联数据通信。该模块通过一根光纤可完成4路信号的传输,操作简单,使用方便,且满足宽工作温度范围,性能稳定。

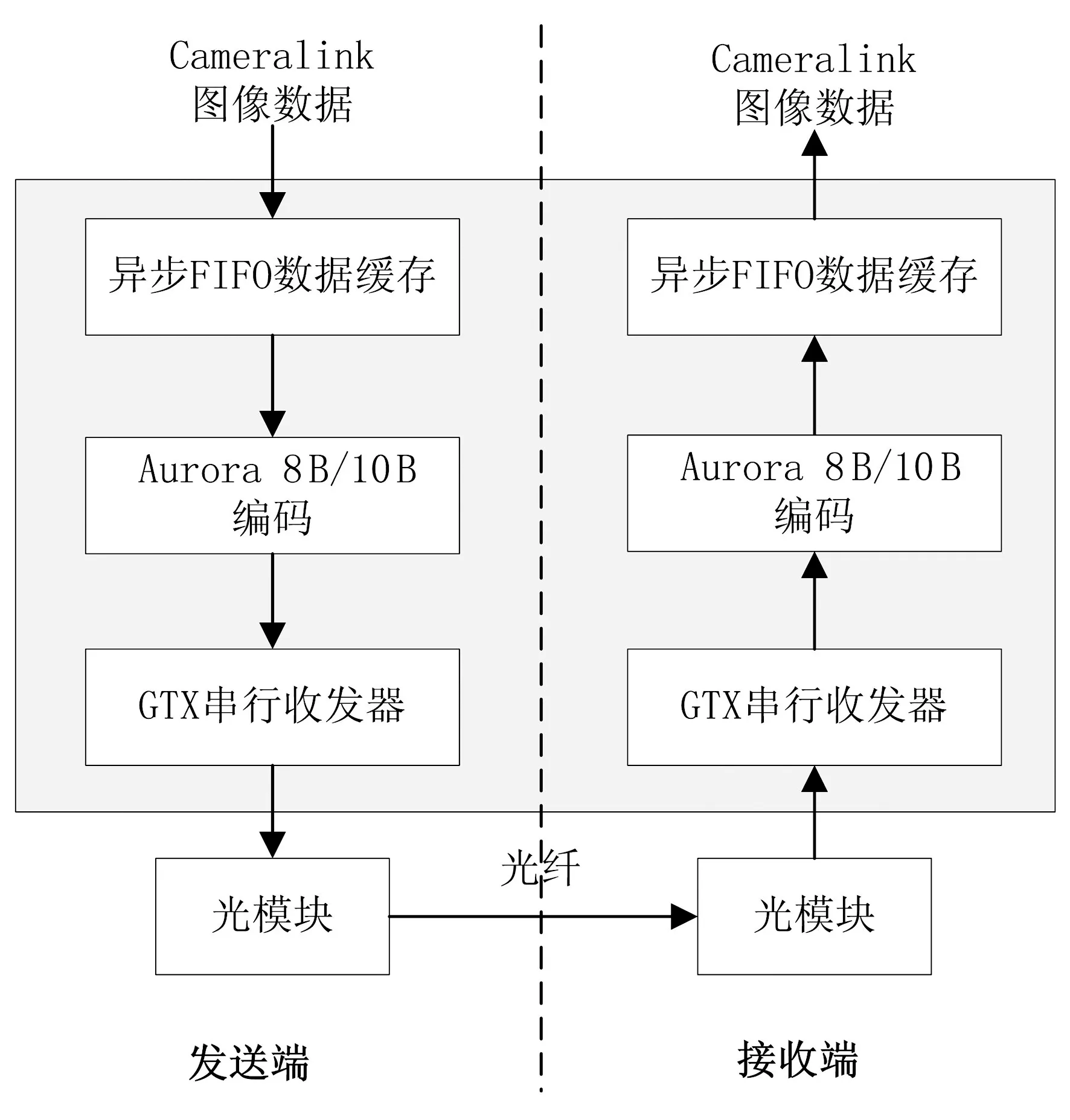

2.2 光纤传输方案设计

Cameralink数字图像光纤传输设计方案如图2所示。在发送端,通过异步FIFO将转换后的TTL并行图像数据信号进行数据缓存,将相机时钟域转换到Aurora协议的用户时钟域;按照Aurora 8 B/10 B协议将异步FIFO缓存后的数据进行编码,编码后的数据经GTX串行收发器转换为高速串行的数据送入到发送光模块,经光纤导线传到接收端;在接收端,串行收发器将光模块接收到的串行数据按照协议转换成并行数据并解码,再经异步FIFO进行数据重建,将并行图像数据从Aurora协议用户时钟域转换到相机时钟域,完成了Cameralink数字图像的光纤传输。

图2 光纤传输设计方案框图Fig.2 Block diagram of optical fiber transmission

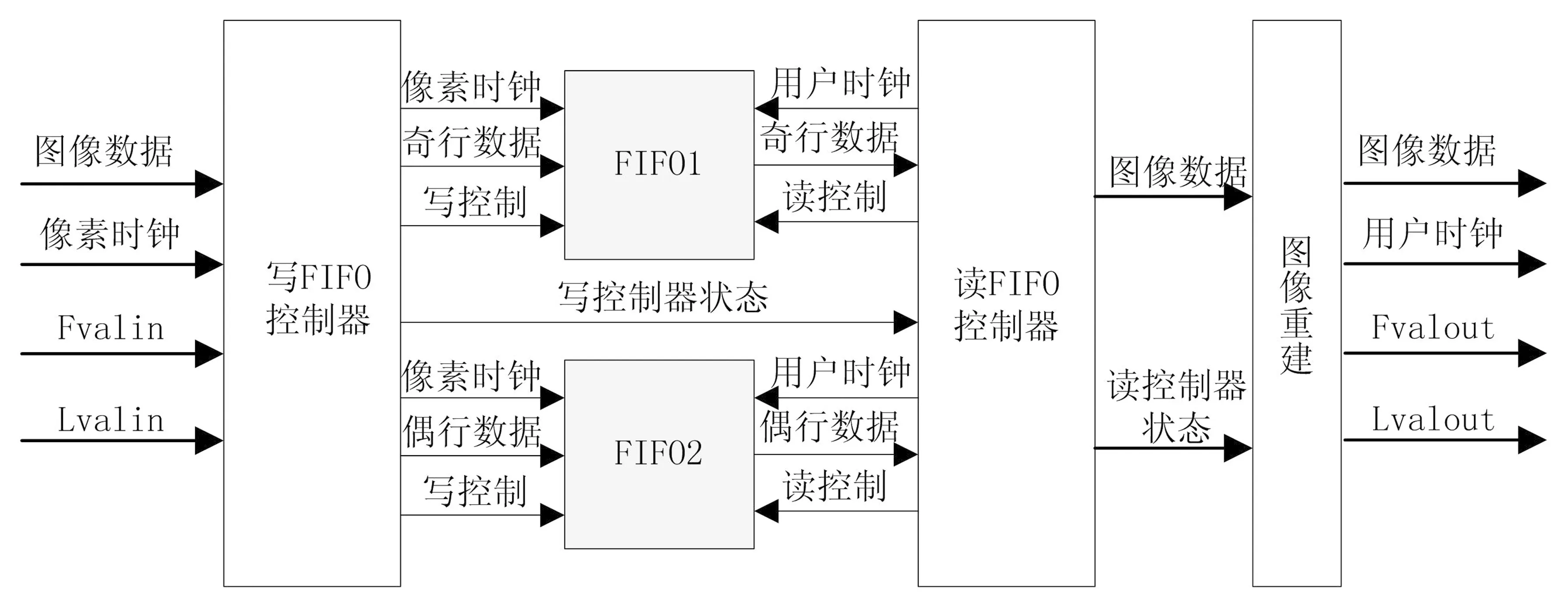

2.2.1 异步FIFO数据缓存

异步FIFO数据缓存是为了解决相机时钟域与Aurora协议用户时钟域的匹配问题。Aurora协议根据配置的工作时钟会产生固定的用户时钟,而不同的相机往往输出的像素时钟不同,两者之间存在时钟域不匹配的问题,所以本系统通过异步FIFO数据缓存来解决像素时钟域与Aurora协议用户时钟域的匹配问题。异步FIFO数据缓存原理框图如图3所示。

图3 异步FIFO原理框图Fig.3 Principle block diagram of asynchronous FIFO

异步FIFO首先在FPGA内部建立两个FIFO存储块,分别为FIFO1和FIFO2,写FIFO控制模块以相机输出的像素时钟作为FIFO的写入时钟,根据Fvalin和Lvalin同步信号将奇数及偶数行图像数据分别写入到FIFO1和FIFO2中。读FIFO控制模块根据写FIFO控制模块的状态及FIFO块的存储状态产生相应的读FIFO控制信号,以Aurora协议的用户时钟作为读时钟,读出的数据经图像重建后产生新的行场数据。

2.2.2 Aurora 8 B/10 B协议

Aurora协议是Xilinx公司针对高速传输开发的一种链路层协议[9],该协议可根据需要灵活的进行多通道绑定,扩展光纤链路数量,提高传输带宽,同时还能保证传输的高速同步和稳定。本系统采用Aurora 8 B/10 B协议,通过8 b/10 b的编码方式,实现并串转换的高速差分传输。具体实现过程是通过Xilinx公司开发的Aurora 8 B/10 B IP核,本系统中设置IP核的工作模式为4字节单通道流模式,传输的线速率为3.125 Gb/s,参考时钟为125 MHz,通过外部高精度的晶振产生,由FPGA专用的高速时钟引脚传入到IP核,以保证传输速率的稳定;IP核外部数据写入配置为32位的AXI接口形式。在发送端,可以直接将转换为AXI格式的并行数据写入到IP核的输入端,IP核自动完成8 b/10 b的编码,并完成并行数据到串行数据的转换,并通过GTX模块将串行数据通过差分信号传输到光模块;在接收端,IP核将GTX接收到的差分信号自动进行串并转换,并完成8 b/10 b的解码,以AXI的格式将解码后的并行图像数据输出,至此完成了由Aurora 8 B/10 B协议部分的单路数字图像数据的传输。由于本系统采用的是4路波分复用的光模块,多路图像的传输相互独立、互不影响,因此只需要复制单路图像传输的方法,分别对多路图像进行相应的处理,然后经光模块的不同通道传输即可。

3 实验结果及分析

为验证本文所设计系统的可行性及稳定性,进行了实验验证。为了验证多路图像的同时传输,在FPGA内部根据实际Cameralink相机的时序生成两路30 Hz的测试图,测试图的数据规律性变化,这样有利于调试。测试图1大小为1 024×768,每个像素由8 bit的RGB分量组成。每行图像像素值的变化相同,每行图像的第一个像素的RGB分量均从0开始,以后每个像素的RGB分量依次累加1;测试图2大小为640×512,每个像素位宽为8 bit,每行像素变化与测试图1相同。并通过编写误码率检测模块,检测接收端的数据误码率,由于测试图的每个位置上的像素固定,所以只需遍历每帧图像的像素值与生成的测试图像素值是否匹配,计数不匹配的像素个数即可得到每帧图像的误码率。通过FPGA内部的集成逻辑分析仪(ILA)对光纤传输前后的测试图数据进行分析,得到如图4所示的实验结果。

图4 测试图传输前后的数据Fig.4 Data before and after transmission of test image

由图4可知,两路视频接收端的测试图数据与发送端的测试图数据完全相同,由此可见,本系统接收端数据接收正确,能够正常的进行2路图像的收发数据。通过30 min的监测,共传输1.4×1012bit数据,2路误码率检测模块的计数结果均为0,未见误码,可知本系统传输的误码率低于10-12。在本文所设计的光纤传输系统的输出端利用采集卡采集2路测试图并显示,测试图传输前后的图像如图5所示。

从图5中2路测试图的原始图像及经过光纤传输后的图像对比可知,传输后的图像清晰稳定。

图5 传输前后的测试图Fig.5 Testimage before and after transmission

4 结 论

本文以FPGA作为核心处理器,设计了多路Cameralink数字图像的光纤传输系统。利用异步FIFO数据缓存、Aurora 8 B/10 B协议完成数字图像的编码、转换等功能,结合4路波分复用的光模块实现了多路数字图像的同时传输,最多可同时传输4路数字图像。实验结果表明,所设计的系统能够实现多路Cameralink数字图像的光纤传输,传输图像效果清晰稳定,传输通道误码率低于10-12,能够应用于多路Cameralink数字图像的光纤传输。