用MATLAB在FPGA芯片中实现数字下变频设计的研究

2019-09-10温浪明

关键词:MATLAB;FPGA芯片;数字下变频设计

中图分类号:TN791 文献标识码:A 文章编号:2096-4706(2019)06-0032-03

Keywords:MATLAB;FPGA chip;design of digital down converter

0 引 言

作為理想概念的软件无线电属于开放性极强的平台,构造一个软件控制的通用硬件平台是软件无线电的中心思想,本文研究的数字下变频属于软件无线电的核心技术之一。数字下变频器主要由三部分组成,即混频模块、抽取模块和滤波模块,其性能直接受到混频器和滤波器的影响。为了真正在应用FPGA芯片的数字下变频设计中引入MATLAB软件,本文研究主要围绕基于FPGA的数字控制振荡器设计(NCO)、积分梳状滤波器设计(CIC)、半带滤波器设计(HB)、FIR滤波器设计及仿真验证展开。

1 数字控制振荡器的设计与实现

1.1 基于FPGA的数字控制振荡器设计

数字控制振荡器的设计首先需要考虑设计方法的选择,为不占用系统的内存,本文选择CORDIC方法进行设计。为避免数字控制振荡器模块产生杂散,需保证其频率控制字为2的整数幂次方,这样才能满足整个系统的实际需求。

设计采用40MHz时钟,相位累加器位数N设置为32,为保证频率在1.5M左右且不产生杂散,频率控制字Δθ设置为227,输出频率如式(1)所示。

1.2 数字控制振荡器模块的验证与仿真

虽然数字控制振荡器设计在理论上满足了要求,但为了直观地验证其功能,需编写测试文件testbench,设置仿真软件simulation进行系统间调用。在完成仿真软件设置后,需选择调用的软件路径,最后打开simulation工具调用仿真。

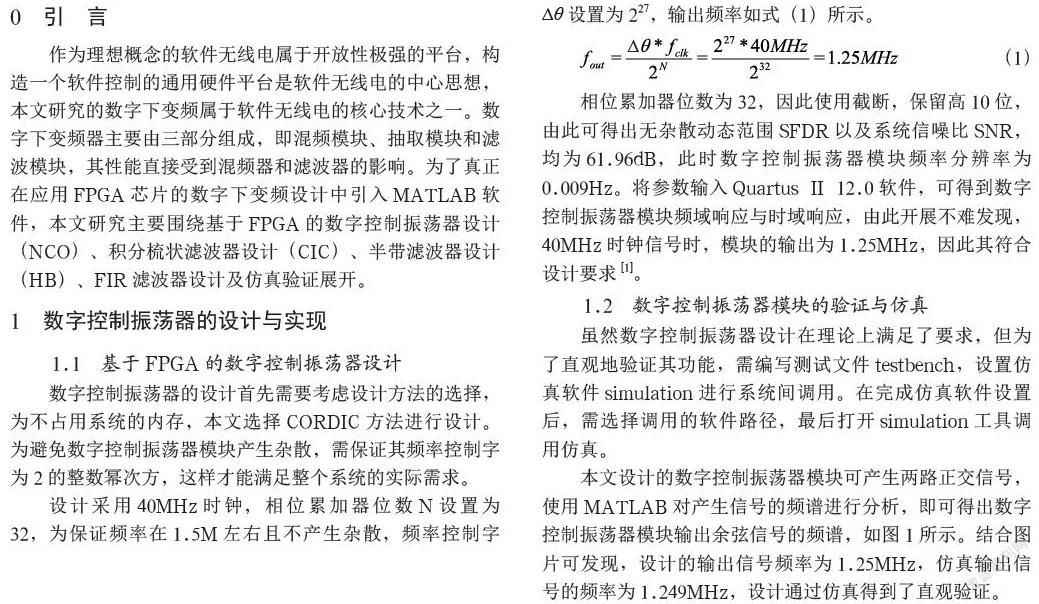

本文设计的数字控制振荡器模块可产生两路正交信号,使用MATLAB对产生信号的频谱进行分析,即可得出数字控制振荡器模块输出余弦信号的频谱,如图1所示。结合图片可发现,设计的输出信号频率为1.25MHz,仿真输出信号的频率为1.249MHz,设计通过仿真得到了直观验证。

2.1 基于FPGA的积分梳状滤波器设计

抽取滤波器组属于数字下变频的核心部分,其第一级抽取滤波器为积分梳状滤波器,且具备抽取因子较大、采样速率最大的特点,结合设计需要,本文计划设计5级8倍的积分梳状I抽取滤波器。本文设计规格积分梳状滤波器的第一旁瓣幅值衰减为67.3dB,因此将输入信号带宽设计为100kHz,结合0.02的带宽比例因子,模数转换芯片采用32MHz,由此可得出式(2)所示的积分梳状滤波器阻带衰减和式(3)所示的积分梳状滤波器通带衰减[2]。

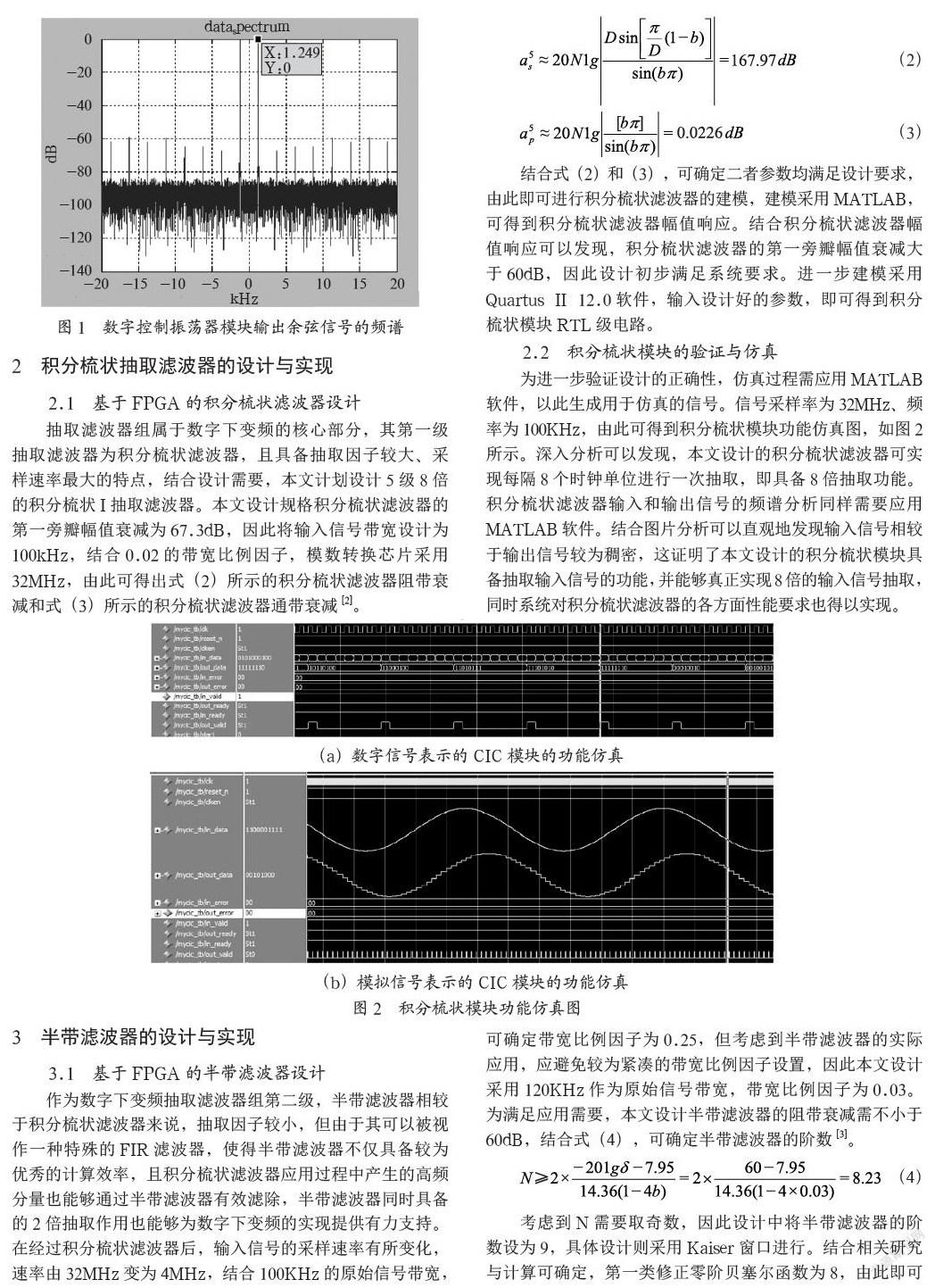

2.2 积分梳状模块的验证与仿真

为进一步验证设计的正确性,仿真过程需应用MATLAB软件,以此生成用于仿真的信号。信号采样率为32MHz、频率为100KHz,由此可得到积分梳状模块功能仿真图,如图2所示。深入分析可以发现,本文设计的积分梳状滤波器可实现每隔8个时钟单位进行一次抽取,即具备8倍抽取功能。积分梳状滤波器输入和输出信号的频谱分析同样需要应用MATLAB软件。结合图片分析可以直观地发现输入信号相较于输出信号较为稠密,这证明了本文设计的积分梳状模块具备抽取输入信号的功能,并能够真正实现8倍的输入信号抽取,同时系统对积分梳状滤波器的各方面性能要求也得以实现。

3 半带滤波器的设计与实现

3.1 基于FPGA的半带滤波器设计

作为数字下变频抽取滤波器组第二级,半带滤波器相较于积分梳状滤波器来说,抽取因子较小,但由于其可以被视作一种特殊的FIR滤波器,使得半带滤波器不仅具备较为优秀的计算效率,且积分梳状滤波器应用过程中产生的高频分量也能够通过半带滤波器有效滤除,半带滤波器同时具备的2倍抽取作用也能够为数字下变频的实现提供有力支持。在经过积分梳状滤波器后,输入信号的采样速率有所变化,速率由32MHz变为4MHz,结合100KHz的原始信号带宽,可确定带宽比例因子为0.25,但考虑到半带滤波器的实际应用,应避免较为紧凑的带宽比例因子设置,因此本文设计采用120KHz作为原始信号带宽,带宽比例因子为0.03。为满足应用需要,本文设计半带滤波器的阻带衰减需不小于60dB,结合式(4),可确定半带滤波器的阶数[3]。

考虑到N需要取奇数,因此设计中将半带滤波器的阶数设为9,具体设计则采用Kaiser窗口进行。结合相关研究与计算可确定,第一类修正零阶贝塞尔函数为8,由此即可应用MATLAB软件进行半带滤波器的建模分析,建模过程需应用软件的Filter Design&Anaiysis工具,由此即可得到半带滤波器幅值响应。结合半带滤波器幅值响应可以发现,本文设计的半带滤波器的阻带衰减能够较好地满足系统要求,同时软件的应用還能够获取半带滤波器9阶系数,应用Quartus II 12.0软件结合系数进行建模,可得到半带滤波器模块综合报告与RTL级电路。

3.2 半带模块的验证与仿真

为验证本文设计半带滤波器模块的正确性,需开展仿真验证,仿真验证过程用于半带滤波器模块输入信号选择积分梳状滤波器模块的输出信号。结合仿真可以确定,本文设计的半带滤波器模块实现了每隔2个时钟单位进行1次抽取,因此可认为本文设计的半带滤波器模块具备2倍抽取功能。值得注意的是,本文设计的半带滤波器模块同时存在一定延时,这类延时源于系统原因和寄存器的存在,但设计在总体上满足要求。为进一步验证设计,应围绕半带滤波器模块开展输入与输出信号的频谱分析,分析需应用MATLAB软件。结合分析可以发现,本文设计的半带滤波器的输入信号相较于输出信号较为稠密,这是由于半带滤波器具备抽取输入信号的功能,半带滤波器具备2倍抽取输入信号的功能由此得到了进一步确认,且系统对设计提出的多方面性能指数要求也得以实现。

4 FIR整形滤波器的设计与实现

4.1 基于FPGA的FIR滤波器设计

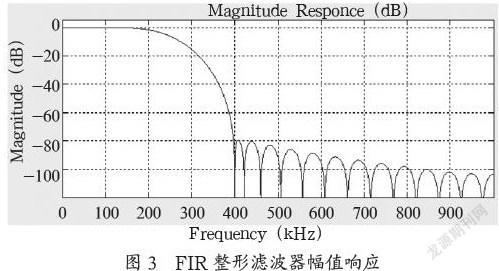

考虑到上文设计的半带滤波器本身属于较为特殊的低通滤波器,因此FIR整形滤波器的设计必须重点关注其数字下变频的最后一级身份。FIR整形滤波器采用与半带滤波器相似的设计思路,且设计需保证通带衰减、阻带衰减分别控制在0.1dB内和80dB内。FIR整形滤波器设计首先需应用Kaiser窗口,考虑到此类滤波器多具备阶数较大的特点,因此设计未采用第一类修正零阶贝塞尔函数。具体设计需应用MATLAB软件,通过应用Filter Design&Anaiysis工具和Kaiser窗口完成具体设计,选择Minimum order作为设计的阶数,同时设置fc、通带衰减、阻带衰减,分别为[0.1 0.4]MHz、0.1dB、80dB,由此即可通过设计得到34阶FIR整形滤波器幅值响应,如图3所示。

4.2 FIR滤波器模块的验证与仿真

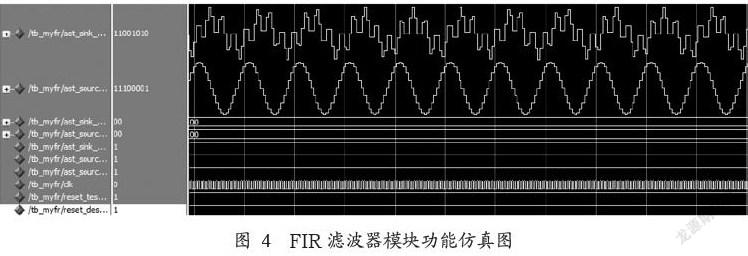

为验证本文设计的FIR滤波器模块的正确性,需应用正弦信号组成的复合信号进行仿真验证,信号由MATLAB软件产生,组成复合信号的正弦信号频率分别为0.1MHz、0.42MHz,仿真采用Modelsim,由此即可最终得到FIR滤波器模块功能仿真图,如图4所示。

结合图片可以确定本文设计的FIR滤波器模块能够有效滤除高频分量,且不对信号具有抽取作用,这使得FIR滤波器模块的整形滤波功能较为优秀,其设计效果能够较好地满足系统需要。

5 结 论

FPGA芯片实现数字下变频设计离不开MA TLAB软件的支持,在此基础上,本文基于FPGA的数字控制振荡器设计、积分梳状滤波器设计、半带滤波器设计、FIR滤波器设计及仿真验证,直观地展示了MATLAB软件在应用FPGA芯片的数字下变频设计中的应用路径,为了更好地发挥MATLAB软件的效用,FPGA器件的灵活方便、处理速度快的优势必须得到充分发挥,AD高速采样的应用同样需要得到重视。

参考文献:

[1] 薛金鑫,马崇鹤,周磊,等.4GS/s-12bitADC内置数字下变频器(DDC)的ASIC实现 [J].微电子学与计算机,2019,36(1):85-89.

[2] 杜兆凯,马宗方,谷卓.基于优化混频器的数字下变频系统的设计与实现 [J].液晶与显示,2018,33(11):943-949.

[3] 佟昕,于勇,赵宝珍,等.基于DMR-CED容错方法的多相结构数字下变频SEU防护设计 [J].遥测遥控,2018,39(4):54-59.

作者简介:温浪明(1986.06-),男,汉族,广东梅州人,中级职称,硕士,研究方向:数字集成电路设计。