基于VerilogHDL的LTC2308控制器设计

2019-09-10周俊秦工

周俊 秦工

摘要:根据AD转换芯片LTC2308的典型工作时序,针对应用设计了有限状态机,给出了用Verilog HDL实现其控制器的具体过程与方法,最后在ModelSim软件下进行了仿真并利用FPGA开发板DE10-Nano予以硬件实现。该控制器具有对LTC2308任一单通道快速访问及多通道自动刷新访问两种功能并能方便地和常用FPGA总线互连,适用于众多现实应用场景,充分发挥了AD转换器的性能,体现了FPGA的优点和灵活性。

关键词:LTC2308;AD转换器;Verilog HDL

中图分类号:TP331.2 文献标志码:A 文章编号:1008-4657(2019)06-0009-05

0 引言

LTC2308是亚德诺半导体公司(Analog Devices Inc,ADI)的一款低噪声12位高精度逐次逼近型模数转换芯片(Analog to Digital Converter,ADC),最多可拥有8个模拟输入通道,具有高达500 kSPS的采样速率以及一个兼容串行外设接口(Serial Peripheral Interface,SPI)。芯片内置有基准电压和一个可以减小共模噪声的全差分采样保持电路[1]。较低的功耗以及小巧的封装使其成为众多便携式设备、系统设计、FPGA开发板的ADC转换首选芯片。比如,业界被广泛使用的FPGA开发板DE10-Nano,由友晶公司为Intel Cyclone V FPGA芯片5CSEBA6U23I7NDK打造,即采用LTC2308作为标准配置[2]。另外,ADI公司自己推出的该芯片评估板DC1186A也被广泛用于各种开发系统,包括Xilinx和Intel公司的各种FPGA芯片开发板以及单片机、Arduino、树莓派(Raspberry)等。

ADC转换器及其控制电路作为联系模拟信号和数字系统必不可少的部分,其重要性已经不言而喻。利用硬件描述语言(Hardware Description Language,HDL)来设计ADC的控制系统,不但可以更容易了解ADC芯片的时序和控制方法,还能最大限度的发挥其性能,并方便于各种FPGA芯片上移植应用。本文通过对LTC2308的具体时序特点进行分析,采用Verilog HDL基于行为描述设计其控制器,并进一步以Intel的Avalon总线为例,封装成基于Memory Mapped的IP核,方便系统集成使用[3]。

1 LTC2308芯片及其时序特点

LTC2308的基本应用电路如图1所示[1],包含一个8选1模拟通道并能随时配置成为单端、差分式通道,以及单极性、双极性通道,通过四线式SPI/MICROWIRETM兼容串行接口与其他数字接口电路相连。当为单端输入时,每个通道相对于COM端,单极性状态下可以输入0~4.096 V的范围,双极性为± 2.048 V的范围,其中,负数是以2的补码形式表示。当为双端输入时,CH0与CH1、CH2与CH3、CH4与CH5、CH6与CH7可以分别构成差分对信号,能同时对双端信号进行采样以减小共模干扰。当输入源的阻抗较大时,需要的获取信号时间也会相应增多。

由于LTC2308采用的是SPI兼容信号与其他数字系统相连,所以如果支持SPI协议的设备与其进行通信并不复杂,但是要想充分发挥其性能特点,就需要具体分析其时序和功能,并针对性地实现对其控制。这里采用Verilog HDL在CPLD或FPGA上予以实现,不失为最佳控制方式之一,而且还具有更大的灵活性[4]。

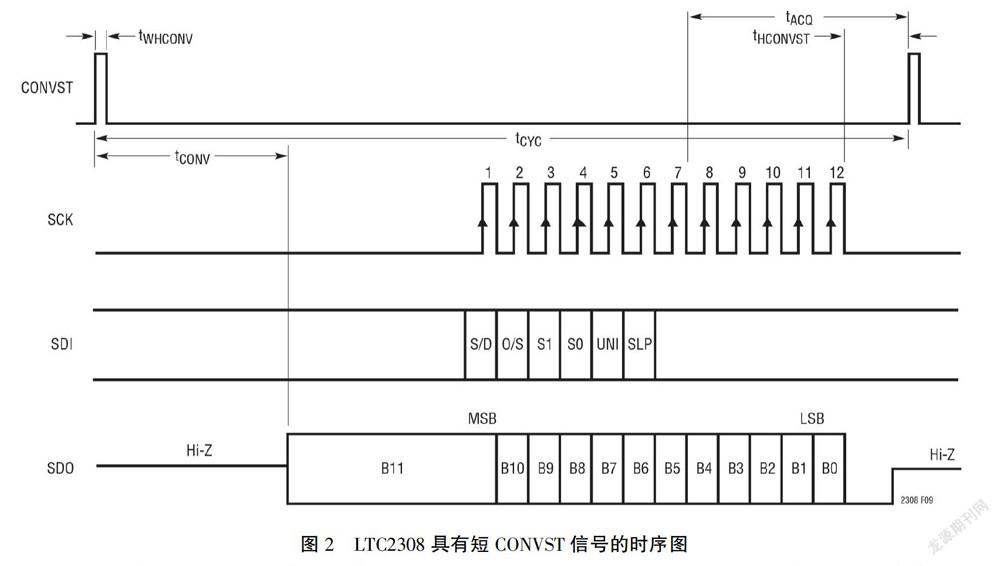

图2所示为LTC2308的典型时序图,CONVST信号的上跳沿将会启动转换,经过tCONV时間后转换完毕。tCONV典型值为1.3 μs,最大为1.6 μs[1],图2中CONVST信号在转换完毕后经过至少20 ns之后迅速变为低电平是为了获得更高性能。CONVST信号在40 ns内或者转换结束后马上回到低电平,能让芯片一直保持上电状态。当CONVST一直保持高电平时芯片会进入NAP或SLEEP节能状态,当在SLEEP状态时,需要200 ms来唤醒芯片。

转换完毕后,当CONVST变为低时,转换结果的最高位会出现在SDO引脚上。此时在SCK脉冲的上跳沿时将对LTC2308的控制数据通过SDI串行写入到芯片内,同时下跳沿时,依次由高到低输出12位转换结果,值得注意的是此时输出是上一次控制数据状态下的输出结果。SCK脉冲时钟最大为40 MHz,从时序图可以看到,如果设计控制器采样SDO的数据串行送入移位寄存器的最佳时刻也是在SCK上跳沿。

LTC控制数据为6位,由高到底依次为:S/D、O/S、S1、S0、UNI、SLP。S/D控制芯片是单端还是双端差分式模式。O/S在差分方式下,控制两个信号的正负极性,比如,当其为0时,CH0为+端,CH1为-端,当其为1时,则CH0为-端,CH1为+端。在单端模式下,O/S则和S1、S0一起构成通道选择信号。在双端模式下,S1、S0构成2位通道选择信号,正好可以选择四组差分通道。在单端模式下,S1、S0、O/S形成3位地址,可以选择8个通道。UNI为极性控制信号,其为1时,输出单极性信号,为0时,输出补码形式的双极性信号。SLP则是控制芯片是进入之前提到的SLEEP还是NAP状态。

在传输完第6位控制字之后,芯片还需要至少240 ns[1]的tACQ的获取时间之后才能再次将CONVST拉高来启动下一次转换。

以上即为LTC2308启动一次转换的基本过程,我们可以根据具体时序,结合芯片应用时的功能需求,设计控制器的有限状态机图(Finite State Machine,FSM),编写Verilog HDL代码予以实现[5]。

2 Verilog HDL实现

应用硬件描述语言在FPGA上定制实现LTC2308控制器时,我们必须根据其应用功能做以下考虑:

(1)LTC2308的8个模拟输入通道是通过多路选择器来复用其500 kSPS的高速转换器的,当同时使用8个通道时,分在每个通道上的采样速率只能达到最高转换速率的1/8。在许多应用场合下,我们并不需要始终都同时使用8个通道,因此为了达到最佳性能需要考虑在Verilog HDL程序中能方便的配置成单通道或者不同通道数进行使用。

(2)每次进行ADC转换时,都是基于前一次写入的控制字来进行的,所以在多通道和单通道应用中获取通道地址及对应结果的方法稍有不同。另外,在系统复位之后,第一次启动转换的同时获取的数据,因为没有控制字的控制,往往是无效的。

(3)当转换结束以后,应该能够给出指示信号供其他数字系统进行中断或者查询使用。

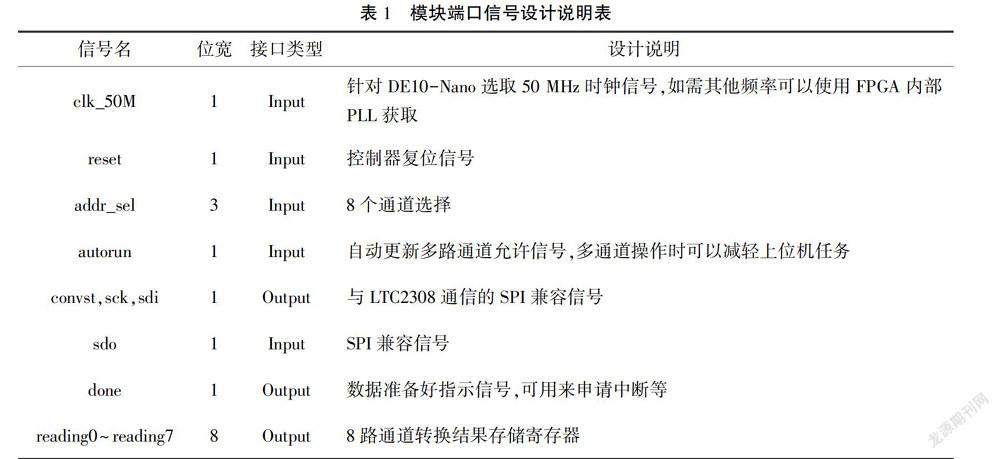

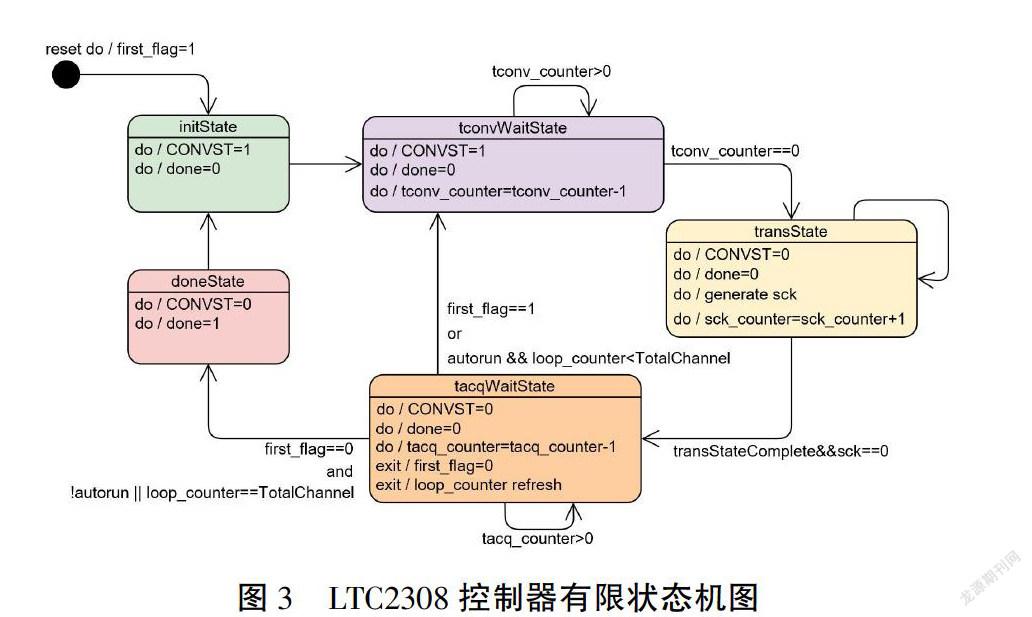

基于这些考虑我们设计了Verilog HDL模块ltc2308_ctrl,其端口及说明如表1所示,以及有限状态机图如图3所示。状态图共设置了5个基本状态,分别为:初始状态initState、转换等待状态tconvWaitState、传输状态transState、数据获取等待状态tacqWaitState、结束状态doneState。

针对状态机进行Verilog HDL编程时,按照一般FSM编程原则,将状态转换逻辑以及用于tconv、tacq定时的寄存器tconv_counter、tacq_counter逻辑、用于sck和通道循环的计数寄存器sck_counter、loop_counter逻辑等分别放在不同的always模块来实现[4]。根据系统时钟以及定时和计数需求确定寄存器位数和初值及计数终值。另外,设置TotalChannel参数方便程序针对不同应用场景下需求的通道数不同来进行修改。

3 系统仿真及Avalon MM总线封装

最终,我们硬件上选定Intel的Cyclone V FPGA芯片,采用友晶的DE10-Nano开发平台,结合Quartus Prime软件,用Verilog HDL实现了该控制器。图4为使用Modelsim软件进行仿真的部分结果,在图中,通过addr_sel信号选择通道1,autorun为低电平,为了简化,假定LTC2308的SDO输出为全1或全0,可以看到在transState状态下,产生了12个sck脉冲,此时sdi输出了6位二进制控制字110 010,并在第11个sck下跳沿后,reading1上获得12位输出4 095,紧接着下一次转换输出为0。

为了方便用Quartus Prime的Platform Designer将LTC2308和CPU连接起来,以上用Verilog HDL设计的控制器可以很方便的进一步用Verilog HDL封装成Avalon总线形式[3]。此时,控制器应该在CPU指令的控制之下才去启动一次转换,所以需要增加一个start启动信号,针对图3所示有限状态机图也需要稍作调整,在initState状态下,只有start信号有效才会进入转换状态,在转换结束后,出现done信号时,start恢复为0,下一次进行读写时,再次置位start信号。在进行Avalon MM总线封装时,主要是参考Avalon MM总线信号及时序标准,设计好address、read、readdata、write、writedata、waitrequest等信号即可[3]。另外在执行写入操作时,可以通过写入的数据来设置标志寄存器决定控制器是否进入到autorun模式。

图5为在DE10-Nano开发板上,通过FPGA内置软核CPU NIOS II控制,加载用Verilog HDL封装的IP核的演示效果,液晶屏上实时显示的通道1数据来自开发板自身提供的3.3 V电压,显示值为3 348 mV,右下角8位LED显示的是12位转换结果对应高8位二进制数11 010 001。

4 结论

ADC转换器作为电子系统设计中不可或缺的一部分,为了可靠的获取其数据,充分的发挥其性能,ADC转换控制器的设计非常重要。LTC2308是一款性能非常强大的8通道ADC转换芯片,采用Verilog HDL来设计其控制器,不但能充分发挥其性能,并具有非常强的灵活性,还能很方便地封装成各种标准总线接口IP核供CPU使用。通过仔细分析时序图,考虑应用场景,设计好有限状态机转换图,能使得用Verilog HDL开发ADC控制器变得比较容易。

参考文献:

[1] ADI.LTC2308 Datasheet[A/OL].(2008-10-18)[2019-11-06].https://www.analog.com/media/en/technical-documentation/data-sheets/2308fc.pdf.

[2] Terasic Inc.DE10-Nano User Manual[A/OL].(2018-11-15)[2019-11-06].http://www.terasic.com.cn/cgi-bin/page/archive_download.pl?Language=China&No=1048&FID=0898a024b81caf1f3a95b241eeeb6f66.

[3] Intel.Avalon Interface Specifications[A/OL].(2018-09-26)[2019-11-06].https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/manual/mnl_avalon_spec.pdf.

[4] Tatiana M L D R,Luz N O M,Antonio G J G.Implementation of the Communication Protocols SPI and I2C Using a FPGA by the HDL-Verilog Language[J].2014,75:31-41.

[5] 王金明.數字系统设计与Verilog HDL[M].第6版.北京:电子工业出版社,2016:195-214.

[责任编辑:郑笔耕]