沟槽栅FS-IGBT HTRB失效的调查分析

2019-09-10梁赛嫦史波江伟敖利波

梁赛嫦 史波 江伟 敖利波

摘 要:IGBT作为功率转换、功率控制的新型器件,已广泛应用于变频空调、电磁炉、电饭煲等产品。鉴于成本压力,在通流能力保持不变的前提下,IGBT将变得更小更薄。工艺上不论是给晶圆代工厂还是封装代工厂,都是极大地挑战。本文主要通过对沟槽栅FS-IGBT芯片封装后,HTRB上机时出现漏电增长的问题进行调查分析,澄清在芯片设计不变的前提下,找出HTRB失效的解决方法。

关键词:沟槽栅FS-IGBT;HTRB;漏电检测

中图分类号:TN322.8 文献标识码:A 文章编号:2096-4706(2019)09-0025-05

0 引 言

IGBT(Insulated Gate Bipolar Transistor),又称绝缘栅双极型晶体管,可以简单地看成为一个电路开关,导通电压达几百伏,甚至上千伏,电流几十到几百安培,为弱电控制强电的功率器件,而沟槽栅FS-IGBT(Field Stop,场截止)具有通态损耗低,通流能力强等特点,广泛应用于消费电子、白色家电、汽车电子等消费领域。

因IGBT工作在高压大电流高温的严苛环境下,且所代表的产品更新换代周期较长,所以IGBT流入市场前必须经过严格的可靠性验证。

HTRB(High Temperature Reverse Bias,高温反偏试验)为验证IGBT芯片性能最为关键的可靠性试验,具体实验方法是在IGBT结温条件下,施加最大反偏电压的80%或100%,在电和热应力的作用下,监控集电极和发射极漏电情况。

沟槽栅FS-IGBT晶圆厚度较薄,一般在70-100μm左右,且大小为8寸,不论是晶圆流片,还是封装加工,在工艺实现上都是挑战。

本文主要对沟槽栅FS-IGBT做HTRB可靠性试验时出现漏电急剧增长的问题展开调查分析,先从封装代工环节切入,逐一排查,再从晶圆流片工艺角度进行分析,以找到影响HTRB漏电问题的关键因素,从而推动产品研发进度。

图1为产品焊线图,以此原型进行封装分析。

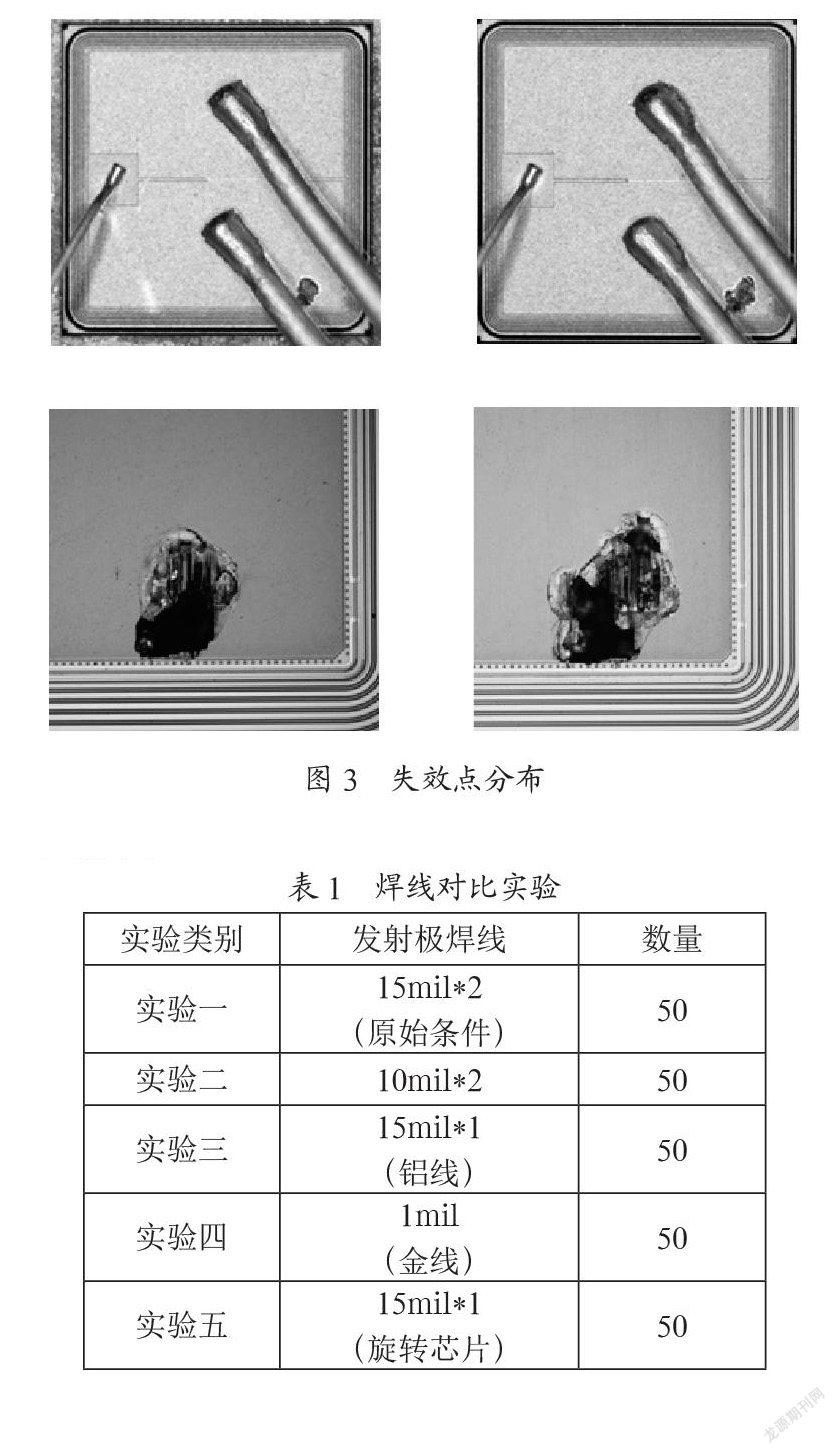

图2HTRB漏电曲线图横坐标单位为时间小时(h),纵坐标单位为电流微安(μA)。从图中曲线可看出,漏电在极短时间内急剧上涨后跌为零,表明产品已被击穿,产品下机,FT失效。抽取样品进行开封分析,发现失效点带有规律,均在焊线下方芯片右下角附近。如图3所示。

1 焊线应力对可靠性影响分析

根据以上基础数据,初步推断失效可能跟焊线应力对芯片造成的损伤有关,安排实验验证,看问题是否重现。

实验中分别从减小线径,减少焊线数量,改变线材及旋转芯片四个方面与原始条件作对比,减少线径、焊线数量的目的为降低应力对芯片的影响;铝线变更为金线,其焊线工艺基本不一样,可判断是否为焊线工艺的影响;旋转芯片,主要看如果产品失效,失效点是仍在芯片右下角,还是会随着焊点而发生转移,或是由于其它工艺原因导致的失效。如表1所示。

由漏电曲线图4可看出,不管哪种实验,HTRB漏电仍然是短时间内骤增后降为零,器件烧坏。抽取樣品开封分析,如图5所示,失效点位置存在飘移,不再在焊线区域右下方,而是随机分布,证明本实验并没有根本解决HTRB漏电骤增问题,从而得出焊线过程导致的HTRB失效为小概率事件,关键因素需进一步澄清。

2 上芯过程对可靠性影响分析

对问题进行拓展,是否在焊线前就已存在芯片异常,因FS型IGBT芯片较薄,上芯过程如果按一般芯片的方式进行作业,容易导致芯片发生裂片。对于超薄芯片,采用特殊顶针座,顶针在4根以上,保证受力均匀,生产过程保证空洞、BLT、结合材覆盖率、翘片数据等均在规格范围内,产品全检后再进行焊线、塑封等制程。之后,安排可靠性试验,结果如图6所示,漏电同样骤增,与原始结果基本一致,问题没有解决。

为验证产品失效是否由于上芯过程导致芯片可能存在的暗裂(因暗裂不容易被检出),故而采取恶化实验来辅助,对同批次产品进行TCT 168cylces(温度循环实验),TCT前后FT均pass,表示产品无暗裂风险。

以上实验表明上芯过程没有出现异常,但HTRB同样出现漏电剧增现象,根本原因需要进一步排查。

3 封装材料对可靠性影响分析

因为第一次开封的产品失效点带有规律性,而第二次及后续实验的开封,失效点又变得没有规律,可能原因为样品量不足导致的误判。排除封装上芯及焊线工艺因素,从结合材和塑封料进行分析,封装过程导致失效的原因主要有以下几点:

(1)上芯过程,结合材不均匀,接触面存在空洞;

(2)塑封过程,塑封料填充不满,导致在高温条件下,空洞膨胀,造成芯片损伤,同时两端接高压,在芯片最薄弱处发生击穿失效;

(3)塑封料与芯片不匹配,导致应力得不到释放;

(4)由于环境或人为因素(湿气、沾污等),芯片或框架处出现塑封分层。

为证实以上所列怀疑点,在上芯和焊线条件保持不变的前提下,安排5组实验进行对比验证,如表2所示。

实验一为原始封装条件,实验二和实验三塑封料分别从A更换为塑封料B和C,实验四更换为结合材B,实验五使用金属封装,不需进行塑封制程,从根本上判断漏电是否跟塑封料有关。

对以上实验先进行首件检验,确保制程没有异常。进行C-SAM及X-ray扫描,结果如图7和图8所示。可以看出,封装过程并没有出现异常,分层及空洞比例均在规格范围内。

从图9的实验四看,结合材对漏电曲线影响不明显,主要表现为漏电太大,已到设备保护界限,设备反复降压后电流再次极速上涨,实验无法继续,下机处理,与原始条件对应的结果基本一致,器件烧伤失效。而实验二和实验三,塑封材料对HTRB漏电结果影响较大,短时间内的烧伤问题得到解决,但漏电趋势随着时间推移而不断增大,可看出塑封料对HTRB漏电改善明显,但仍未能根本解决问题。金属封装整个封装过程与塑封工艺不一致,结果同样出现漏电增大现象,此条件已基本可排除塑封料导致的HTRB失效。

综合以上分析,在封装制程方面已基本调查清楚,但其非导致HTRB漏电失效的根本原因,需同时从晶圆流片角度(包括正面及背面工艺)进行分析。

4 晶圆厚度对可靠性影响分析

场终止(FS)结构,需要对硅片背面进行减薄,而IGBT减薄工艺为晶圆代工厂比较核心的关键技术。晶圆表面设计结构保持不变,正面工艺制程完成后,背面不进行减薄,以验证是否由晶圆背面工艺导致的HTRB失效。此晶圆流片出来后按最开始的封装条件完成封装,曲线如图10所示。

图10 晶圆不减薄封装后的HTRB漏电曲线图

超薄IGBT虽然给晶圆厂或封装厂带来工艺难题,但从图10结果可看出,晶圆厚度或晶圆减薄工艺并不是使HTRB失效的主要原因。

5 晶圆正面工艺对可靠性影响分析

排除前三种原因,对正面结构进行分析。沟槽栅FS-IGBT器件形貌结构分元胞区和终端区两种,元胞结构主要由栅极、层间绝缘层、接触孔、金属集电极和钝化层等组成,终端结构由复合场限环、复合场板、层间绝缘层和钝化层构成。形貌结构对IGBT的性能和可靠性有着至关重要的影响。

对不良品的接触孔进行FIB(Focus Ion Bean)分析,发现部分开孔没有打开,对CT(Contact) layer进行FEM(Focus Energy Matrix,焦距能量矩阵)确认,由于CT处台阶高度及所处位置有差异,导致CT的曝光结果有差异。因此,若不进行CT改版,通过减小poly的厚度,降低台阶高度,同时确保沟槽栅填充完整,BPSG增加B/P浓度,改善形貌平滑度,增大注入剂量及CT曝光量,令通孔全部打开,如图11所示。

以下为改善后的HTRB漏电曲线图,如图12所示。可以看出,HTRB實验已进行300小时,漏电一直保持6μA左右,没有出现之前的短时间内漏电骤增,产品失效等现象。产品下机、FT pass、HTRB问题得到根本性解决。

6 结 论

本文通过对HTRB漏电骤增问题展开调查分析,分别从封装代工及晶圆流片工艺两个角度进行分析,得出两个关键点:封装塑封料对HTRB漏电曲线改善明显,但随着时间推移,器件同样会发生失效,不能根本解决漏电增长问题;晶圆工艺上的缺陷与IGBT的HTRB结果有强相关性,只有找出失效位置,排查晶圆流片制造过程出现的异常,保证晶圆流片出来的形貌及尺寸满足设计仿真结果,才能确保芯片性能。

参考文献:

[1] 董少华,刘钺杨,何延强,等.HTRB试验方法及现象研究 [J].智能电网,2016,4(12):1200-1203.

[2] 张金平,赵倩,高巍,等.IGBT新技术及发展趋势 [J].大功率变流技术,2017(5):21-28+41.

[3] 张满红,邹其峰.沟槽式FS-IGBT各部分对其性能的影响研究 [J].现代电子技术,2018,41(14):5-9.

[4] 黄建伟,杨鑫著,刘根,等.沟槽栅IGBT关键技术研究 [J].大功率变流技术,2015(2):57-61.

[5] 张景超,赵善麒,刘利峰,等.绝缘栅双极晶体管的设计要点 [J].电力电子技术,2010,44(1):1-3+16.

作者简介:梁赛嫦(1989.09-),女,汉族,广东江门人,功率半导体产品开发工程师,学士,研究方向:封装工艺研究、产品导入、封装制程失效分析。