人体心电信号数字处理及控制模块的SOPC设计*

2019-09-07左右清

李 鸿,左右清

(湘潭医卫职业技术学院,湖南 湘潭 411102)

0 引言

心电信号(Electrocardiogram,ECG)数字处理及控制模块是心电监护仪的重要组成部分,实现ECG的滤波、储存、回放、通信和显示等数字处理及控制。目前大多采用DSP+MCU或DSP+ARM的双CPU结构设计,通过编写复杂的程序实现模块的功能。其协同性差、稳定性低,运算速度慢,分析时响应不高,影响诊断结果的准确性,不易执行复杂的心电信号分析算法,同时,随着模块功能实现的增加,硬件设计更加复杂,软件编写烦琐,体积庞大,研制成本提高[1],与产品微型化、多功能化和低功耗要求相背。

本研究旨在用FPGA(Field Programmable Gate Arrary)“片上系统”结构来取代目前心电监护仪所采用的DSP和MCU或ARM微处理器双CPU结构,实现对ECG信号的数字处理和控制。FPGA是在硬件上实现全部控制逻辑,比MCU或DSP的软件处理速度快,实时性好,效率高。同时FPGA支持NiosⅡ嵌入式软核处理器,对各种算法的实现和数据的处理能力大大增强。其次,基于SOPC的FPGA系统设计具有研制周期短、制作成本低,可靠性高,特别是可以很方便地对设计进行在线修改,同时器件少、功耗低,很适应可穿戴设备和移动医疗的需要。

1 ECG数字处理及控制模块架构

ECG数字处理及控制模块基于FPGA芯片EP2C35F672C6N构建,接收A/D转换输出的数字ECG信号,对信号再次除杂,分析处理并存储,实现与各个接口间的通信,包括AD控制器、心率处理器、FIR(Finite Impluse Response)滤波器以及寄存器编码等子模块。

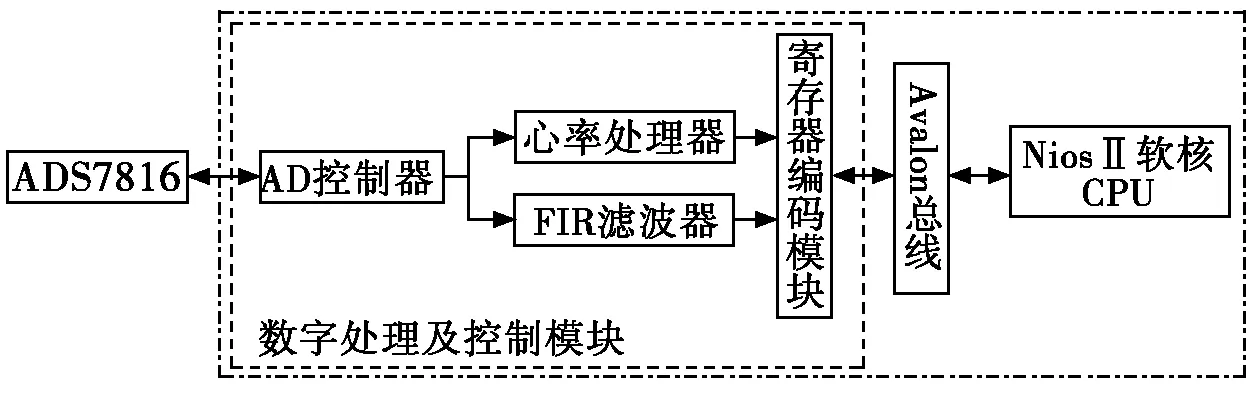

首先,在FPGA内部定制1个NiosⅡ软核处理器,实现总体控制,上述子模块通过寄存器编码子模块挂载到Avalon总线上作为NiosⅡ系统的外设,并采用统一的同步时钟,构成一个基于32位嵌入式NiosⅡ软核CPU的嵌入式系统,实现信号的采集、处理、回放、存储和显示功能。总体框架结构如图1所示。

图1 模块整体结构框图

NiosⅡ软核处理器采用Avalon交换式总线[2],通过Avalon总线控制心率处理器、FIR滤波器等子模块对输入的ECG进行数字滤波和心率检测,得到信噪比更高的数字心电信号,转换成可视波形和数据放入寄存器模块中存储。同时,通过对寄存器的设置或读取,直接获得心率大小、心电波形缩放系数等心电信息的相关数据,进而实现心电信号的实时显示、远程传输,用于分析和诊断。

2 ECG数字处理及控制模块设计

模块设计采用软硬件协同设计的思想,在FPGA上采用SOPC定制IP核技术单独完成各个子模块的设计,实现相关逻辑功能,再将各个子模块整合在一起形成一个系统,达到对数字ECG的处理与控制,CPU采用Altera公司提供的NiosⅡ软核处理器,本设计在QuartusⅡ9.0版本下完成。

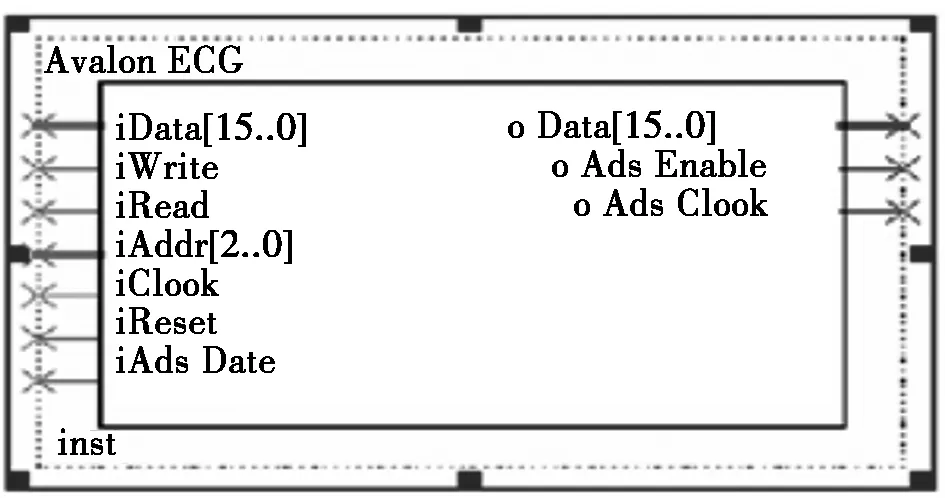

图2为ECG数字处理及控制模块在QuartusⅡ9.0开发软件中设计生成的封装效果图。iDATA为从CPU发出的16位数据输入,iWrite和iRead是CPU控制ECG模块进行写、读操作的使能信号,iAddr为寄存器偏移地址,CPU通过发送偏移地址获取存储在该地址内的内容,iClock和iReset为ECG控制模块的时钟信号和复位信号,iAds Data是从ADS7816采集到的数据;oDATA为输入到CPU的16位数据输出,oAds Enable和oAds Clock为控制ADS7816进行采样的使能信号和时钟信号。

图2 ECG控制器模块

2.1 A/D转换控制器设计

AD控制器根据ADS7816芯片的时序要求,输出控制信号实现对ADS7816的模数转换控制、时钟分频,同时接收ADS7816输出的12位串行数字信号数据,通过串/并转换,实现12位并行数字信号数据的输出至数字滤波和心率检测子模块。

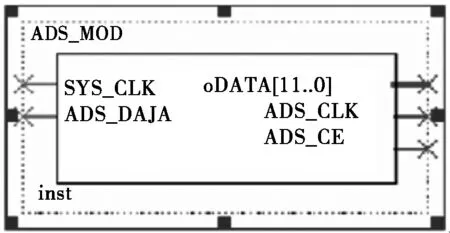

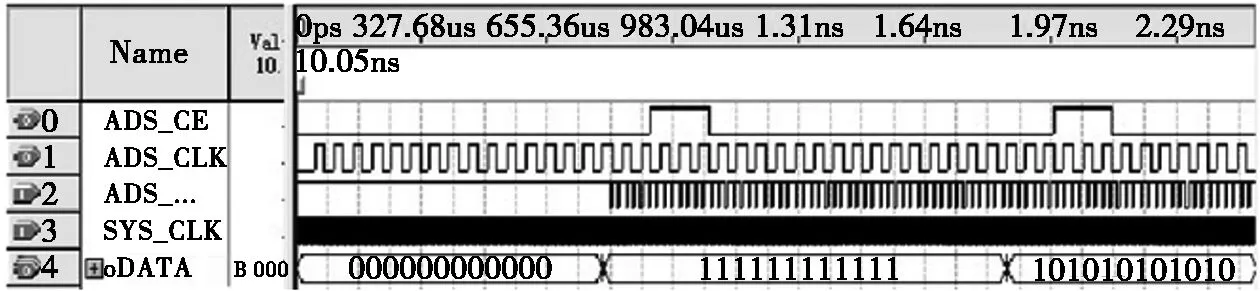

AD控制器的封装效果如图3所示,行为仿真如图4所示。ADS_DATA为ADS7816输出的12位串行数据输入,oDATA为12位的并行数据输出,SYS_CLK为系统时钟,ADS_CLK和ADS_CE为用于ADS7816采样控制的时钟信号和使能信号。根据心电信号的采样要求,AD控制器设计的主要参数为:系统时钟为50MHz,通过模块内分频电路将采样时钟设定为20 kHz,采样频率设为1 kHz,每20个时钟周期采样一次,其中17个时钟周期为数据采集时间,剩下的3个时钟周期为复位时间。从仿真图可以看出AD控制器准确产生了时钟信号ADS_CLK、使能信号ADS_CE,并且ADS_DATA串行输入数据经过串并转换后能准确的并行输出。

图3 AD控制器

图4 AD控制器行为仿真图

2.2 FIR数字滤波器的设计

数字滤波器实现对ECG信号的数字滤波,滤除模拟带通滤波器(通频带为0.05~100 Hz,消除基线漂移和电路内部噪声干扰)很难滤除在ECG频率范围内的50Hz工频干扰,得到更为精确的ECG信号,同时,通过波形转换程序,将数字信号转换成波形输出。工频干扰是影响比较显著的噪声之一,由50 Hz市电电压及其谐波构成的一种固定干扰,与心电信号的频带重叠,影响心电信号分析,严重的甚至会淹没有用的信号,因此必须采取一定的方法和措施加以抑制。根据数字滤波器冲激响应的时域特征,可分为FIR滤波器和IIR(Infinite Impluse Response)滤波器。IIR滤波器计算量小,幅频特性精度高,但它的相位是非线性的,应用于能够容忍相位失真的系统中。FIR滤波器计算量较大,幅频特性的精度较低,但相比于IIR滤波器具有严格的线性相位,没有相位失真,系统稳定,同时它的单位响应也有利于对数字信号的处理,便于编程,计算时延也小,在便携式和低功耗的背景下容易实现。考虑到ECG信号对滤波器相位的线性有要求,结合FIR数字滤波器的优点,我们选用FIR数字滤波器中的带阻滤波器为ECG信号进行49~51 Hz带阻滤波,滤除其中50Hz的工频信号。FIR数字滤波器常用的设计方法有窗函数法、频率采样法和等纹波最佳逼近法等[3]。综合三种设计方法的优缺点及设计带阻滤波器的目的,考虑到窗函数法设计比较简单,实现的性能完全可以达到设计要求,同时由于带阻滤波器要求过渡带尽量的窄,可以快速的从通带到阻带。因此选择窗函数法下的矩形窗来设计FIR数字滤波器。目前,FIR滤波器的实现常采用设计优化好的FIR滤波器IP核,采用IP核的方法可以保证性能,极大地缩短设计时间[4],用户使用这种IP核,根据实际需要进行简单的开发即可,Altera公司提供了FIR滤波器的IP核,所以该数字滤波器的实现采用Altera公司提供的FIR滤波器IP核,采取一种基于DSP Builder的FPGA设计方法[5]。首先利用MATLAB中滤波器设计工具FDAtool工具设计FIR滤波器系数,再利用Matlab中的Simulink库文件下的DSP Builder库中的各个模块搭建FIR滤波器系统,然后在Simulink里进行了仿真,并编译生成VHDL语言,再通过QuartusⅡ软件对生成的VHDL程序进行编译和仿真,并利用Matlab对仿真结果进行了分析,证明所设计的FIR滤波器功能的正确性,最后实现硬件系统。其设计界面如图5所示。

2.3 心率处理器的设计

心率处理器对心率进行计算。经过滤波后的ECG数据可准确地进行R波的检测,进而计算心率。心率的计算通常是通过计算相邻两个R波峰值之间的时间间隔求出RR间期来得到(两个R波之间的间隔即为一个RR间期)[6]。计算公式:心率=60/RR间期。然儿在少数异常波形中,T波的幅值会超过R波,如果把T波误判为R波来进行心率计算,则会产生很大的误差。为了在心率计算时消除T波可能引起的干扰,考虑到R波通常位于0~33 Hz的频率范围内,而T波位于0~9 Hz的频率范围内[7]。因此,我们设计了一个中心频率f0=12.867 Hz,带宽B=f0/Q=5.629 Hz,下限截止频率f1=10.356 5 Hz,上限截止频率f2=15.985 5 Hz的带通滤波器,首先将ADS控制器输出的12位并行ECG信号通过带通滤波器,以获取信噪比比较高的QRS波群信息,然后通过采样(初始采样频率设为100 Hz)计算得出瞬时心率,输出到寄存器中。

图6为3输入2输出心率计算模块封装效果图。ADSDATA为并行12位的ECG信号输入端,连接到AD控制模块的数据输出端;iCLK为模块的时钟控制信号,输入的是AD控制模块的采样频率,即为1 kHz;RST为复位端;ODATA为26位的信号输出,在进行波形显示时,只取高16位作为波形输入的数据,ORATE为心率输出。

2.4 寄存器编码模块的设计

寄存器编码模块实现对心率处理器和FIR滤波器输出的数据进行编码,将这些数据放在指定地址的寄存器中方便CPU的读取或设置。我们为ECG控制器设置了3位地址宽度寄存器,占用8个地址空间,每个偏移地址对应具体的功能,如偏移地址“0”对应寄存器功能“输出波形缩放系数”,偏移地址“1”对应寄存器功能“输出波形Y轴偏移量”……。CPU通过发送偏移地址来获取存储在该地址内的内容。

3 结语

基于FPGA的心电信号数字处理与控制模块利用其高速并行处理数据的能力实时地对信号进行处理。模块设计采用软硬件协同设计的思想,在QuartusⅡ开发环境中,通过硬件描述语言(VHDL)或采用SOPC定制IP核技术完成AD控制器、心率处理器、FIR滤波器以及寄存器编码等子模块的设计,实现相关逻辑功能。该模块研制周期短,成本低,精度高、体积小、功耗低,具有较好的实用性和可扩展性,特别适应可穿戴设备和移动医疗的需要。