基于VHDL 语言的电子秒表设计

2019-09-07高皑琼甘肃工业职业技术学院

高皑琼 甘肃工业职业技术学院

引言

电子秒表在很多领域充当着重要的角色,尤其在各种比赛中对秒表的精度要求很高。以往的电路多选用单元电路来实现,采用传统的“自底向上”设计方法,其设计主要依赖设计者的经验与技巧,这种方式设计成本高,效率低。本设计采用EDA 技术,以VHDL 语言为系统逻辑描述,自动完成由软件描述系统到硬件电路的实现。整个设计“自顶向下”完成功能模块的划分,各模块相对独立。可以对各模块单独进行设计、调试和修改,极大地减少了设计人员的工作量,更提高了设计的灵活性和可靠性。

1 设计思路及模块划分

1.1 设计思路

秒表实际上是一个对标准脉冲信号(1HZ)进行计数的电路,能够精确反映计时时间。在此过程中具备启动、暂停、复位等功能,使其真正具有实用功能。秒表计时的最大范围为1 小时,精度为0.01 秒,当按下暂停按键后,由显示电路显示计时时间。

1.2 模块划分

电子秒表的设计模块主要包括分频器、计数器电路、控制电路、报时电路和译码显示电路等。其中,计时电路和控制电路是系统的主要部分,计时电路完成对秒脉冲信号的计数功能,而控制电路具有直接控制计数器的清零、启动计数、停止 3 种状态的功能。

(1)计数器模块主要完成对时钟信号的精确计时。其实质是对有分频器输出的秒脉冲信号(频率为1HZ)进行计数,通过计数完成计时。秒、分部分为60 进制计数,即从0 到59 循环计数,计至59 分59 秒时归零。计数结果通过译码显示部分显示,即所计时间值。

(2)控制电路可产生 3 个控制信号,分别用作电子秒表的清零、计时、停止 3 种状态。

(3)由石英晶体振荡器产生频率很高的脉冲信号,经分频电路分频生成 1Hz 标准秒脉冲信号和100Hz 的音频信号,同时满足计数电路和报时电路的需要。

(4)译码显示模块为译码驱动电路和数码显示电路,可以将测得的数值转换成能在数码管上显示的数字,方便读取结果。

(5)报时电路,当计时电路计到 59 秒时,产生一个报时信号,蜂鸣器报时。产生“滴答,滴答”的报时声。

2 电子秒表的部分VHDL 程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY mb_60 IS

PORT( en,Reset,clk: IN STD_LOGIC;

co: OUT STD_LOGIC;

led1: OUT STD_LOGIC_VECTOR(6 DOWNTO 0);

led10: OUT STD_LOGIC_VECTOR(6 DOWNTO 0));

END mb_60;

ARCHITECTURE S_watch OF mb_60 IS

COMPONENT count_60_2

PORT( en,Reset,clk: IN STD_LOGIC;

counter1: OUT STD_LOGIC_

VECTOR(3 DOWNTO 0);

counter10: out STD_LOGIC_VECTOR(3 DOWNTO 0);

co: OUT STD_LOGIC);

END COMPONENT;

COMPONENT encoder_7_2

PORT( d:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

y:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));

END COMPONENT;

COMPONENT fenping

PORT( clk: IN STD_LOGIC;

clk_out: OUT STD_LOGIC);

END COMPONENT;

SIGNAL x:STD_LOGIC;

SIGNAL y,z:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

U0: fenping PORT MAP(clk,x);

U1: count_60_2 PORT MAP(en,Reset,x,y,z,co);

U2: encoder_7_2 PORT MAP(y,led1);

U3: encoder_7_2 PORT MAP(z,led10);

END S_watch;

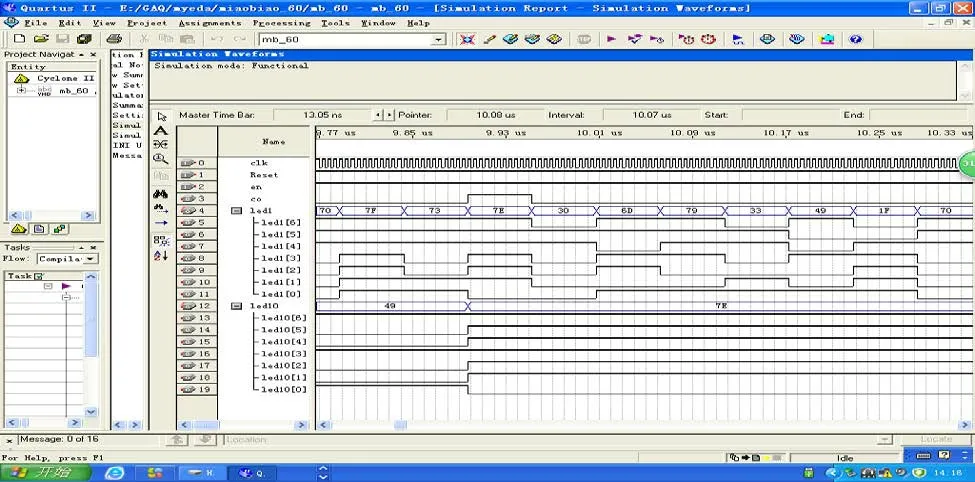

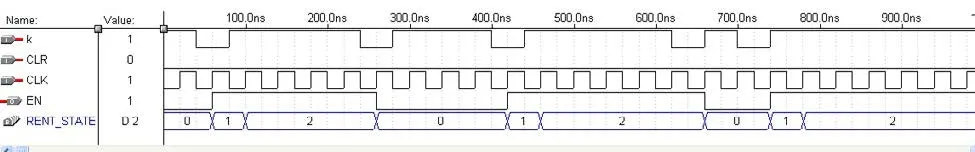

3 部分时序仿真图

3.1 计数器模块仿真图

3.2 控制电路仿真图

4 结束语

EDA 技术的应用实现了电子设计自动化,使得数字电路的设计变得更加灵活、简捷、高效。不仅极大的减轻了设计人员的工作量,提高了工作效率,更缩短了产品开发的周期。