基于软件无线电的通信系统实验平台研制(4)

——射频电路

2019-09-03戴伏生

戴 伏 生

(哈尔滨工业大学(威海) 信息与电气工程学院, 山东 威海 264209)

0 引 言

基于类似Unix操作系统但可自由免费使用的开源无线电软件(GNU's not Unix Radio, GNU Radio)[1]研制的无线通信系统实验平台,分为主板和射频子板。主板本质上是一个无线电通信的中频处理及其管理系统[2-3]。射频子板需配合主板才能工作,它主要任务是完成无线物理信号的发/收、中频和射频的频率调制/解调等工作。若要利用实验平台构建一套完整的软件无线电实验系统,采用“上位机+主板+射频子板”积木形式的组合,所以射频子板是实验系统组成不可缺少的无线信号收/发功能单元。采用市场上为通用软件无线电外设(Universal Software Radio Peripheral, USRP)配套的射频子板,可以完成一些常规的实验内容[4-6]。通常购买的射频子板只能获得产品使用说明书,无法获得其核心技术以及主板管控射频子板等方面的资料,难以开发出有特色的高级创新型实验。因此,有必要研制一款核心技术公开,适合软件无线电教学实验平台的射频子板。

1 软件无线电实验平台的射频子板

1.1 射频子板模块化设计思想

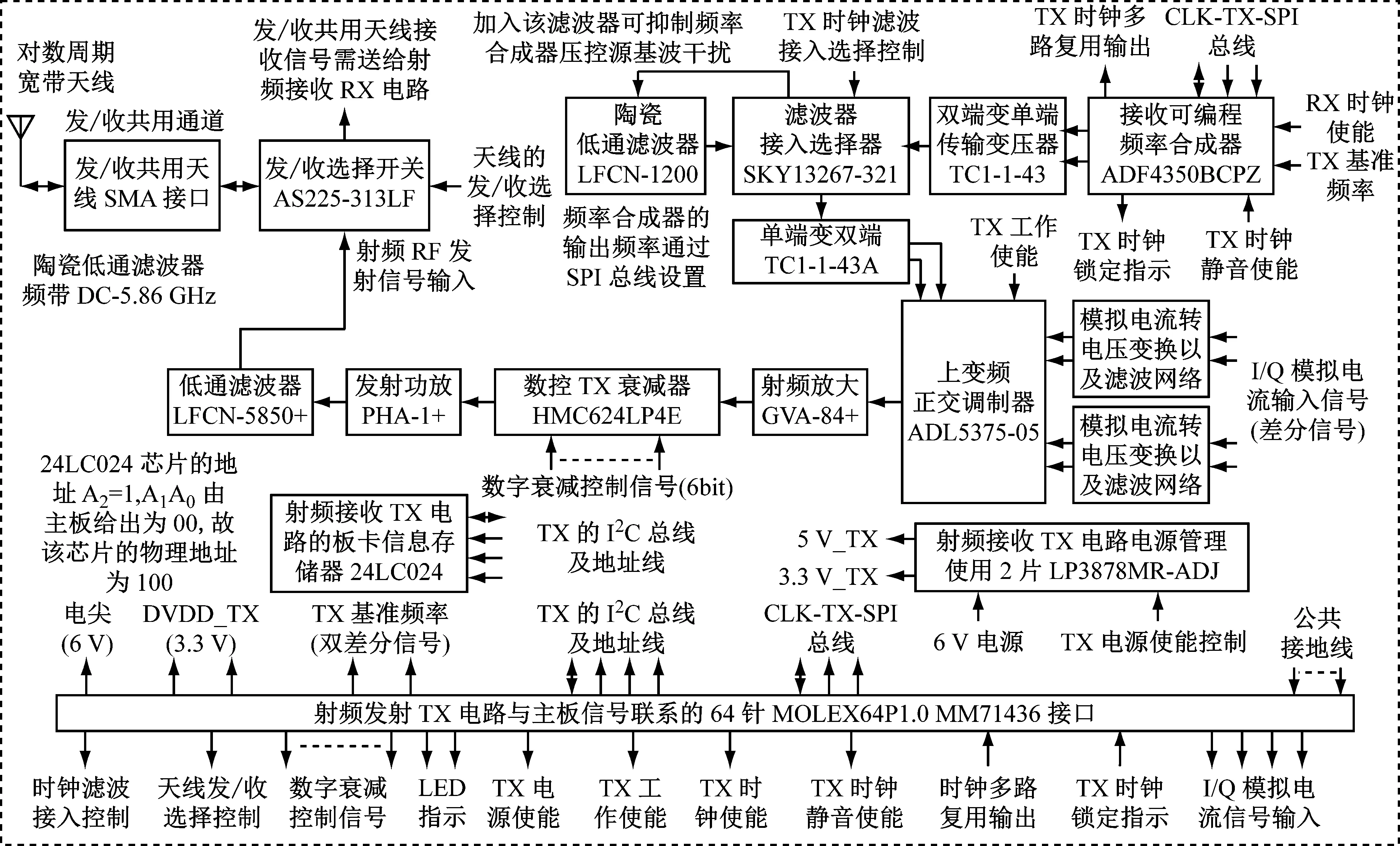

射频子板采用灵活的积木式模块化设计,赋予多种设定选择,既可以设定为固定接收/发射频点、固定功率的无线方式,也可以通过GNU Radio软件控制,随时改变接收/发射频点和功率的动态调整无线方式,便于学生开展各种设计性和创新实验。图1为射频子板功能组成,接收/发射频点均可在400 MHz~4.4 GHz范围内独立的任意设置,且收/发通道功率可以按最小步进为0.5 dB进行独立的6位数控,既可以设定时分双工方式又可以设定频分双工方式。

图1 射频子板基本功能组成

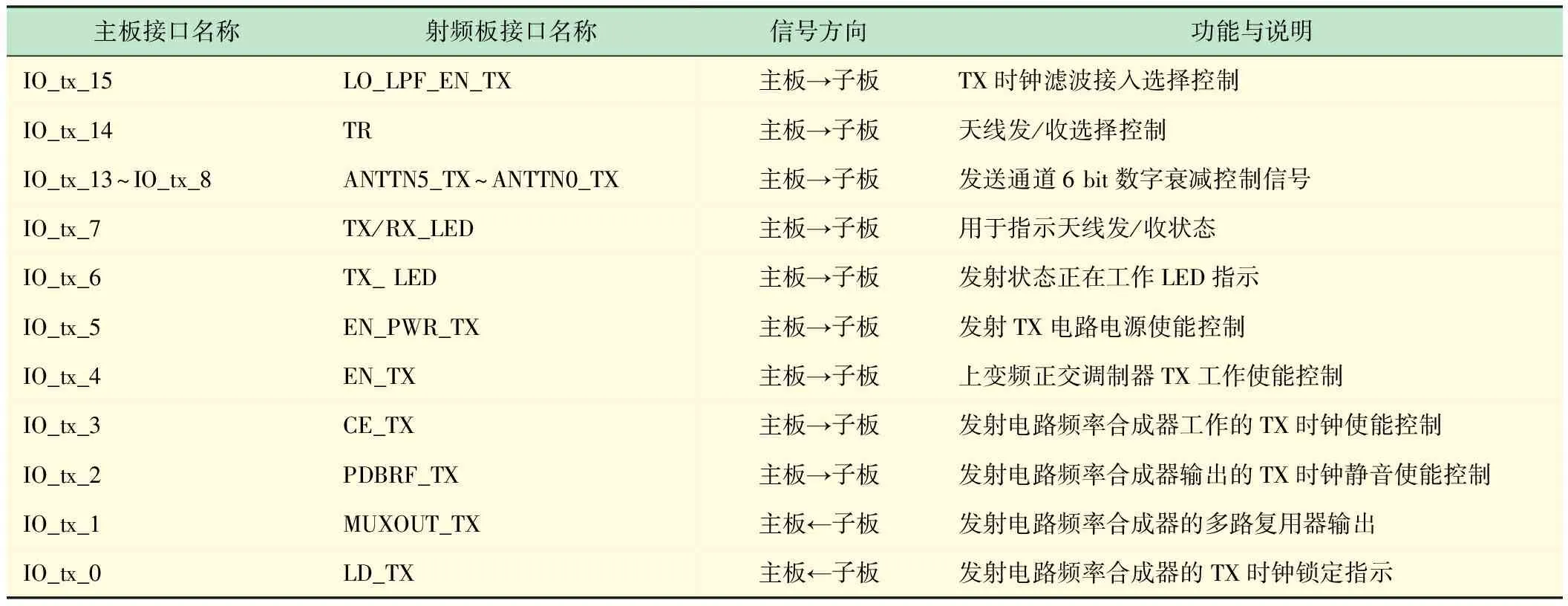

1.2 主板管理射频子板接口定义

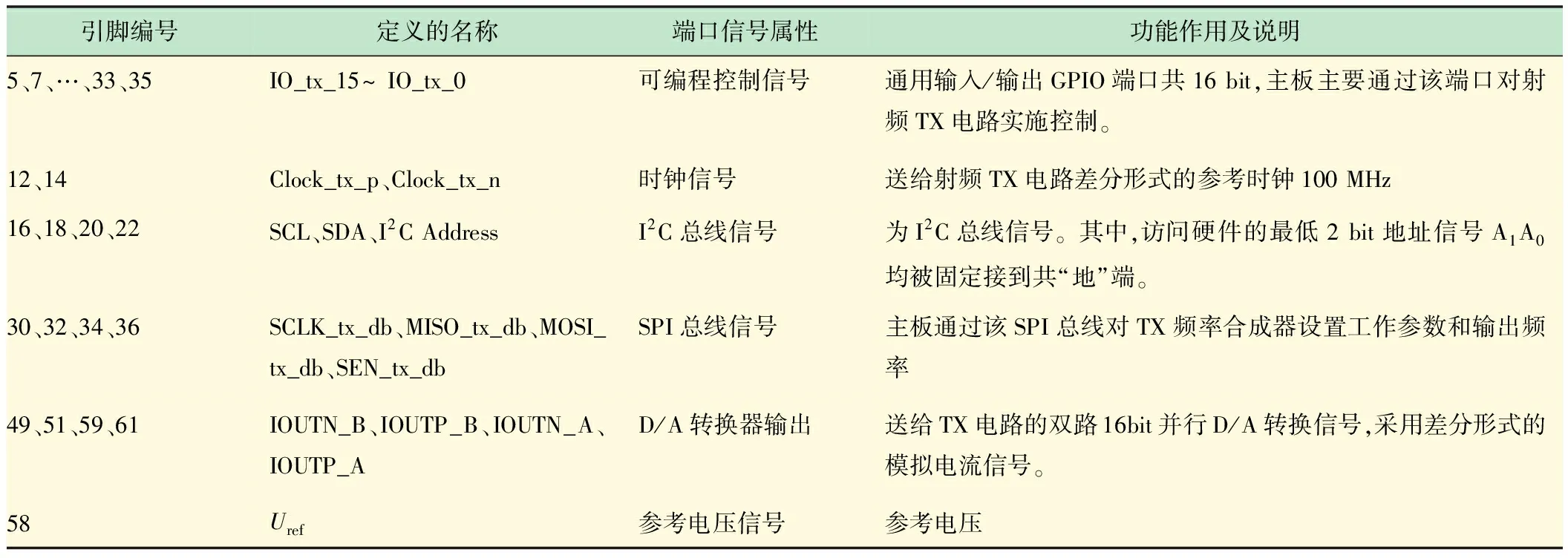

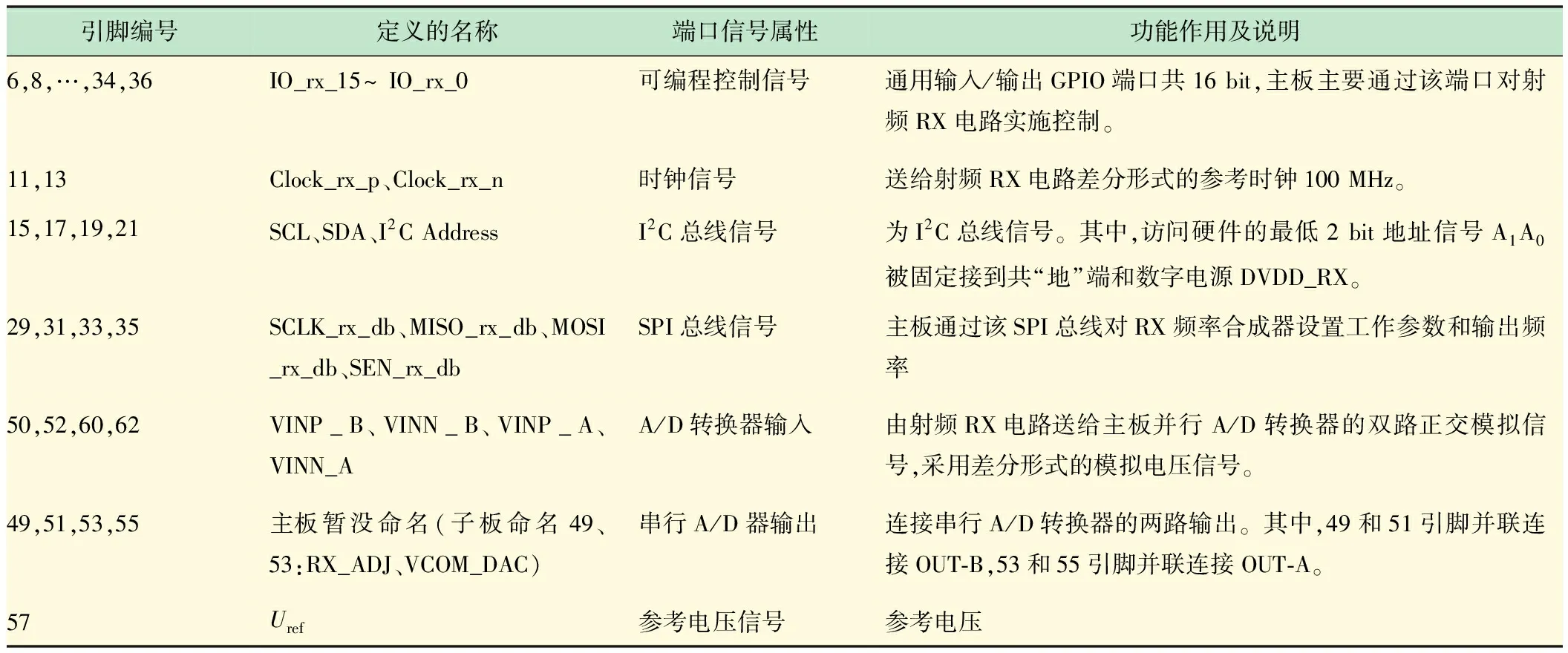

为实现主板对射频子板的控制和管理以及收发信号交互传输,主板与子板接口采用了两个64针接插件,分别作为主板与子板的发射TX和接收RX接口。考虑到积木式应用以及与USRP射频子板SBX_REV3.0的兼容性,主板对TX和RX接口主要有效信号引脚定义如表1和表2所示[7,8]。

表1中串行A/DC输出应用方式比较特殊,主板上串行D/AC主要用于参考基准电压Uref的控制和调整,调整既包括主板又包括射频版,采用从接口给射频板控制射频板中的共模电压UOCM,而UOCM又通过接口再反馈到主板调整ADS62P4X上的共模电压Ucm。D/AC调整UOCM的参数置以数字的形式保存在24LC024板卡信息串行EEPROM中。表1~2中的通用可编程控制I/O端口(General Purpose Input Output,GPIO)[3],共32 bit,即IO_tx_15~IO_tx_0和IO_rx_15~IO_rx_0。信号发/收时主板通过该端口频繁给射频子板控制命令。

表1 主板对发射TX接口主要有效信号引脚定义

表2 主板对接收RX接口主要有效信号引脚定义

2 射频子板电路原理

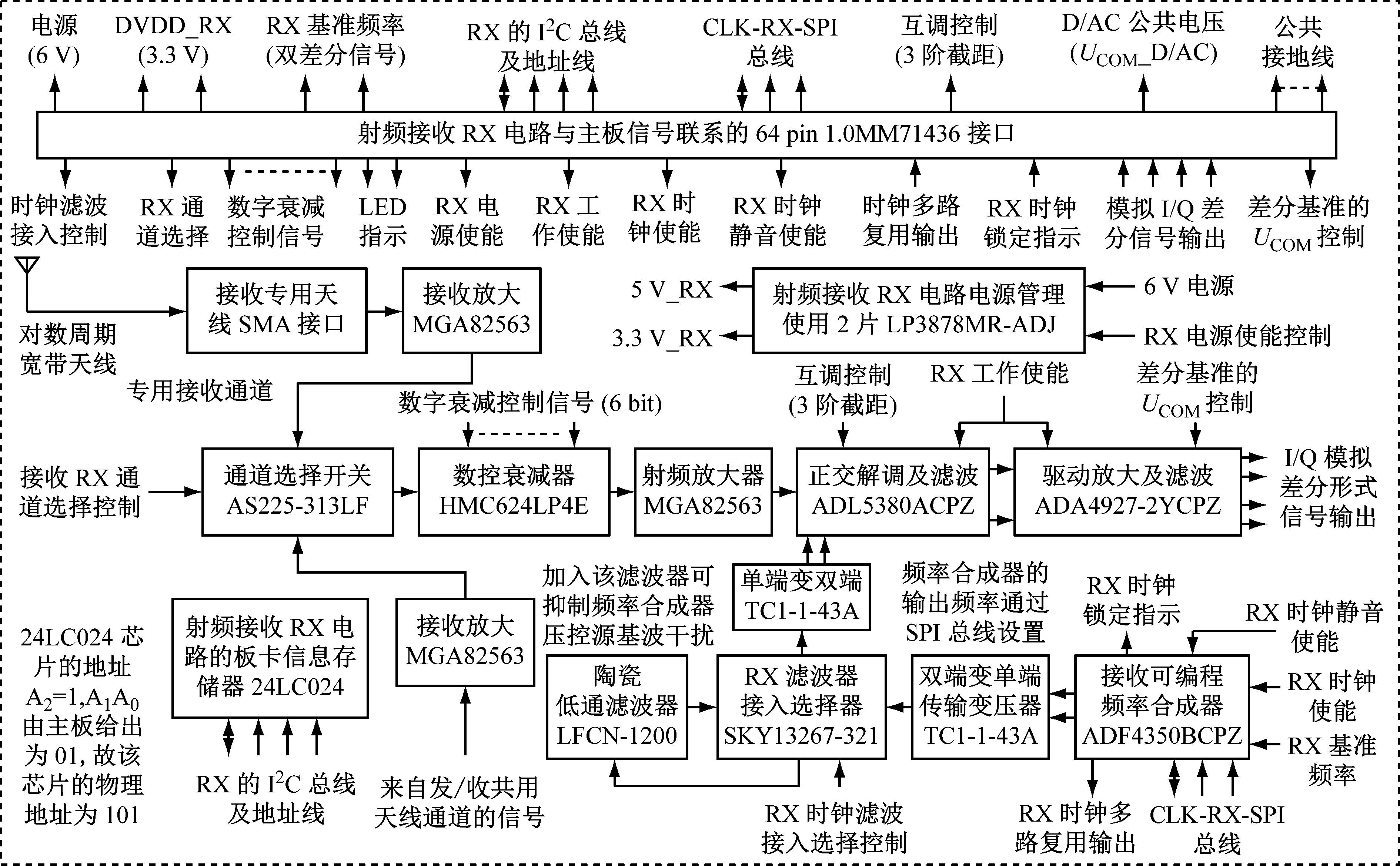

2.1 无线接收RX电路工作原理

射频子板接收RX电路原理如图2所示。图中频率合成器ADF4350,是一款内置片上低噪声压控振荡器VCO的锁相环PLL,VCO的输出基波频率范围2.2~4.4 GHz[9]。ADF4350有一个SPI串行总线接口,根据需要进行数字编程参数设置。支持137.5~4 400 MHz范围内的连续调谐频率输出。ADF4350提供两个射频差分信号输出端口,可对输出功率进行数字编程。锁定状态指示和数字编程选择的多路输出接口,可指示出内部各电路的工作状态。

图2 射频子板无线接收RX电路原理

射频放大器MGA82563工作带宽为0.1~6 GHz[10],增益大于等于17 dB。AS225-313为频带0.1~6 GHz的单刀双掷电子开关[11],利用数字信号就可方便地实现开关的切换控制。HMC624LP4E为数控衰减器[12],其控制方式分为串行控制和并行控制,射频子板采用并行数字编码控制方式,可控衰减范围在0~31.5 dB,最小步进衰减为0.5 dB。ADL5380是宽带正交I/Q下变频解调器[13],采用4.75~5.25 V单电源供电,涵盖从400 MHz~6 GHz的射频输入频率范围。差分射频输入提供功能良好的50 Ω宽带输入阻抗,射频子板采用1∶1巴伦驱动。通过控制ADL5380的调节引脚ADJ,改善3阶截距控制互调的产生。在正交I/Q变频解调器的2路输出均连接了5阶巴特沃斯低通滤波器[14],滤波器截止频率为fc=40 MHz。ADA4927为低噪声、超低失真、高速、电流反馈型差分放大器[15],适合驱动分辨率为16 bit 100 MHz的高性能A/DC,它有2个电压反向输出和1个附加UOCM输入,采用2个反馈环路来控制差分和共模输出电压。共模反馈环路为内置,使用电压反馈架构且仅控制共模输出电压。输出共模电压由内部共模环路强制设定等于UOCM的输入电压。输出共模电平可以与所需A/D输入共模电平实现匹配,且内部共模反馈环路可提供输出平衡并能抑制偶数阶失真产物。在ADA4927的正交I/Q 2路输出端,均连接了3阶巴特沃斯低通滤波器,以进一步滤除杂波。由于变频解调器滤波器截止频率为fc=40MHz,为了使有用信号不再衰减,该滤波器截止频率设计为fc=50 MHz。

2.2 无线发射TX电路工作原理

射频子板发射TX电路原理如图3所示。该电路通过发/收选择可实现射频发射和接收天线共享。因为其频率合成器、收/发选择电子开关、数控衰减器、电源等电路的设计方法与图2无线接收RX电路中同类电路的相同,故不再赘述。

ADL5375是宽带正交上变频调制器[16],工作频率范围400~6 GHz。相位精度与幅度平衡适合于通信系统中高性能的中频或射频调制。研制射频子板时考虑到D/A与正交调制器间的直流偏置电压差越小信号传输损失就越小,选定ADL5375-05型正交调制器应用于设计。该器件具有宽基带,输出增益平坦度在450 MHz~3.8 GHz范围内变动幅度不超过1 dB。ADL5375-05可接收双路差分基带50 Ω阻抗输入,输出为50 Ω阻抗的单端口。由于主板D/AC输出的是差分模拟电流,而ADL5375-05要求的是电压输入,因此在2路输入前利用电阻网络进行I/U变换及阻抗匹配,且为了滤除D/A转换的杂波,利用截止频率fc=40 MHz的5阶巴特沃斯低通滤波器对信号进行滤波。射频子板的TX电路中设计了2个放大器,GVA-84射频放大器[17]为达林顿改进形式的单片放大器,5 V电源供电情况下,在100 MHz~4.4 GHz频率范围内增益优于14 dB。PHA-1功率放大器[18],它是输出阻抗为50 Ω的超高动态范围单片放大器,5 V电源供电情况下,在100 MHz~4.4 GHz频率范围内增益优于10 dB。

图3 射频子板无线发射TX电路原理

3 主板对射频电路控制方法

3.1 通用I/O可编程控制端口

通用I/O可编程控制端口GPIO,任务是负责发送/接收通道的射频管理和控制,主板通过GPIO对电源转换器、频率合成器、频率调制器/解调器和数控衰减器的控制。在主板和射频子板中都明确划分出了发送通道与接收通道,GPIO对应的射频功能引脚名称及功能表3~4[7]。实验平台对影响全局信号的控制接口操作方式如下。

时钟滤波接入选择控制LO_LPF_EN,无论是发射电路还是接收电路,只有在射频频率低于1.2GHz时,才考虑给频率合成器的输出接入滤波器,当LO_LPF_EN为高电平时将插入滤波器。天线发/收选择控制信号TR为高电平时,发/收共用天线作为发射天线,否则作为接收天线。接收通道选择控制信号LNA为低电平时,射频输入选择专用接收天线通道。当LNA为高电平且TR为低电平时,射频输入选择发/收共用天线通道。电源使能控制EN_PWR为高电平时关断电路直流供电电源,为低电平时则开启电源;上变频正交调制器工作使能控制EN_TX为高电平时禁止输出,低电平时正常输出;频率合成器时钟工作使能控制CE_TX为低电平时,电路停止频率合成器工作,高电平时恢复工作。频率合成器时钟静音使能控制PDBRF_TX为低电平时,电路虽然在正常工作但输出被关断,为高电平时才能有输出。数字衰减控制信号ANTTN5~ANTTN0为正逻辑信号,衰减范围在0~31.5 dB内可按照0.5 dB步进数字编码任意控制。

表3 发送通道GPIO接口

表4 接收通道GPIO接口

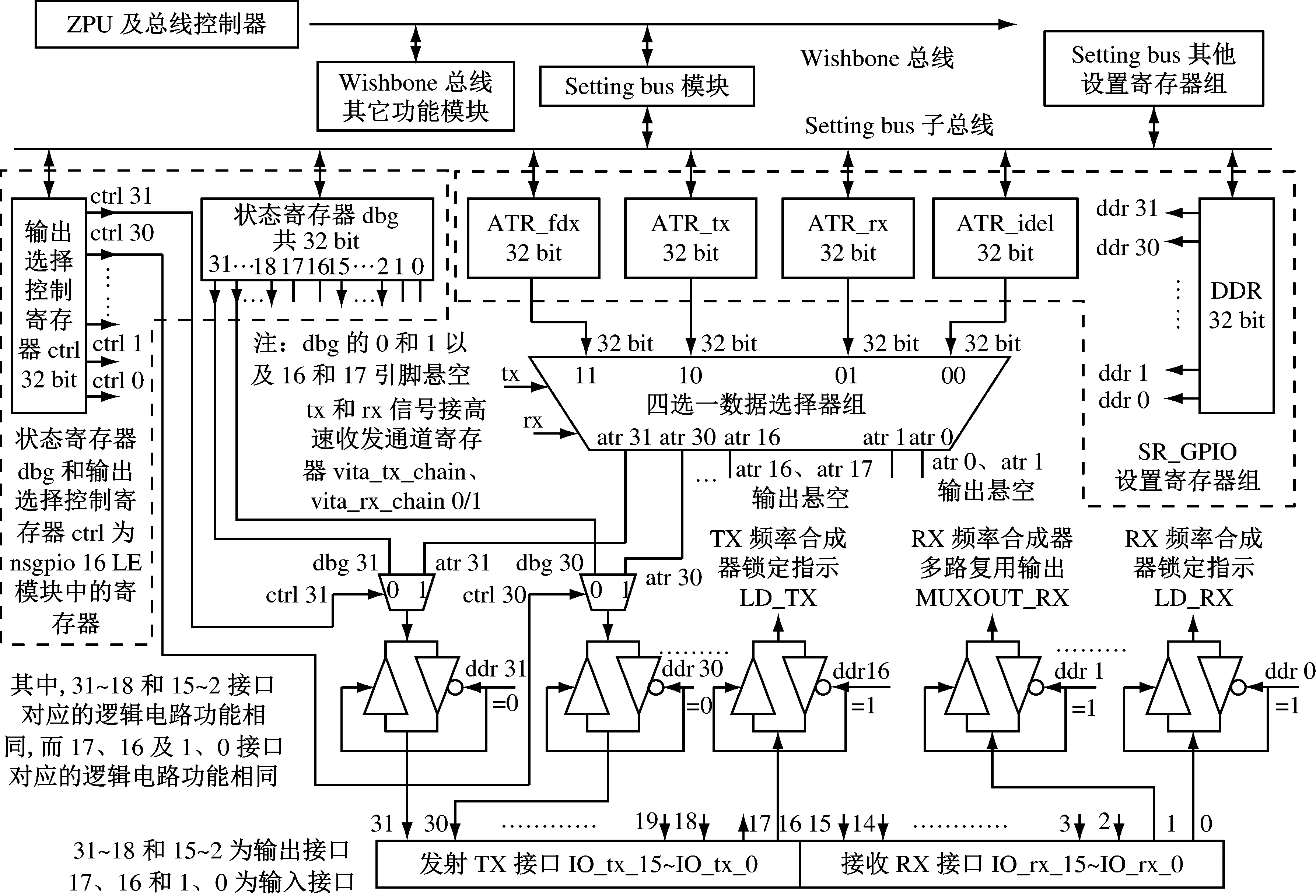

3.2 主板通过GPIO对射频电路的控制

主板对射频电路实施控制需通过FPGA内定义的32 bit GPIO接口,GPIO逻辑工作原理如图4所示。

图中每个32 bit I/O口分为高/低各16 bit,对应发送子板和接收子板的GPIO接口。在FPGA内定义了一个32 bit设置寄存器组SR_GPIO,是挂接Wishbone总线上Setting bus功能模块下的子单元模块[3,19],访问SR_GPIO寄存器组需通过(Zylin CPU, ZPU)[3,20]操作,使用子功能单元寻址方法。在寄存器组SR_GPIO中定义了5个32 bit寄存器为:1个DDR和4个ATR寄存器。DDR寄存器用于确定FPGA的I/O口O/I状态,bit为0时为输出口、1时为输入。4个32 bit ATR寄存器,分别存储发送/接收子板常用4种设置信息,分为空闲ATR_idel、接收ATR_rx、发送ATR_tx、双工ATR_fdx等状态,其内容需根据表1和表2功能预先设置。在射频收/发期间4个ATR寄存器具体由哪一路输出,由tx和rx信号选择。tx和rx是高速端口送来的控制信号,改变tx和rx的逻辑状态组合,就可实现射频电路工作方式的快速转换。

图4 实验平台主板的FPGA内GPIO接口控制逻辑原理

主板对射频电路的控制,除上述4种常用状态的转换控制工作方式之外,还可以通过操作用户设置寄存器Nsgpio16LE实现非常规任意收发状态的切换。这时GPIO的输出可由用户定义Nsgpio16LE寄存器状态决定。为了确定设备是什么方式控制,在Nsgpio16LE寄存器组中设计了输出选择状态寄存器dbg,以及配套的控制寄存器ctrl。当ctrl寄存器某一bit为1时,采用快速转换控制,即该bit的值由ATR寄存器决定;当该bit为0时,设备收/发由用户定义的状态寄存器dbg去控制。再有,GPIO既可以用于向射频板写入配置信息并可回读,也可以把配置信息和输入的频率锁定指示等引脚全部信息,送到用户定义的回读寄存器中,再通过命令执行高速响应,送入控制命令应答寄存器中,供进一步管理和控制使用。

4 结 语

本文分析了实验平台中射频子板电路工作原理,以及主板对射频子板实施的管控方法。主板与射频子板相互配合,可方便地实现双频双工/半双工、单频双工/半双工、单独发射或单独接收等通信方式,收发增益可数字控制,射频收/发电路的频率可通过SPI串行总线随时设置,射频频带范围宽达4 GHz。射频子板在电路设计上采用了宽带与模块化思想,在管理操作方面采取接力式的层级控制方法,应用灵活适应性强。掌握射频子板工作原理及管控方法,不仅有助于全面理解软件实验平台的系统工作原理,而且为个性化地开展创新实验教学奠定了基础。通过连续几篇文章的介绍,可以系统地掌握实验平台硬件工作原理,读者只需将实验平台硬件进行软件驱动映射,转化为应用程序接口,就能开展具有创新特色的软件无线电开发。