基于FPGA的时域滤波抗干扰实现与验证∗

2019-09-03张道成

张道成

(91404部队 秦皇岛 066200)

1 引言

从20世纪中叶开始,随着超大规模数字集成电路的发展和计算机技术的广泛应有,数字信号处理越来越多的被应用到了现代工业体系中[1],如通信、雷达等领域,尤其是在航天领域,导航卫星接收信号的实时处理[2~7],不仅需要简单的实时处理,更加需要高速实时处理。

目前,市场上主要是三种信号处理器[8],DSP、ARM、FPGA,而FPGA主要存在功耗低、设计灵活并且工作频率高的优点,相比较而言,开发起来更加简单,而且稳定性高,可以很好地满足导航卫星信号实施处理高速、高时效性及大数据的要求[9],故本文主要采取FPGA进行研究。

2 时域滤波FPGA设计

FPGA的开发,主要是使用电子设计软件和编程工具对芯片进行设计实现的过程,根据实际需求和经验,本文进行了以下的设计实现的过程。

2.1 主要设计流程

FPGA实现与验证的主要设计流程如下[10]:1)编写VHDL代码,遵照至顶向下的原则,按照Matlab定点仿真的思路编写。

2)编好代码后,用Modelsim仿真,来验证程序流程是否正确,时序是否与设计时一致,基本功能是否实现。

3)把FPGA计算出的数据导出,与Matlab计算结果进行比较;需要注意的是,FPGA与Matlab输入的数据要完全一致,Matlab中的运算要用定点,保证与FPGA中的运算完全一致。如果不一致,将返回代码,查找原因。

4)FPGA与Matlab计算的结果一致后,将程序烧到板卡上,实际测试;在实际运行中,用Chipscope观察实际运行的结果,并与Matlab仿真的结果进行比较。如果要与Matlab程序进行比对,就要保证两者的输入一致,这就要求FPGA程序在实际运行时要收集一段数据,作为Matlab数据源,然后比对结果。

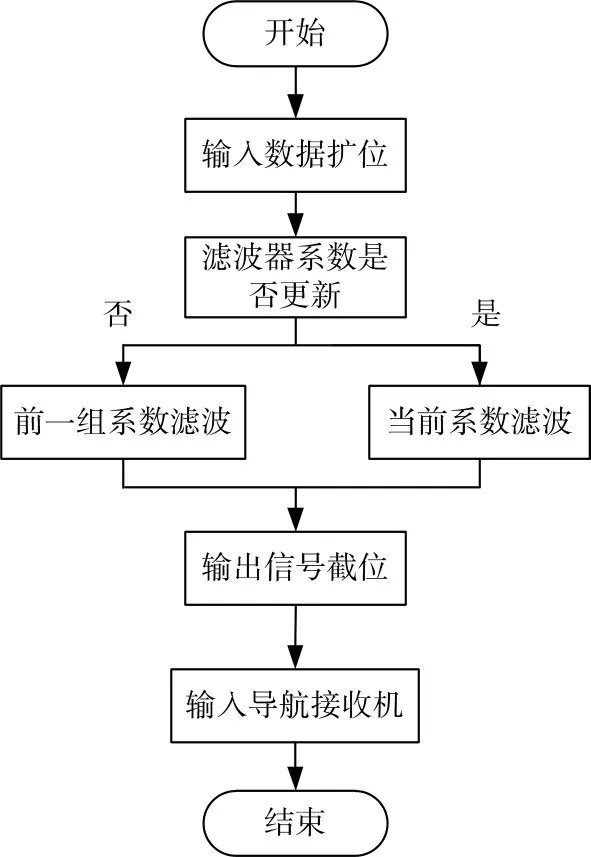

5)总结测试结果,做出最后结论。具体算法如图1。

图1 FPGA实现与验证算法

2.2 滤波器系数更新

根据导航接收机抗干扰的不同的算法类型[11],本文的滤波器采用时域NLMS算法[12],需要根据干扰的变化,及时更新系数。但每进一个数据都更新一次系数的计算量太大,而且干扰不可能变化那么快,所以要找到一个合适的时间间隔来更新系数。初步用接收机给出的10ms中断作为标志位来对系数更新。由于抗干扰后的数据要进入接收机用于定位,所以出来的数据要保证连续性,如果有延时需要保证每个数据延时的一样。具体方法如图2:

图2 系数更新示意图

接收机发出10ms中断,fifo开始接收用于更新系数的信号源,接收完成后,开关闭合,停止接收;当系数完全更新后一次性送到抗干扰算法模块,抗干扰模块将用新系数来对信号源消除干扰。

图3 Modelsim仿真系数更新

2.3 滤波器扩位截位处理

在Matlab中计算出的滤波器系数都是小于1的小数,如果直接取整就会造成系数全是0或1的结果,滤波器将会失去作用。所以在这里考虑首先将滤波系数扩大,然后取整计算,最后在输出结果缩小相应的倍数。

根据算法定义,

FPGA中规定一个乘法器是18*18,如果数据位数超出18位,一次乘法就需要使用两个乘法器。从式(2)中可以看出,将步长扩大128倍,实际上也是将系数h(k)扩大128倍,为了节省乘法器,就将系数的扩大倍数定位1024倍。这样系数的位数就是1024*128位,输入数据也将扩大1024*128位,最后在滤波器输出结果上将数据缩小1024*128倍,数据仍然是8bit。程序设计基本流程如图4所示。

图4 抗干扰计算流程

3 验证FPGA程序正确性

验证FPGA程序功能是否正确,主要分为两个部分,一是Modelsim仿真结果与Matlab仿真结果比对;二是Chipscope实时观测滤波器系数计算是否正确。这两项都正确后说明FPGA程序能够正常实现抗干扰功能。

3.1 Modelsim仿真

将FPGA程序完全按照Matlab仿真程序编写,如果FPGA程序编写正确,那么FPGA程序应与Matlab程序输出结果一致。将输入源设为相同,观测FPGA仿真结果,并与Matlab结果比对。由图6所示,FPGA计算滤波器系数结果与Matlab计算结果完全一致。

图5 FPGA计算系数(左)Matlab计算系数(右)

图6 FPGA计算结果与Matlab计算结果比对

3.2 FPGA板上验证

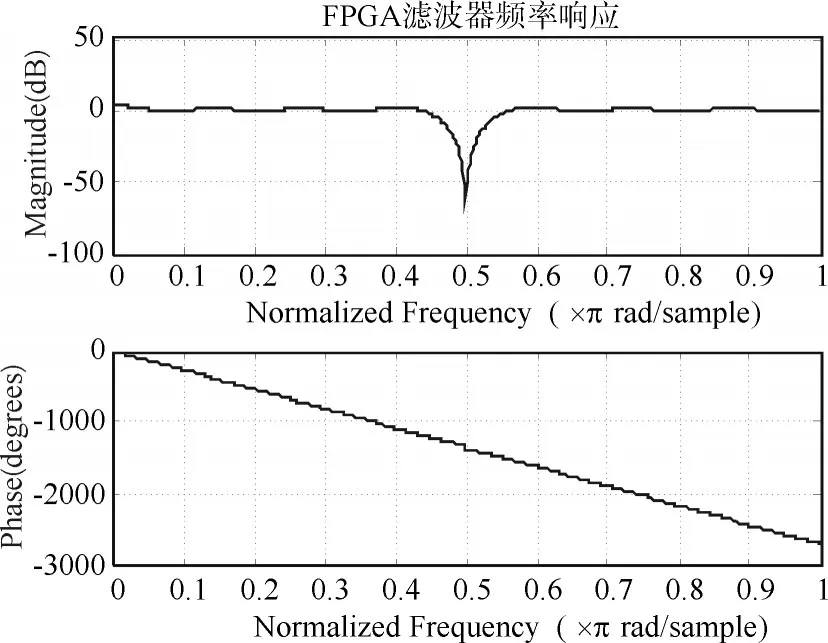

将程序下载到板卡上,Chipscope捕捉FPGA中计算出的系数、输入中频数据以及滤波器的输出结果。在Matlab中进行数据转换,可以看到滤波器的频率响应及抗干扰效果。具体见图7、图8。

4 抗干扰性能指标测试

4.1 测试环境

1)导航信号:由导航模拟源产生模拟信号,可根据需要调整信号功率;

图7 FPGA计算的滤波器频率响应

图8 FPGA抗干扰前后信号频谱对比

2)干扰信号:干扰由4438C模拟信号源产生。

4.2 测试结果(见表1)

表1 单载波干扰测试结果

从表1中可以看出,对于单载波干扰,大约可以抵抗干信比54dB的干扰,干扰频率在中心频点±100KHz与±1MHz的差别并不是很大,并没有因为靠近中心频点性能会变差,这也是插值滤波器的特点。

4.3 测试结果分析

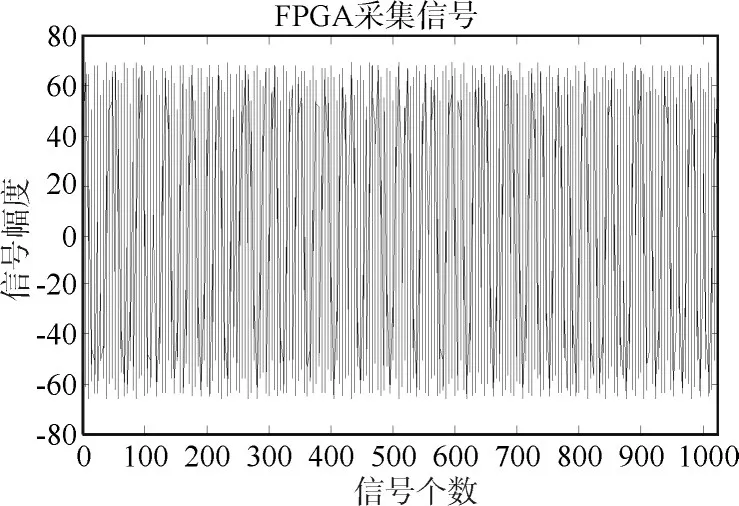

1)实际AD量化位数减少,见图9。

图9 FPGA采集信号幅度

由于AGC的作用,干扰增大会导致压缩信号幅度,当干扰达到一定功率时,信号将被完全压制。所以当量化位数少时,所能容纳的干扰功率也就随之减小。

2)实际干扰与理想干扰差别,见图10。

图10 实采干扰信号频谱

由于硬件原因,在中频输出端干扰会出现二次谐波。当干扰为-70dBm时,由图10所示,椭圆圈区域为二次谐波,这会造成载噪比的损失。

5 结语

随着信号处理器的不断发展,利用FPGA实现信号的高速、髙时效处理,已经成为一种趋势,本文在导航接收机抗干扰时域滤波的基础上,编写FPGA程序,并在Modelsim中仿真,与Matlab定点仿真程序进行比较,确定FPGA程序输出与Maltab程序输出完全一致,保证FPGA程序功能正确;并在接收机中实际调试,验证FPGA程序。