新型绝缘体上硅静态随机存储器单元总剂量效应*

2019-08-29王硕常永伟陈静王本艳何伟伟葛浩

王硕 常永伟 陈静† 王本艳 何伟伟 葛浩

1)(中国科学院上海微系统与信息技术研究所,信息功能材料国家重点实验室,上海 200050)

2)(中国科学院大学,材料与光电研究中心,北京 100049)

1 引 言

绝缘体上硅(silicon-on-insulator,SOI)技术与体硅工艺相比,通过引入掩埋氧化物(buried oxide,BOX)结构给器件提供了全介质隔离,从而避免闩锁效应,减少电荷泄漏,同时减小了寄生电容,提高了器件的开关速度[1].然而,直接将体硅工艺中的MOSFET移植到SOI工艺中,由于碰撞电离和电子隧穿,电荷将会在体区积累,导致MOSFET出现浮体效应(floating-body effect,FBE).这些额外的电荷导致晶体管体电位不稳定、亚阈值摆动异常以及漏极-源极击穿电压(drainto-source breakdown voltage,BVds)减小等问题[2].通常采用体区引出技术可以有效地抑制SOI器件的浮体效应.

在空间辐射环境中,辐射效应主要分为总剂量辐射效应(total ionizing dose,TID)和单粒子效应(single event effect,SEE).其中,空间高能粒子在集成电路的材料中电离产生电子-空穴对,这些电荷在氧化层中积累形成氧化物陷阱电荷或者在氧化层与半导体材料的界面处形成界面陷阱电荷,从而造成器件的性能降低甚至功能失效,称为总剂量辐射效应[3].随着半导体工艺的进步和数字集成电路性能的提升,静态随机存储器(static random access memory,SRAM)在片上系统和专用集成电路上所占面积比例不断增加,而静态随机存储器单元(SRAM cell)的特征尺寸却不断减小,SRAM存储单元成为电路中总剂量效应最敏感的部分之一[4].目前,已有许多体接触场效应晶体管结构被提出来以改善总剂量效应,例如H栅场效应晶体管器件[5],GAA[6],BUSFET[7]以及FlexFET[8].虽然它们可以抑制由总剂量效应引起的浅沟槽隔离(shallow trench isolation,STI)或掩埋氧化物漏电流,但是它们存在面积过大、工艺步骤复杂、制造成本昂贵等缺点.

因此,本文设计了一种基于L型栅体接触(L-gate body-contact,LB)MOSFET的6晶体管静态随机存储器单元(6 transistors LB static random access memory cell,6T LB SRAM cell),并对基于不同MOSFET的单个静态随机存储器单元主要电学性能在总剂量效应下的变化进行研究,直观地体现总剂量效应对静态随机存储器单元的影响.通过60Co-γ射线辐照分析,验证了所提出的6T LB SRAM cell相比于基于传统浮体场效应晶体管的6晶体管静态随机存储器单元(6T FB SRAM cell)具有漏电更小、稳定性更高等特点,在辐射环境中具有稳定可靠的实用价值.

2 SOI MOS器件

2.1 器件结构

MOS器件结构直接影响着静态随机存储器单元的各方面性能.针对SOI工艺的特点,本文选择了具有代表性的传统浮体(floating body,FB)场效应晶体管和T型栅体接触(T-gate body-contact,TB)场效应晶体管,如图1(a)和图1(b)所示.由于静态随机存储器单元的版图一般采用中心对称的结构,同时考虑到面积作为静态随机存储器设计的重要指标,于是本文采用了一种L型栅体接触场效应晶体管设计制备了具有紧凑版图结构的6T LB SRAM cell.图1(c)为该 LB MOS器件的N型器件3维示意图.以LB NMOS器件为例,该器件通过重掺杂P型硅将P型体区引出,而重掺杂P型硅又与器件的N型源区紧密接触.如图1(f)所示,硅的金属工艺步骤将在源区与体区硅表面形成CoSi2硅化物,该硅化物实现了源区与体区互连的源体接触结构.硅表面形成CoSi2硅化物是半导体工艺中常见的步骤,通常该工艺的目的在于增加MOS器件有源区和栅极的导电性能.该LB MOS器件遵守传统SOI CMOS工艺版图设计规则,不需要添加额外的掩模版或其他复杂工艺,可以实现较好的源体接触.

2.2 SOI MOS器件的实验系统及测量结果

图1 (a)FB NMOS版图;(b)TB NMOS版图;(c)LB NMOS 3维示意图;(d)LB PMOS版图;(e)LB NMOS版图;(f)LB NMOS器件沿(e)图线A-A'截取的器件横截面图Fig.1.(a)The layout of FB SOI nMOSFET;(b)the layout of TB SOI nMOSFET;(c)the LB nMOSFET 3-dimensional schematic;(d)the layout of LB pMOSFET;(e)the layout of LB nMOSFET;(f)a cross-sectional view of LB nMOSFET is taken along line AA' in(e).

本文基于标准的130 nm SOI工艺,制备了相同尺寸(W/L=0.5 µm/0.13 µm)的 LB,TB和FB NMOS器件.其中,顶层硅(top silicon)和BOX的层厚度分别为100和145 nm,栅极氧化层的厚度为1.8 nm.所有器件在室温下使用Agilent B1500A在片测试.

图2(a)为VD=0.1 V时器件的转移特性曲线,LB,TB和FB NMOS器件的线性阈值电压(threshold voltage,Vth)几乎相同.但是,当栅极电压VG=1.16 V时,FB NMOS器件跨导曲线出现峰值.这是由于NMOS器件体区价电子隧穿至栅极留下空穴,而多晶硅栅导带空穴隧穿进入体区,体区空穴积累造成栅致浮体效应(gate induced floating body effect,GIFBE),致使器件Vth降低、跨导升高.而LB和TB NMOS器件跨导曲线相对平缓,其栅致浮体效应受到抑制.这与文献[9]中的结果一致.除了栅致浮体效应,130 nm SOI MOS器件存在漏致势垒降低(drain-induced barrier lowing,DIBL)效应,并导致浮体效应[10].由图2(b)可知,LB,TB和FB NMOS器件的DIBL值分别为 34.2,34.5和152 mV/V.LB和TB NMOS器件的DIBL效应相近,并明显优于FB NMOS器件,有效地抑制了浮体效应.当VD=1.2 V时,FB NMOS器件的Vth明显小于LB和TB NMOS器件.LB,TB和FB NMOS器件的输出特性曲线如图2(c)所示.由于空穴注入,可以在FB MOS器件的输出特性曲线中观察到扭结效应(kink effect)[11].在VDS> 0.6 V 时,FB NMOS 中的扭结效应明显,而LB和TB NMOS器件则明显抑制扭结效应.图2(d)显示了 LB,TB和FB NMOS器件中漏极-源极击穿电压(BVds),其中BVds被定义为漏极电流ID=100 nA且栅极电压VG=0 V时的漏极电压,该效应是由寄生双极管导致源极-漏极穿通引起的[12].LB,TB和FB NMOS器件的BVds分别为3.15,3.20和2.45 V.LB NMOS的 BVds值比 FB NMOS增加 21%,与TB MOS几乎相同.这是因为体电位固定在零电位,LB和TB NMOSFET的BVds得到有效改善.

测试结果表明,在130 nm SOI工艺下,LB MOS相比传统FB MOS成功抑制了浮体效应,并且DIBL和BVds特性得到了改善.而且由于采用特殊体接触设计,具有面积小、连接方便的优点,工艺上与逻辑电路技术完全兼容.所以,LB MOS适用于大规模集成电路.

图2 FB,TB和LB NMOS器件的(a)转移特性曲线和跨导;(b)ID-VG曲线;(c)输出特性曲线;(d)BVds曲线Fig.2.(a)Transmission characteristic curve and transconductance;(b)ID-VG curve;(c)output characteristic curve;(d)BVds curves for the FB,TB and LB NMOS devices.

3 基于不同MOS器件的静态随机存储器单元

3.1 结构与性能

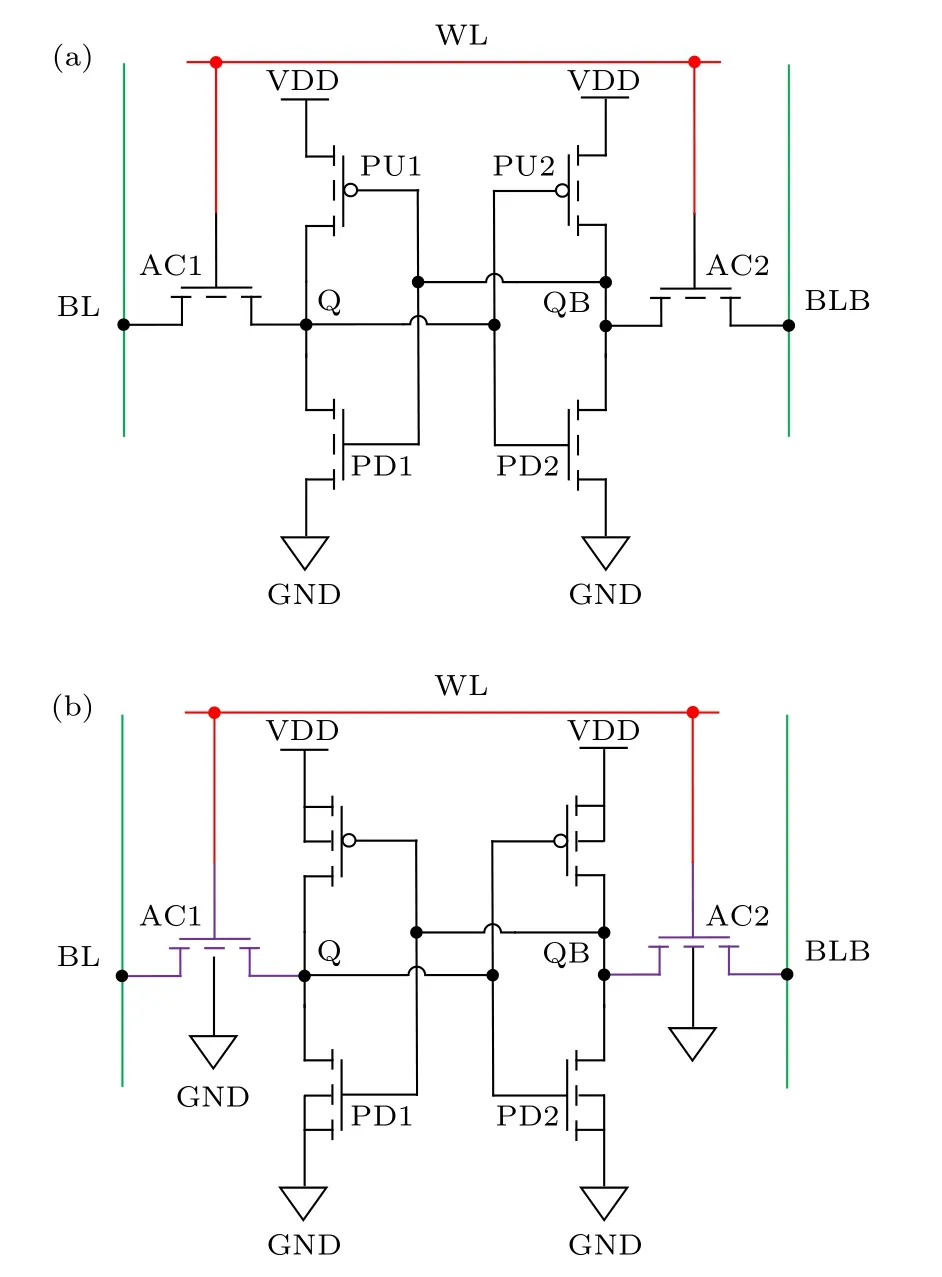

本文所述静态随机存储器单元采用CMOS反相器交叉耦合的传统6晶体管结构,如图3所示.图4 为 6T FB SRAM cell、6T LB SRAM cell与6T TB SRAM cell的版图示意图,最外围通孔包围的部分即静态随机存储器最小的数据存储重复单元.其中,6T LB SRAM cell的两个选通传输管(access device,AC)采用TB NMOS器件,以确保所有晶体管实现体接触.而上拉管(pull-up device,PU)和下拉管(pull-down device,PD)均使用LB MOS器件.对比图4(b)与图4(c)不难发现,虽然LB MOS器件是一种非对称的结构,但由于静态随机存储器单元的版图通常被设计成中心对称的排布以实现最紧凑布局的目的,这使得LB MOS器件搭建的6T LB SRAM cell节省了上下边缘的空间.为了实现静态随机存储单元可读可写的约束条件,晶体管的导通能力应满足[13]:

这意味着(W/L)PD>(W/L)AC>(W/L)PU.依据该原则绘制的具有相同晶体管尺寸的6T LB SRAM cell,6T TB SRAM cell以 及 6T FB SRAM cell样品的面积分别为3.36,4.29和2.1 µm2.根据图5数据,与6T FB SRAM cell相比,6T LB SRAM cell的读状态静态噪声容限(reading static noise margin,RSNM[14])提高了45.7%,而与基于TB MOS的静态随机存储器单元(6T TB SRAM cell)性能接近.由此可见,6T LB SRAM cell在保证RSNM性能与6T TB SRAM cell基本一致的情况下,版图面积可减少约22%.虽然其面积大于6T FB SRAM cell,但存储单元的稳定性能却得到提升.

图3 (a)基于FB器件的6管静态随机存储器单元的原理图;(b)基于LB(或TB)器件的6管静态随机存储器单元的原理图Fig.3.SOI SRAM cell schematic circuit of(a)The 6T FB SRAM cell;(b)the 6T LB SRAM cell or 6T TB SRAM cell.

图4 (a)基于FB器件的6管静态随机存储器单元的版图示意图;(b)基于LB器件的6管静态随机存储器单元的版图示意图;(c)基于TB器件的6管静态随机存储器单元的版图示意图Fig.4.SOI SRAM cell schematic layout of(a)The 6T FB SRAM cell;(b)the 6T LB SRAM cell;(c)the 6T TB SRAM cell.

图5 基于LB,TB和FB MOS器件的静态随机存储器单元的RSNM曲线Fig.5.The RSNM curves of FB/TB/LB SRAM cell.

3.2 总剂量效应实验描述

实验使用60Co-γ射线源模拟恶劣的辐射环境,测试静态随机存储器单元的总剂量辐射效应.辐射的剂量率为276 rad(Si)/s.实验测定了在100,300,500和700 krad(Si)的辐射剂量下静态随机存储器单元的漏电流和读状态静态噪声容限.表1为针对不同测试项目器件的辐照偏置条件.测试均在辐照后1h内完成,使用Keithley 4200SCS半导体参数分析仪测试静态随机存储器单元的相关电学特性.

3.3 实验结果与讨论

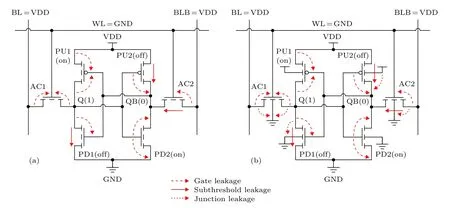

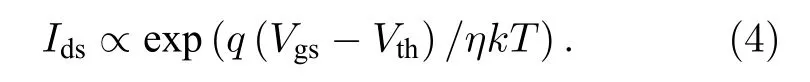

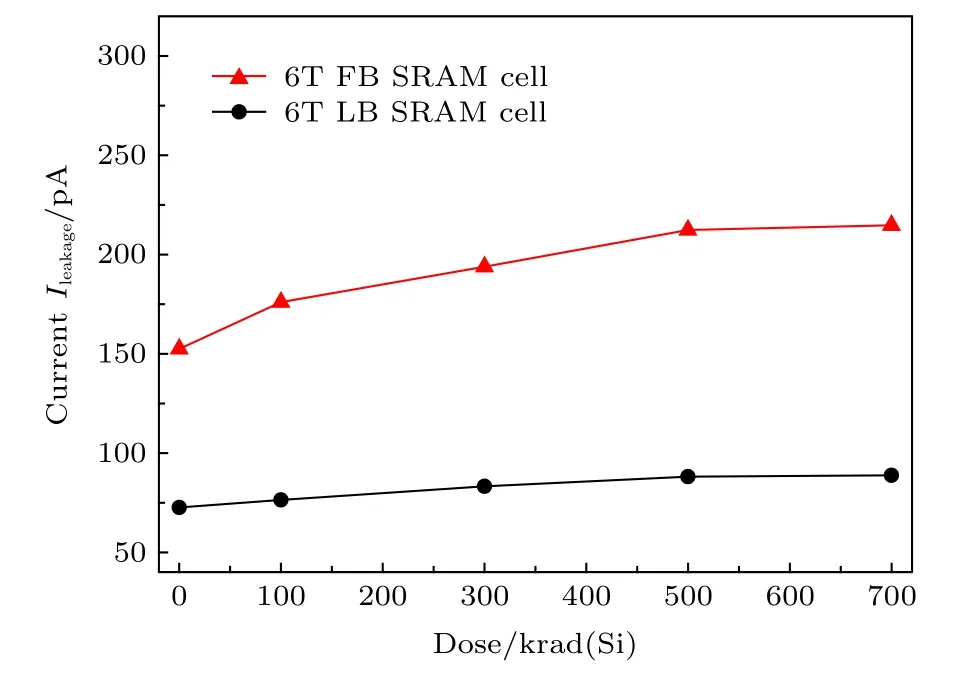

静态随机存储器单元处于保持状态时流过该单元所有器件总的漏电流量是反映该存储单元静态功耗的重要指标.图6为静态随机存储器单元的漏电流测试示意图.测试时,VDD,BL和BLB相连接并接到供电电源,而WL和GND接到共同的地.保持状态下,工作电压(1.2 V)偏置时流经地的电流即为储器单元的漏电流.图7显示了不同辐射剂量下基于FB和LB MOS器件的静态随机存储器单元总的漏电流.当辐射总剂量增加到300 krad(Si)时,6T FB SRAM cell的漏电流从辐照前的152 pA急剧增加到194 pA.而当辐照总剂量从500 krad(Si)增加到700 krad(Si)时,由总剂量效应引起的漏电流增加量减少.这是由于总剂量辐射效应导致的陷阱电荷趋于饱和.随着沟道长度减小,漏极的电势变化会影响到源极与体区之间的势垒高度.高漏极电压使得源极边缘处的势垒高度降低,增加了从源极注入沟道的载流子数量,导致漏极关态泄漏电流增加,这被称为DIBL效应.该效应广泛存在于短沟道的体硅和部分耗尽SOI MOS器件.而LB MOS的体接触结构使源区和体区具有相同的电势,高漏极电压引起的带隙变化主要发生在漏极和体区之间,源极和体区之间的势垒高度的变化减弱.所以,LB MOS器件的DIBL效应减弱.由于DIBL效应,Vth可表示为[15]

其中σ0,σ1和m是用于更好地拟合DIBL效应的模型常数.MOS器件亚阈值区的阈值电压和电流关系可近似表示为

表1 基于LB和FB MOS器件静态随机存储器单元在辐照过程中的偏置条件Table 1. Bias conditions of 6T LB cell and 6T FB cell during irradiation.

图6 (a)6T FB SRAM cell与(b)6T LB SRAM cell的漏电流测试电路及漏电路径示意图(假定Q存储1逻辑值,QB存储0逻辑值)Fig.6.The leakage current test circuit and the leakage path diagram of(a)6T FB SRAM cell and(b)6T LB SRAM cell(Assuming Q stores 1 logical value and QB stores 0 logical value).

图7 基于LB和FB MOS器件的静态随机存储器单元的漏电流在不同辐射总剂量下的变化情况Fig.7.The cell leakage current of 6T FB SRAM cell and 6T LB SRAM cell at different radiation doses.

可见,MOS器件的Vth越小,关态漏电流越大.LB MOS器件的关态漏电流小于FB MOS,这与图2(b)的结果一致.所以,在辐照前,6T LB SRAM cell比传统的6T FB SRAM cell的漏电流小52%.通常对于SOI器件,相同的偏置条件下,浮体NMOS器件的漏电流受到总剂量辐射效应的影响要比体接触NMOS器件的稍微大一些[16].总剂量辐射效应会增强MOS器件STI寄生晶体管以及SOI器件埋氧化层对应的背栅晶体管的DIBL效应,导致器件漏电流增加[17,18].由于浮体器件对于DIBL效应的抑制能力弱于LB MOS器件,导致FB MOS器件的寄生侧壁晶体管以及背栅晶体管的漏电流随辐射剂量增加的变化量高于LB MOS器件.另外,由图1可以看到,LB MOS器件在结构上比FB MOS器件减少了一个STI与器件体区的接触面.这使得6T LB SRAM cell器件的辐射效应关态漏电流比6T FB SRAM cell器件减小一倍以上.如图7所示,当辐射总剂量累积到700 krad(Si)时,6T LB SRAM cell的漏电流从辐照前的73 pA增加到89 pA,增加了21.9%.相比之下,6T FB SRAM cell的漏电流从辐照前的152 pA增加到215 pA,增加了41.4%,漏电流的增加量是6T LB SRAM cell的3.94倍.从该性能可以看出,6T LB SRAM cell的性能受TID效应的影响小于6T FB SRAM cell.

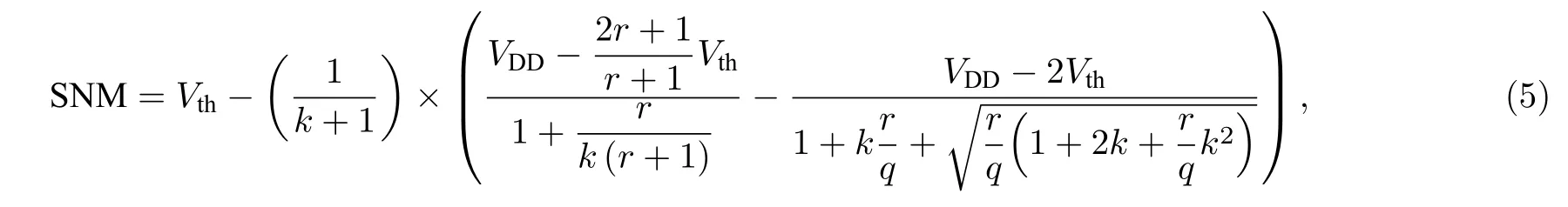

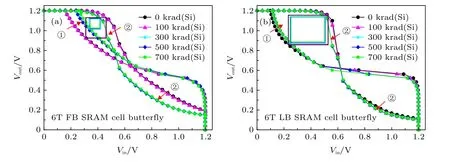

6T FB SRAM cell的读状态静态噪声容限随辐射剂量变化情况如图8(a)所示.当辐射剂量为100 krad(Si)时,RSNM曲线几乎不变.然而,当辐射剂量从100 krad(Si)增加到300 krad(Si)时,相应的读状态静态噪声容限值从250 mV降低到144 mV,变化率为42.4%.6T LB SRAM cell的读状态静态噪声容限测量结果如图8(b)所示.辐照前,该存储单元的RSNM比6T FB SRAM cell高了1.93倍.当总剂量增加到300 krad(Si)时,RSNM从420 mV变为390 mV,下降比率为7.14%.当总剂量为700 krad(Si)时,RSNM降至373 mV,比照射前的RSNM值低11.2%.已知SNM的表达式为[19]

图8 (a)基于FB MOS器件的静态随机存储器单元和(b)基于LB MOS器件的静态随机存储器单元的读取静态噪声容限受总剂量辐射的影响Fig.8.(a)6T FB Cell read stability and(b)6T LB Cell read stability under various radiation doses.

在实际电路中,大部分的静态随机存储器单元都是处于保持状态下(WL=0 V,BL=BLB=VDD),SRAM单元的存储结点将保存为“1”或“0”逻辑.当接受辐照时,由于静态随机存储器单元两个存储结点的电位是相反的,所以结构对称的交叉耦合CMOS反相器处于不同的偏置状态.研究表明,寄生侧壁晶体管的ON状态是辐射下最恶劣偏置[20].而总剂量效应对PMOS晶体管氧化物电荷和界面态的影响,将导致PU器件的阈值电压的绝对值增加[20,21],从而抑制电荷泄漏.首先分析晶体管AC2,PU2和PD2构成的反相器组合.根据图3和表1,辐照时存储器单元的存储结点Q=0 V,晶体管 PU2处于 ON状态,晶体管 PD2处于OFF状态,而AC2处于类似ON状态的非饱和状态.因此,辐照将导致晶体管AC2的Vth减小,而PU2和PD2的|Vth|基本不变.对辐照后对该反相器组合读取状态的传输特性曲线(VTC)进行分析.当存储结点Q被置于低电位时,晶体管AC2和PD2处于线性区,而晶体管PU2处于饱和区,辐照前后曲线变化不明显.当存储结点Q输入高电位时,晶体管AC2处于饱和区,而晶体管PU2处于线性区,根据电路结点电荷守恒原理,有

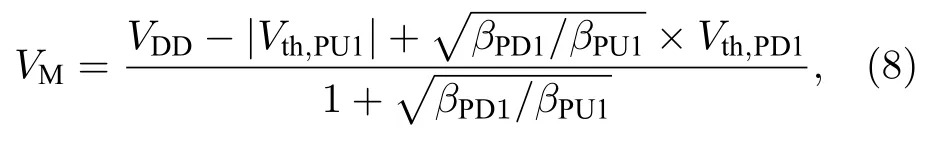

由(7)式得,VQB随着AC2的Vth减小而增加.这个结果与图8中曲线①的结果一致.讨论对称的另一个由AC1,PU1和PD1构成的反相器组.辐照时存储器单元的存储结点QB=1.32 V,晶体管PD1处于ON状态,晶体管PU1处于OFF状态,而晶体管AC1处于饱和状态.因此,辐照将导致晶体管 AC1和PD1的Vth减小,而 PU2的|Vth|基本不变.当存储结点QB置于低电压时,先忽略AC1的作用,根据反相器中点电压VM公式[22]

反相器中点电压VM随着PD1的Vth减小而减小.所以,图8中曲线②发生左移.当存储结点QB置于高电压时,根据(7)式,如果AC1的Vth不变,VQ随着PD1的Vth减小而减小.所以,图8中曲线②辐照后的VQ由于晶体管AC1和PD1制约关系,当VQB=1.2 V时的VQ基本保持不变.图8(a)和图8(b)的曲线变化趋势是一致的.但是,MOS器件的阈值电压由于辐射效应变化越明显,曲线变化的程度越剧烈.FB MOS在辐射总剂量达到300 krad(Si)时,其特性出现明显恶化,从而降低SRAM单元的稳定性.然而,LB MOS对总剂量效应不敏感,在辐射总剂量达到700 krad(Si)后静态随机存储器单元的对称性仍然存在,SNM值比辐照前仅降低了11.2%.

4 结 论

本文采用130 nm SOI工艺,制备了3种静态随机存储器单元.研究了不同MOS器件的结构和电学性能,以及不同静态随机存储器单元直流特性.通过60Co-γ射线辐照实验,测试分析了基于LB MOS器件的静态随机存储器单元随辐射总剂量的变化情况.

实验结果表明,LB MOS相比传统FB MOS成功抑制了浮体效应,并且DIBL和BVds特性得到了改善.由于采用特殊体接触设计,相比于TB MOS具有面积更小、连接方便的优点.而且工艺上与现有SOI CMOS完全兼容,无需额外的掩模版.所以,LB MOS适用于大规模集成电路.6T LB SRAM cell与6T TB SRAM cell具有类似的电学特性,但是节约大约22%的面积,且性能明显优于6T FB SRAM cell.在辐射环境中,采用体接触LB MOS器件的静态随机存储器单元在漏电流和读取静态噪声容限指标上明显优于传统FB MOS静态随机存储器单元.实验结果表明,6T LB SRAM cell具有辐照环境下稳定可靠的实用价值.