一种小型化设备方案的设计与实现

2019-08-15王磊

王磊

摘 要:为解决现有通信设备体积、功耗大的问题,文中提出一种小型化设备的设计及实现方案。方案主要由数字信号信息处理和收发信道两部分组成,使用高性能SoC处理器代替现有设备中的DSP及FPGA等处理器,使用基于捷变频器件AD9164设计的数字跳频本振源代替模拟跳频本振源,使用射频直接发射技术代替模拟上变频混频技术,简化了设备数字电路及模拟电路的设计难度,有效降低了设备的功耗、减轻了设备重量、缩小了设备体积。对方案设计中的系统启动加载流程及通信能力进行测试验证,测试结果表明,方案可满足现有通信设备的需求,对后续设备的小型化、轻量化设计具有指导意义。

关键词:AD9164;小型化;射频直接发射;SoC处理器;通信;轻量化

中图分类号:TP39文献标识码:A文章编号:2095-1302(2019)07-00-02

0 引 言

现有通信设备由中频信号处理、数据处理、接收信道、发射信道及射频前端组成,中频信号处理及数据处理组合使用多种处理器实现数字信号处理及数据解析等功能,接收信道使用二次混频电路实现下变频功能,发射信道使用复杂的模拟电路实现上变频功能,多种专用处理器及模拟混频电路的使用使得现有设备的质量、体积、功耗都较大。随着SoC技术及数字电路技术的高速發展[1],完全可对中频信号处理、数据处理及收发信道进行数模一体化设计。

本文提出一种小型化设备设计方案,给出了设计框图及实现方法。该方案采用数模一体化设计思想,使用高性能SoC处理器代替现有设备中的多种专用信号处理器,使用数字本振源代替模拟本振源,使用射频直接发射技术代替模拟上变频混频电路,降低数字电路及模拟电路的设计难度。

1 系统设计方案

系统由数字信号信息处理、接收信道、发射信道、中频采样电路、射频直接发射电路、本振切换开关及射频自检控制组成,结构如图1所示。

数字信号信息处理分为PL和PS两部分,具有VxWorks镜像文件加载、系统收发流程控制、收发电路参数配置、数字信号处理算法及状态检测上报等功能。

中频采样电路对接收信道输出的中频信号进行模数变换后送入数字信号信息处理模块进行后续处理。

射频直接发射电路使用高性能AD9164器件和放大滤波电路实现上变频功能,在系统处于发射模式时将基带信号上变频为射频信号后输出,在系统处于接收模式时产生所需的快跳本振信号。

接收信道完成对射频信号的预选滤波、一次混频及放大处理,发射信道对射频直接发射电路输出的射频信号进行放大滤波后输出。

本振切换开关在系统处于发射模式时将射频信号送入发射信道,在系统处于接收模式时将射频信号送入接收信道的混频器作为本振源使用。

射频自检控制由一组开关组成,系统处于射频自检模式时将发射信道产生的信号直接回环到接收信道进行处理,处于正常模式时将射频接收信号送入接收信道、将发射信道输出信号送往射频前端。

2 数字信号信息处理设计

数字信号信息处理部分使用高性能SoC处理器实现现有设备的中频信号处理及数据处理功能,分为PL和PS两部分[2],在PL中实现中频信号处理功能,在PS中实现数据处理功能。PS为两个主频为800 MHz的ARM Cortex-A9内核[3],按照功能划分为CPU0和CPU1,CPU0负责处理器上电初始程序加载、VxWorks系统运行及数据处理软件运行;CPU1运行信号处理软件完成收发状态控制、数据解析等功能。系统控制流程如图2所示。

设备加电后首先加载FSBL,然后依次加载VxWorks镜像文件和PL bit文件,最后加载并运行CPU0及CPU1程序。程序运行后首先初始化所有外围接口,随后读取配置状态,如果配置失败则重新配置,配置成功后分别进行基带自检和射频自检,并上报自检结果,自检无故障则根据时隙任务进行正常收发通信并进行周期自检,自检有故障则根据故障类型进行排故处理,之后重新加电运行。

3 收发信道设计

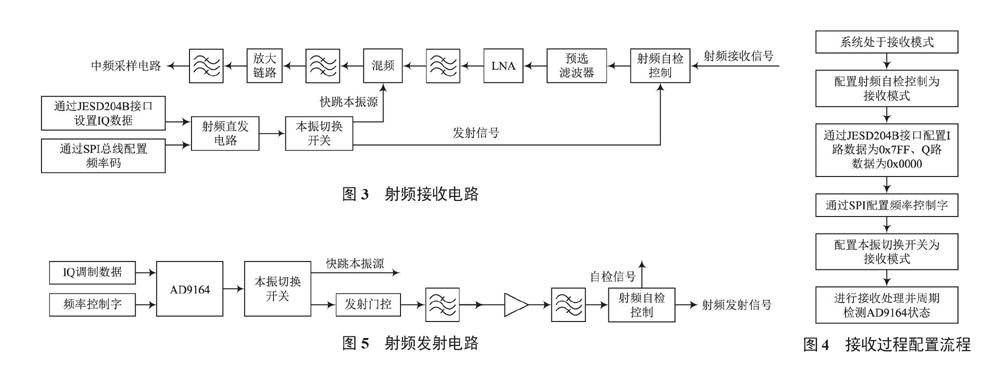

接收信道使用一次混频电路代替原有的二次混频电路,使用数字快跳本振源代替模拟快跳本振源,简化电路结构设计,接收电路框图如图3所示。

接收信道首先对射频接收信号进行预选带通滤波、LNA放大,然后通过混频器进行下变频,最后经中频滤波后送入中频采样电路进行模数变换。通过配置射频直接发射电路来产生数字快跳本振信号,实现流程如图4所示。

发射信道采用高性能AD9164和滤波放大电路实现射频直接发射功能,射频发射电路设计如图5所示。

系统处于发射模式时,首先经JESD204B接口设置IQ调制数据[4],然后通过SPI总线配置相应频率控制字,最后对AD9164上变频产生的射频信号进行放大滤波后输出。本方案中配置AD9164为24倍内插模式,工作模式为NCO基带直流模式[5],内核采样速率fDAC为5.76 GHz,频率控制字为48 bit,计算方式:

4 测试验证

由系统控制流程可知,设备加电启动后首先加载FSBL,然后依次加载VxWorks镜像文件和PL bit文件,最后加载并运行CPU0和CPU1中的应用程序,加电启动流程如图6所示。

由图6可知,系统的加电启动控制符合设计要求,待所有程序加载运行成功后,使用发送通信测试数据方式进行性能测试,测试结果如图7所示。

根据测试结果可知,发送端发送5 000组通信测试数据后,在接收端可以完整接收到5 000组通信测试数据,且无丢包和误码,满足通信设计要求。

5 结 语

本文采用数模一体化设计方法,提出一种小型化设备设计方案,给出设计框图及实现方法,并验证了方案的可行性。与现有通信设备相比,该方案可以简化数字电路及模拟电路的设计,有效降低设备功耗、减轻设备重量、缩小设备体积、简化数据交互控制时序,为后续设备的小型化、轻量化设计提供新的设计思路和参考依据,具有广阔的应用前景。

参 考 文 献

[1]陆启帅,陆彦婷,王地,等.Xilinx Zynq SoC与嵌入式Linux设计实战指南[M].北京:清华大学出版社,2014.

[2]符晓,张国斌,朱洪顺.Xilinx ZYNQ-7000 AP SoC开发实战指南[M].北京:清华大学出版社,2015.

[3] Xilinx.Zynq-7000 All Programmable SoC Technical Reference Manual[Z].2014.

[4]亚德诺半导体.JESD204串行接口和JEDEC标准数据转换器[Z].

[5] AD9164:16-Bit,12 GSPS,RF DAC and Direct Digital Synthesizer,Analog Devices[Z].

[6]张清联.浅谈NFC手机非接触式射频接口测试方法[J].物联网技术,2018,8(8):45-47.

[7]金骏,王旭云,孙晨,等.一种小型化高可靠USB测控应答机的设计与实现[J].信息通信,2016(3):70-73.

[8]薛猛,冯占群.一种小型化PLL电路的设计方案[J].产业与科技论坛,2013,12(11):73.

[9]王钰.基于AD9164的小型化设备研究与实现[J].物联网技术,2018,8(6):57-59.

[10]吴律.小型收发信机设计与实现[D].西安:西安电子科技大学,2014.