低成本功能可扩展虚拟示波器研制及验证

2019-08-15李丰璞包建荣郭春生

姜 斌,李丰璞,包建荣,刘 超,郭春生

(杭州电子科技大学 a.通信工程学院;b.信息工程学院,杭州 310018)

0 引 言

作为常见的电子测量仪,示波器能测量并显示信号波形及相关参数,已被广泛用于各类科学研究及生产实践[1-2]。随着集成电路和信息技术的发展,传统示波器波形不稳定、测读易老化而不准确、功能单一等缺点逐渐突显,已无法满足现代科研和测量等诸多应用。其中,国内一些理工类高校实验室常使用国产数字示波器辅助本科教学,其成本区间约为1 000~3 000元,其中,电信类科研实验室使用的一些国外多功能示波器价格高达万元,成本高昂,购买不易[3]。

虚拟示波器主要将计算机和现代测量技术融合,使用软件代替传统示波器部分硬件功能,利用计算机显示器代替传统示波器物理面板[4]。相比传统示波器,虚拟示波器在波形显示,功能多样化,成本控制等方面都更具有灵活可配置及低成本等优势[5]。但现有的虚拟示波器仍存在成本较高,信号处理接口不公开,难以扩展信号处理算法而无法适应不同测试场景等缺陷。基于此,本文使用压缩感知(Compressed Sensing,CS)信号处理技术,并将STM32单片机、现场可编程门阵列(Field-Programmable Gate Array,FPGA)等模块与个人微机(Personal Computer,PC)结合作为硬件平台,研制了具有50 MB带宽,100 MS/s采样频率的低成本功能可扩展虚拟示波器。该示波器在优化了传统示波器的信号波形显示、测量等功能的基础上,还实现了频谱分析、扫频输出及幅频测量等信号特征显示的扩展功能,具有配置灵活,功能多,成本低廉,便携性好等优势,便于教育界和工业界的大批量推广应用。

1 虚拟示波器结构与应用场景

该虚拟示波器的整体布局由高速通用串行总线(Universal Serial Bus,USB)数据采集模块与PC软件信号处理端两部分构成。高速USB数据采集模块采用STM32单片机与FPGA模块为核心组成的集成式结构。其中,FPGA模块负责高速数字信号处理,包括高速数据采集和缓存;STM32单片机为高速USB数据采集模块的主控制器,主要完成了数据流控制与传输并通过控制USB接口完成数据采集模块与PC软件信号处理端的对接。PC软件信号开发使用微软公司的Visual Basic编程语言,一方面通过高速USB接口接收下位机发送的波形信号,利用软件编程完成各波形显示、测量以及变换,实现虚拟示波的窗口化显示;另一方面向数据采集模块发送各类指令,使虚拟示波器实现信号发生器、频谱仪、扫频仪等新型功能。该虚拟示波器的典型应用场景如图1所示。

图1 虚拟示波器应用场景图

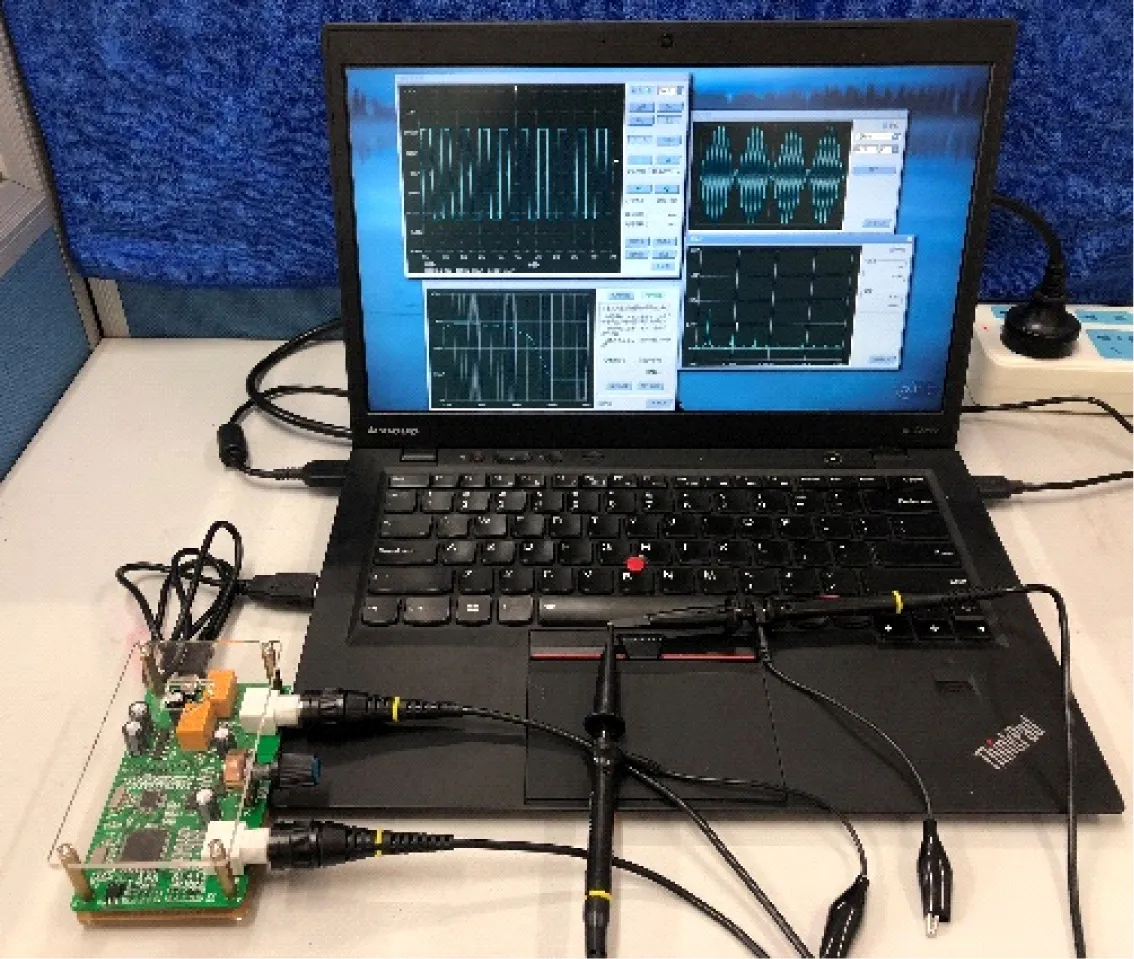

图1同时展示了该多功能虚拟示波器的两种应用场景。左侧所示为下位机与便捷式PC相连构成的虚拟示波器。数据采集模块未封装体积约为10 cm×7 cm×3 cm,不到传统示波器体积的5%,其便携性相比传统示波器有质的提升[6]。该下位机与便携式电脑的组合非常适合个人携带,可应用于各类现场测试和生产实践,并极大降低了运输及人力成本。右侧为实验室科研及教学应用场景,本新型虚拟示波器同时具备信号发生功能,集成下位机于PC上位机相结合可同时实现示波器功能及信号发生器功能,可同时代替传统示波器以及传统信号发生器,集成下位机制造成本低廉,大大节省了电信类实验室科研和教学的费用成本。

2 硬件结构设计

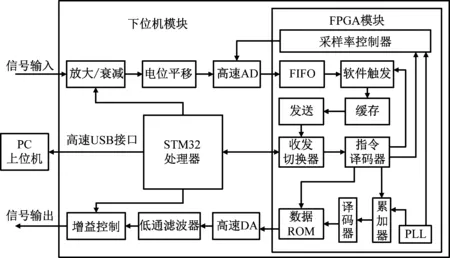

虚拟示波器的硬件模块框图如图2所示。其中,数据采集模块主要包括了模拟信号预处理接口芯片、高速AD/DA转换器、STM32核心处理器、FPGA信号处理芯片、高速USB接口芯片及其配套的电源管理等外围芯片与线路。

图2 虚拟示波器硬件模块设计框图

2.1 模拟信号预处理接口

硬件模块由集成运放电路OPA2356芯片和模拟开关CD4053芯片组成,并实现两个功能。首先,对该系统示波器功能中的输入信号做预处理,通过分压电阻及旁路电容对输入信号滤波,实现信号的放大、衰减和电位平移,从而使得输入信号位于AD采集范围之内,避免波形失真;其次,对该系统信号发生器功能中的信号输出处理,该模块接收到高速DA转换器发出的模拟信号后,先通过低通滤波处理,再根据STM32给出的指令完成信号的放大或衰减,最后将模拟信号输出。

2.2 高速AD/DA转换器

高速AD转换模块利用压缩感知算法,压缩进入AD芯片的信号,降低了信号最小采样频率,从而提高AD采样效率。同时,降低芯片功耗和成本。AD芯片选择满足采样频率≥100 MS/s的低功耗芯片。DA转换器模块负责完成信号发生器功能中的信号转换工作,该模块由2个四位T形权电阻网络串联组成,具体包括电阻网络、缓冲寄存器、模拟开关以及运放电路4部分,将FPGA模块发出的数字信号转为模拟信号,完成信号发生器的波形输出。

2.3 STM32核心微控制器

模块主体为一块STM32集成芯片,该集成芯片拥有多个功能模块,使用各模块自带的固件库大大简化了设计开发难度且降低了成本,使用STC-ISP烧写软件,将通过Keil编写的固件程序下载至STM32中[7]。当系统实现示波器功能时,STM32芯片控制运放电路对进入AD转换器的模拟信号放大、衰减等处理,使其不超过采集范围,然后接收经过AD模块以及FPGA模块处理的信号并通过高速USB模块将信号传输至上位机。当系统实现信号发生器功能时,STM32通过高速USB模块接收上位机发出的指定波形数据,再将该数据发送给FPGA模块,通过DA转换器以及模拟信号处理模块后输出。

2.4 FPGA信号处理芯片

如图2所示,为了同时实现虚拟示波器、信号发生器以及扫频仪等功能,需在FPGA中开辟多个功能区域,实现采样频率控制、先进先出(First Input First Output,FIFO)数据缓冲、锁相环(Phase Locked Loop,PLL)时钟同步及只读存储器(Read-Only Memory,ROM)存储。当系统实现示波器功能时,模拟信号经AD转换器变为数字信号进入FPGA模块中的FIFO数据缓冲区,再根据触发条件将所需数据传给STM32。同时,FPGA模块对高速AD转换器下达采样频率数据指令。当系统实现信号发生器功能时,FPGA模块将STM32波形数据写入ROM表。同时,对PLL时钟模块的频率数据累加及译码。最后,FPGA模块将ROM表中的波形数据按一定频率发给DA转换器。

2.5 高速USB接口

STM32芯片内置一个兼容全速USB(12 MB/s)的设备控制器,且端点可由软件自由配置[8]。高速USB接口模块实现了数据采集模块与PC软件信号处理端的实时数据交换,根据本集成架构特性,设置其传输带宽为50 MB。同时,下位机USB端口采用MiniUSB接口,压缩了下位机体积,提高了便携性。

3 软件系统设计

3.1 后端程序设计

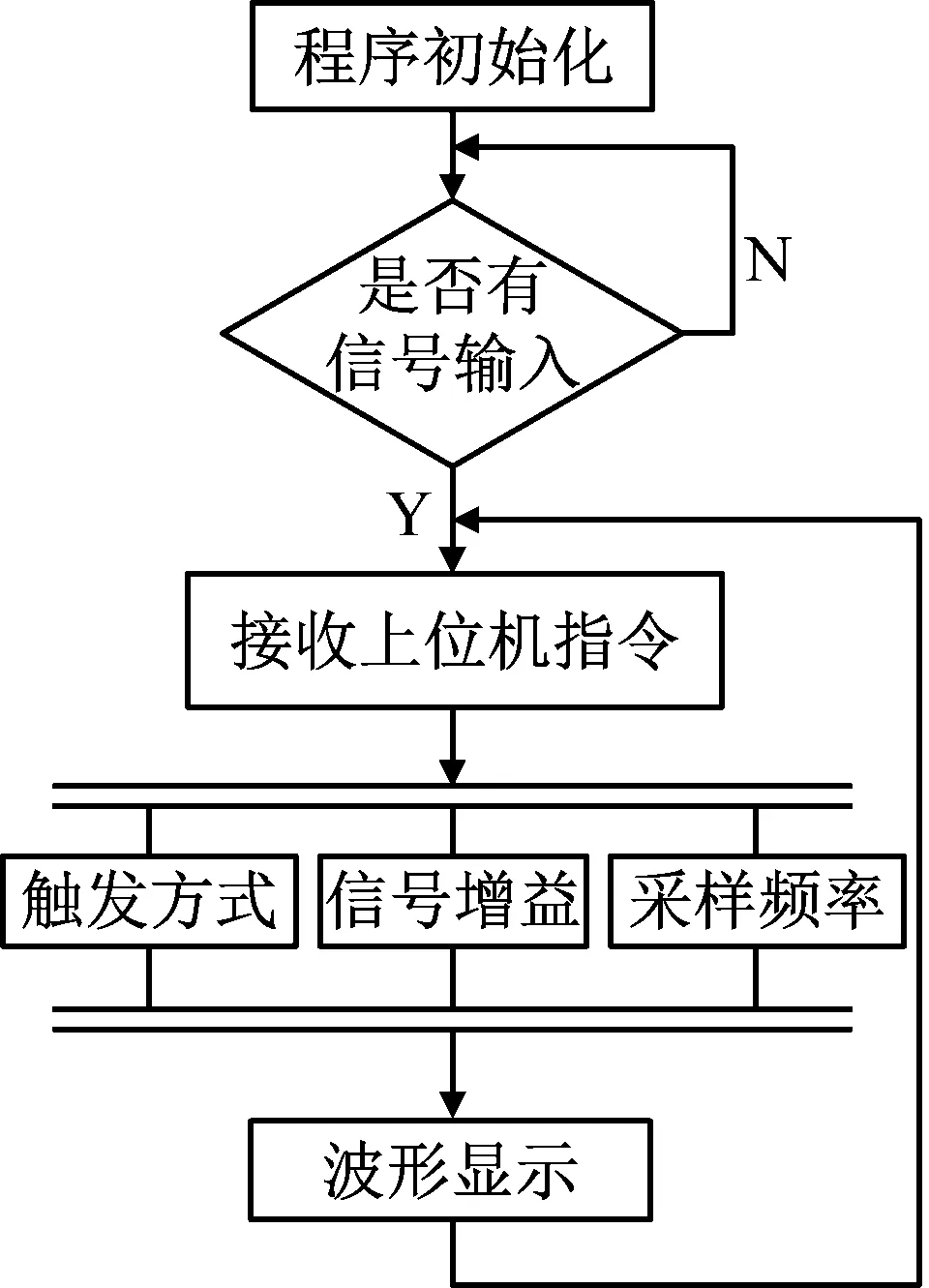

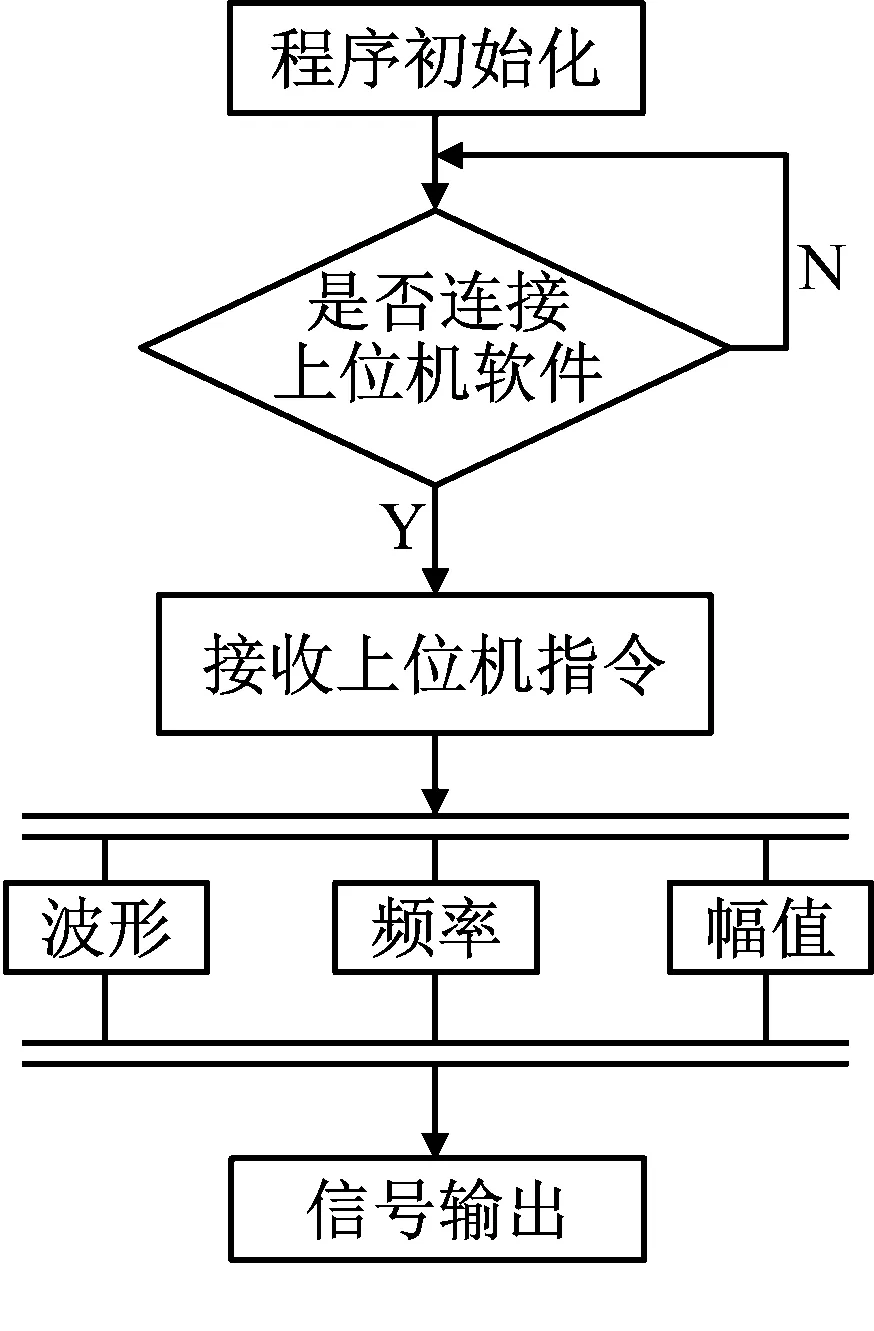

下位机固件(Firmware)程序采用Keil编程软件编写。图3所示为下位机固件程序流程图。其中,图3(a)为示波器功能流程图,下位机根据上位机指令,以指定采样频率对接收信号采样,并按指定触发方式将波形输至上位机。同时,也可对信号实现一定增益。其中,触发方式有单次,多次及连续触发3种,且信号增益效果区间为0.01~1 V/div,以满足各场景需求。图3(b)为信号发生器功能流程图,下位机按照指令,以一定波形、频率和幅值输出波形信号。

(a)示波器功能

(b)信号发生器功能

图3 下位机固件程序流程图

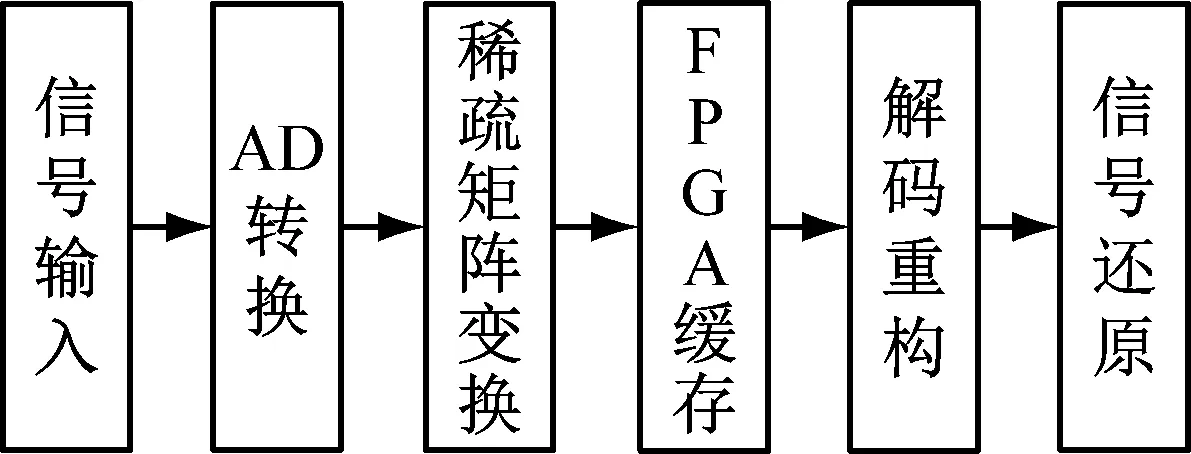

信号处理部分则采用最新的CS算法,使输入信号实现功率压缩,降低了信号最小采样频率,从而加速了AD转换效率,且减少了FPGA缓存空间。压缩感知的应用流程如图4所示。

图4 压缩感知流程图

设待测信号先经AD变换至维度为1×N的离散实值信号向量X,再经稀疏矩阵变换将X表示为一组稀疏基ΨT=[Ψ1,Ψ2,…,Ψm,…,ΨM]的线性组合,且有:

(1)

式中:αk=〈X,Ψk〉;α与X是N×1矩阵;Ψ是N×N矩阵。当X在某组基Ψ上仅有K≤N个非零系数αk时,称Ψ为信号向量X的稀疏基。该公式将X投影变换至稀疏投影区间,减小了信号功率,经稀疏变换压缩的信号输入FPGA缓存模块,即可极大减少储存需求,降低成本。接着,通过稀疏向量计算:⊗=ΨTX,得出压缩采样的观测部分,并解码重构信号。该过程主要围绕观测矩阵φ,其选择是为了得到M个观测值:yj=〈Θ,φj〉(j=1,2,…,M),以确保重构完整X,获得的观测向量

Y=φΘ=φΨTX=ACSX

(2)

式中:ACS=φΨT,且ACS为CS信息算子。该公式也可表示为X经矩阵ACS实施非自适应观测。最后,利用0—范数优化问题求解X的精确或近似逼近值,完成信号的还原[9-10]:

(3)

3.2 前段软件设计

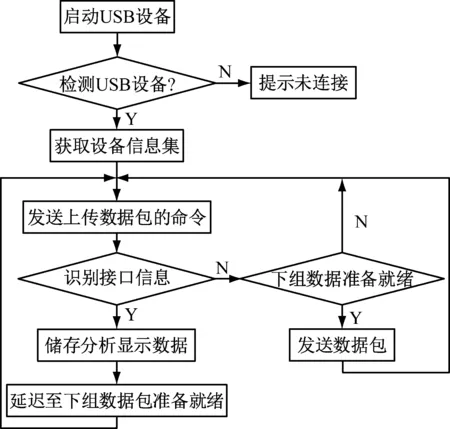

上位机软件实现了该虚拟示波器的可视化操作以及多功能开发,其开发平台为VB,易于实现窗口化、模块化设计[11-12]。上位机软件至下而上可分为USB驱动模块、功能实现模块以及UI模块。USB驱动模块调用STM32自带的USB接口相关程序库,以实现在Windows操作系统下的自动安装,USB的数据链采集与分析流程如图5所示。

图5 USB数据链采集与分析流程图

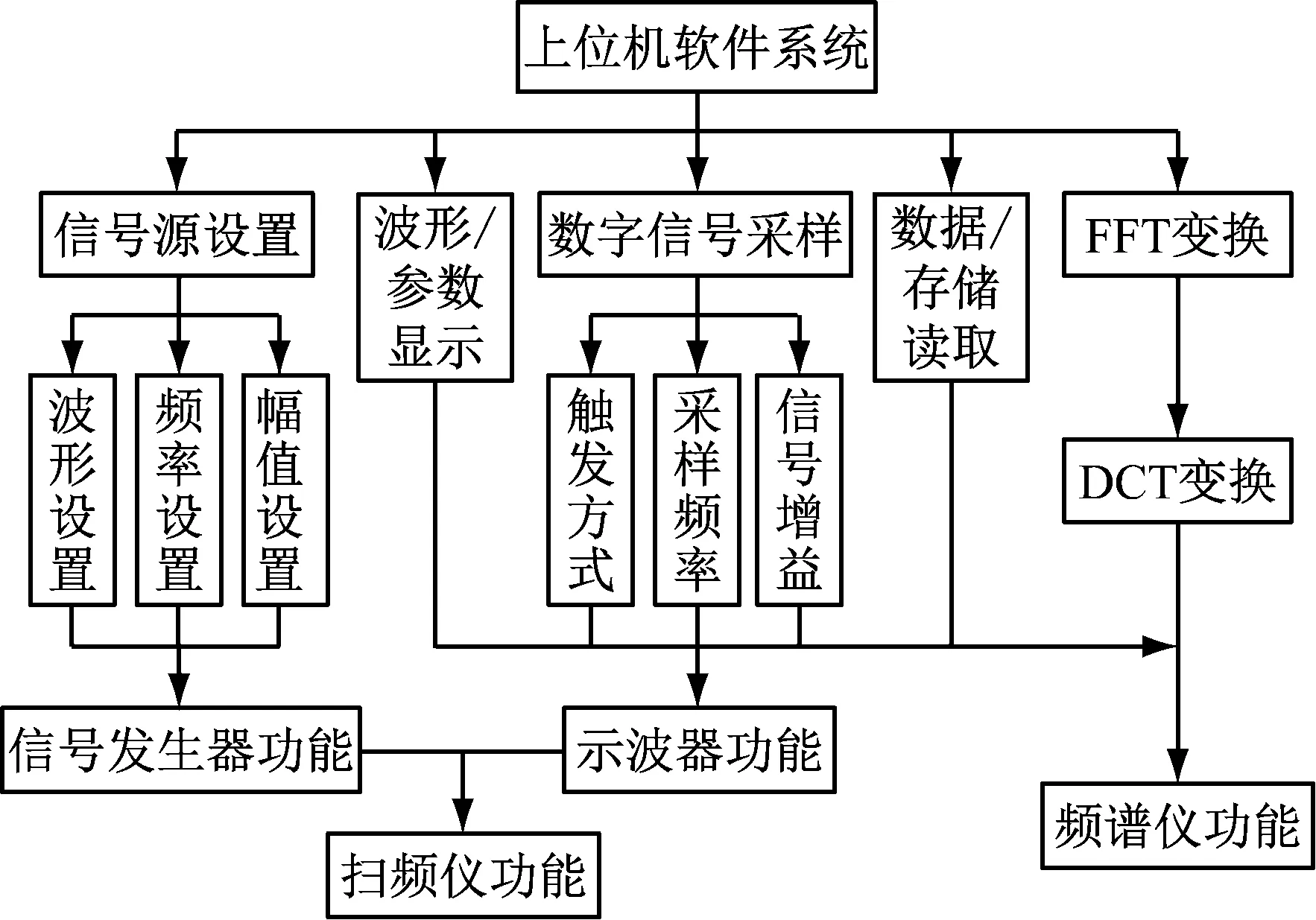

虚拟示波器的功能实现模块如图6所示。上位机通过VB编程实现以下5类数据处理:信号源设置、波形/参数显示、数字信号采样、数据存储/读取、快速傅里叶变换,通过信号源设置对下位机下发相关指令(波形、频率、幅值)以实现该系统的信号发生器功能;通过对接收信号采样、数据存储/读取及波形/参数显示处理,以实现示波功能;通过对采样波形信号的快速傅里叶变化实现频谱仪功能,实现功能拓展,完成DCT变换;此外,将下位机信号发生器的信号输出端口与示波器信号输入端口相连接,同时上位机通过信号源设置,使下位机发出频率可变的扫频信号,再利用示波器功能测量信号,输出对应的幅值变化,绘制成幅频特性曲线,从而实现该系统的扫频仪功能。

图6 上位机软件功能流程图

4 虚拟示波器样机测试及效果

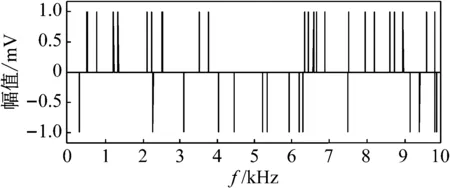

本文主要通过对待测信号的频率响应测试,验证压缩感知对该示波器波形显示的影响。如图7所示,输入一个随机复频信号,将未使用压缩感知的信号与通过压缩感知压缩还原的信号的频率响应对比,其频率响应基本一致。压缩感知使得该虚拟示波器的采样频率范围提高了25%~30%,采样速度提高了近35%。因此,除了极大地增加了AD芯片采样效率,还释放了FPGA缓存空间,降低了制造成本[13-14]。

(a)原始信号

(b)接收信号

图7 CS技术频率响应图

压缩感知提高了AD采样效率,但使FPGA的输入与输出时钟域不同步。另外,为了防止FPGA数据溢出,在FPGA模块中使用异步FIFO结构。异步FIFO结构实现了对数据流的缓冲,使得速率较高,间隔较大的写入数据变得平滑均匀,减少了空信号出现,增大了信号突变容错率,从而有效防止了信号数据的溢出和丢失[15]。

通常,高功耗会使USB数据采集器因温度过高而无法长期工作。为了保证该虚拟示波器长时间稳定运行,在USB传输模块中,使用了门控时钟屏蔽技术及动态调频技术,以降低功耗。门控时钟屏蔽技术使虚拟示波器在运行指定功能时,可断开不相关模块的时钟和电源,且激活必要的运行模块,从而降低静态功耗。动态调频技术根据各芯片工作的不同状态,调节各模块运行频率和电压,降低了系统运行动态功耗[16]。

为防止该虚拟示波器产生电磁干扰(Electromagnetic Interference,EMI)且减少静电放电(Electrostatic Discharge,ESD)现象,下位机印制电路板板信号走线皆于同一层,且靠近电源层,实现电磁屏蔽;电源层使用低数值电感,减少瞬态信号,降低共模EMI;在芯片引脚间增加了特定分压电阻和二极管等元件组成的ESD保护电路,在确保芯片正常工作的同时,防止静电产生。

经过样机实验测试,获得该虚拟示波器的参数结果如表1所示。

表1 低成本可扩展虚拟示波器的验证参数表

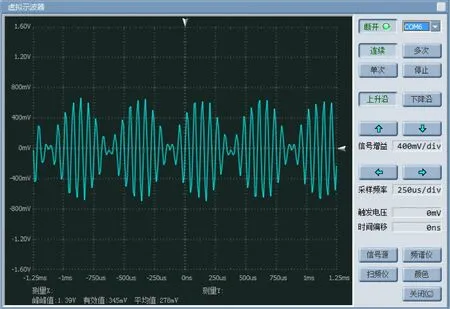

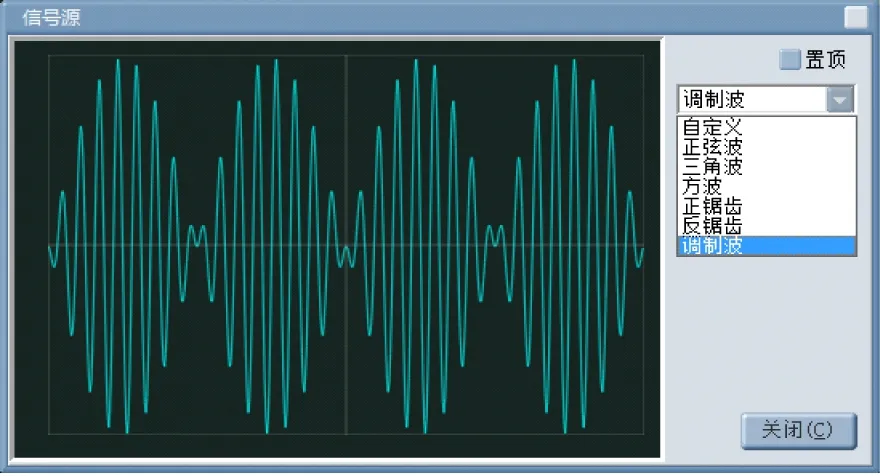

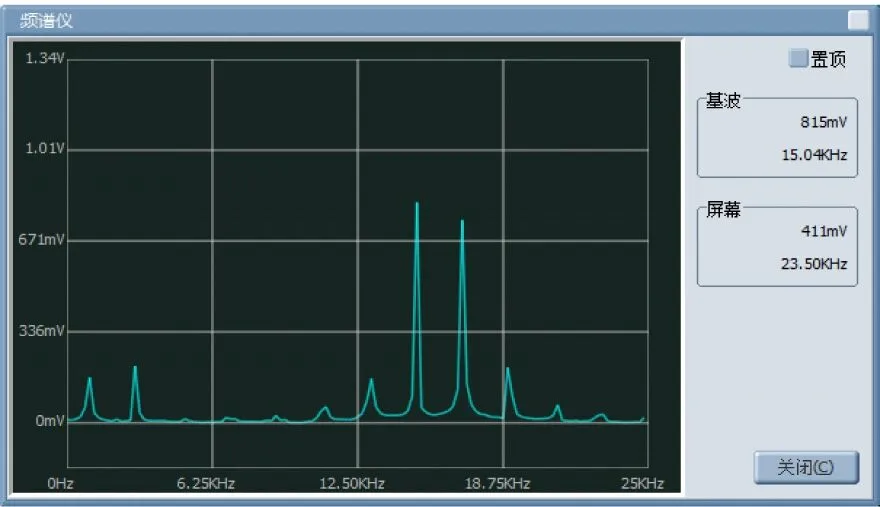

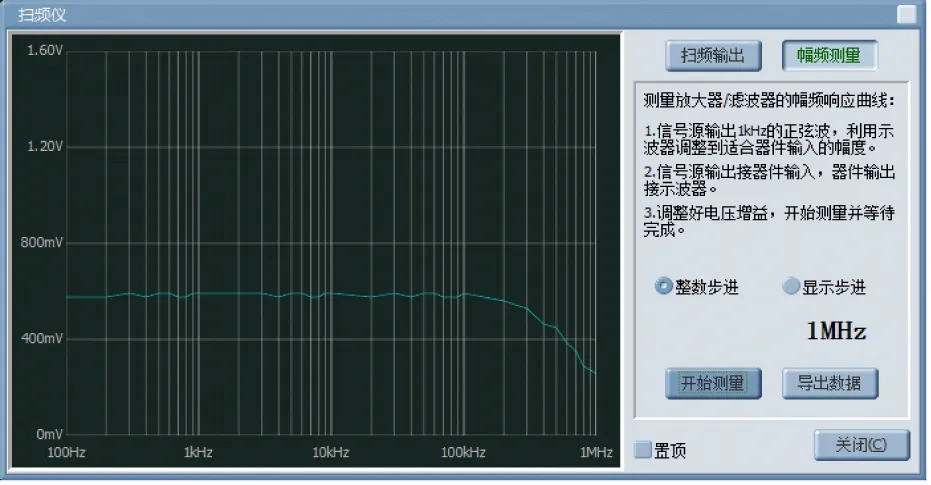

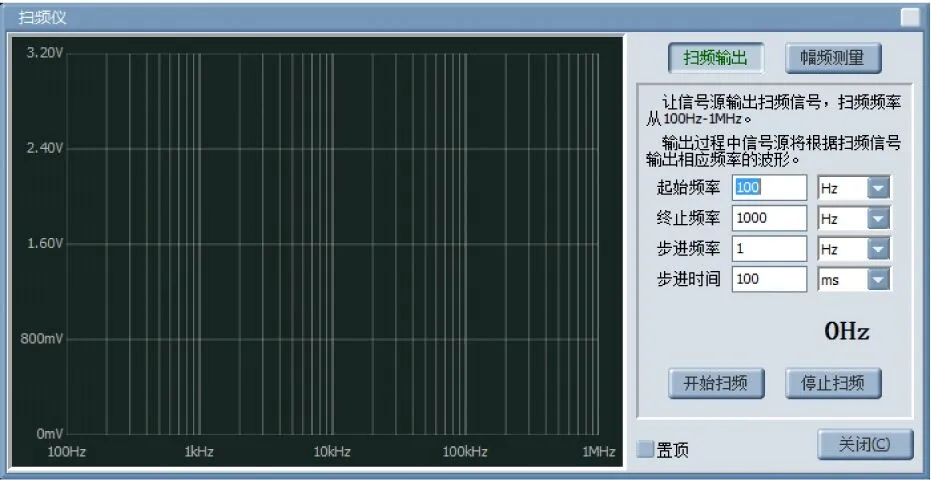

前端用户界面设计参考传统数字示波器界面,多以按钮形式呈现,达到实现简洁、直观的交互体验。图8所示为虚拟示波器的主界面,左侧为波形显示窗口。当前波形窗口展示了由该示波器自身信号源产生频率为1 kHz的调制波。右侧为功能控制区域,集成了示波器、信号发生器、频谱仪以及扫频仪功能。图9所示为信号发生器及频谱仪功能界面,信号发生器功能支持多种波形输出。而频谱仪界面左侧显示了频域波形,右侧提供了基波数据以及屏幕测读功能。图10所示为扫频仪功能界面,扫频仪具有扫频输出和幅频测试两种功能,满足了不同应用场景。图11为该新型多功能虚拟示波器的样机演示图。

图8 虚拟示波器主界面

图9 信号发生器及频谱仪功能界面

图10 扫频仪功能界面

图11 样机测试效果的展示

由于AD芯片量化器为8 bits,该虚拟示波器的垂直分辨率上限无法改变。故对采样信号用平均及高分辨率运算,增加了其噪声失真比,提高了系统整体有效位数,优化了波形显示分辨率。平均算法即在捕获周期信号时,先设定一个平均次数N,然后采样N段触发位置相同的信号。最后,经平均运算得到最终波形,并输出。该方法降低了随机噪声且未减少带宽,进而增加了噪声失真比。而高分辨率算法对固定时间间隔内的M个采样点进均计算,对波形平滑处理,极大地提高了分辨率。经测试通过分辨率优化处理,使整体系统有效位数从8位增加到接近12位,分辨率性能提升了约50%。

5 结 语

本文研制的采用CS信号处理技术的虚拟示波器,在优化了示波器基本波形显示、测量等功能基础上,还实现了频谱分析、扫频输出及幅频测量等信号特征显示的扩展功能,具有配置灵活,功能多,成本低廉,便携性好等优势,便于教育界和工业界的大批量推广应用。同时,该系统在软件方面仍存在灵活的扩展空间。其在稳定性,测量精度及功能复杂度等方面,还可通过软件编程及改进而进一步扩展。