基于FPGA数字视频自动倒换器的设计与实现

2019-08-02许卫行展再铭江苏省广播电视总台

许卫行 展再铭 江苏省广播电视总台

1.概述

为提高安全播出的可靠性,广播电视信号系统中一般具有几路不同路由、不同传输方式的相同SDI数字视频信号源,经过自动倒换设备(2选1、3选1等)选择一路信号输出,这样,即使一路输入信号因故中断,也不会影响最终的安全播出。

常规的SDI数字视频自动倒换设备一般只对SDI同步进行检测,不同时对视频内容(如黑场、彩条、静帧等)、嵌入音频的状态做全面的分析,难以满足广播电视安全播出需要。为此,我们自主研发4选1数字视频SDI倒换器,能对视频的帧内容进行检测,实现安全可靠的信号倒换。

2.技术特点

(1)基于FPGA设计,对所有视音频状态实时对比,同时实现对SDI信号丢失、黑场、75%彩条、100%彩条、静帧、音量的快速检测,按照优先级进行自动倒换,对输入信号判断的准确性、快速性大大提高。

(2)自适应的静帧检测。通过移动物体检测和像素变化统计等方法进行静帧检测,其中,移动物体能被快速检测,单色场需要一个较长的时间进行对比判决(单色场默认5秒),无规则的静帧则需要更长的统计时间(默认10秒)。

(3)倒换条件和参数可自定义,如信号丢失,黑场、彩条、静帧、伴音音量、静帧时间、伴音丢失时间等。

(4)设备最终采用全硬件实现,无软件跑飞及死机现象。

(5)均衡后的SDI信号由FPGA进行时钟再生、解扰、解码、音频解嵌、压缩、检测的全部过程,全部由FPGA完成,节省成本的同时,增加了系统的集成性。

(6)三种倒换模式可选,自动、主备、主从。

3.方案设计

图1描述的是4:2:2的YCbCr视频数据流和行、场同步所用的控制信号。一帧图像数据由一个625行、每行1728字节的数据块组成。其中,23-311行是偶数场视频数据,336-624行是奇数场视频数据,其余为垂直控制信号。

图1 BT.656每行的数据结构

每行开始的288字节为行控制信号,开始的4字节为EAV信号(有效视频结束),紧接着280个固定填充数据(80-10),最后是4字节的SAV信号(有效视频起始)。后面是视频数据信号,排列顺序为Cb-Y-Cr-Y。EAV和SAV信号有3字节的前导:FF、FF、00;最后1字节XY表示该行位于整个数据帧的位置及如何区分SAV、EAV,最高位bit7为固定数据1;F=0表示偶数场,F=1表示奇数场;V=0表示该行为有效视频数据,V=1表示该行没有有效视频数据;H=0表示为SAV信号,H=1表示为EAV信号;P3-P0为保护信号,由F、V、H信号计算生成;P3=V异或H;P2=F异或H;P1=F异或V;P0=F异或V异或H,EAV/SAV中XY字节各个比特的含义见图2。

图2 EAV/SAV中XY字节各个比特的含义

在数字视频中,存在行辅助数据区“HANC”(Horizontal Anicillary Data)和场或帧辅助数据区“VANC”(Vertical Anicillary Data)。附属数据标志ADF表征数据包的开始,ADF由三个字的序列组成,其数值为:00,0hFF,0hFF。数据标识DID(Data ID)规定附属数据包中用户数据字所运载数据的内容和性质。目前辅助数据最大的用途是放置音频,称为嵌入式音频。

本设计实现四路SDI数字视频信号的自动倒换,整体框图如图3所示。

整体设计基于FPGA,4路SDI信号经过均衡、时钟再生后进入FPGA,FPGA分别进行声音的解嵌、视频采集、音频采集。采集每一路SDI信号的视频内容状态和音频内容状态,按照预先设定的切换条件,自动选择一路最优信号输出。

串口驱动模块将各路视频、音频数据发送到RS232串口,送给计算机进行彩条显示、报警、记录等处理;LED灯显示当前设备的工作状态,这些状态也通过串口和网络数据输出,进行集中监控。

4.FPGA程序设计

系统主要功能由FPGA芯片实现,主要分为以下几个模块组成。

4.1 MUX模块

实现SDI信号的分配、调度,此处需实现信号的高速处理,信号分别分配至后级采集模块,同时还受切换逻辑控制,选择不同的信号源输出。

4.2 音频解嵌模块

系统总共有4个音频解嵌压缩模块,分别解出4路SD-SDI信号内嵌入的音频。具体实现功能如图4。

4.3 时钟再生模块

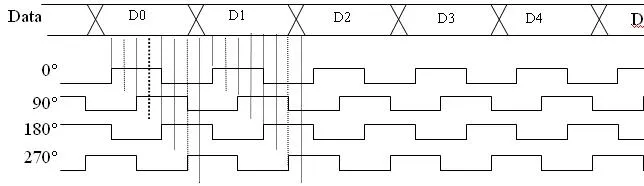

利用FPGA内部的PLL输出的多相位时钟对进来的270M串行流进行数据过采样(Over Sampling),进行数据和时钟的再生,本方案通过4相位过采样实现,如果需要5倍过采样速率,则需要的时钟频率是:5270/4=337.5MHz 。如果不采用多相位过采样方式,则需要的频率是5⋆270=1350MHz,在FPGA设计中是很难实现的,图5是采样时序。

图3 系统整体框图

图4 音频解嵌模块

图5 采样时序

4.4 解码解扰模块

SDI传 输 的 是 NRZI(NRZ-I No Return Zero-Inverse 非归零反相编码)码,在NRZ-I编码方式中,信号电平的一次反转代表比特1。就是说是从正电平到负电平的一次跳变,而不是电压值本身,来代表一个比特1,0比特由没有电平变化的信号代表。NRZI优点在于每次遇到比特1都发生电平跳变,方便接收端时钟重新同步。根据统计,连续的比特1出现的几率比连续的比特0出现的几率大,因此对比特 1的连续串进行同步就在保持整体消息同步上前进了一大步。由于也可能出现连续的0,一般NRZI会和扰码同时使用。SDI的解码和解扰通过进行X+1和 X9+X4+1计算实现。

4.5 解串模块

解串模块分析数据流内的TRS(EAV/SAV)将数据并行化输出。10bit的并行数据最终给后续音频解嵌模块使用。

4.6 音频解嵌模块

该模块对音频进行解嵌,解嵌框图见图6。

图6 解嵌框图

数据采集模拟通过“输入状态机”检测数据流内的ADF序列,鉴别不同的DID,将监测到的音频数据放到FIFO内,程序同时需要监控FIFO的状态,防止溢出或空载。数据最终通过“输出状态机”将不同组(GROUP),不同对(PAIR),不同通道(CHANNEL)的数据正确的输出。音频控制包的作用是为接收端提供必要的解码信息,如音频通道对的取样频率和同步/异步指示、通道的有效性指示以及通道对音频/视频时延等。音频控制包位于场消隐切换点之后的第二个行辅助数据区内,即位于奇数场的第8行和偶数场的第321行。每场传送一次, 音频控制包中含有音频帧序号、取样频率和各通道音频/视频间的相对时延等信息,对于48KHz同步运行模式,音频控制包的传送是可选的,但对其他运行模式,则是必需的。

4.7 视频采集模块

FPGA内部有4个视频检测模块,每路视频检测模块实现同步分析、黑场分析、100%彩条分析、75%彩条分析、静帧分析五个功能。

(1)同步分析。判断是否有SDI信号输入。(2)黑场分析。在数据流中的排列顺序为Cb-YCr-Y,其中亮度消隐电平0x10,白峰值数字电平(0xFB),有效像素范围:10-FB;色度具有极性:0用0x80表示,最大0xF0/0x10。黑场是一场信号的内容全部是黑点(亮度分量Y=10,色度分量Cr、Cb=80)组成。判断一帧(两场:奇数场和偶数场)全部是该信号时,即检测到一帧黑场,进行状态输出。(3)100%彩条分析。100%彩条是经常使用的信号源,有的设备在信号输入中断时,会自动输出彩条信号,因此检测彩条也十分重要。100%彩条的组成是这样的,在屏幕上依次显示白、黄、青、绿、紫、红、蓝、黑8种竖条,其中的三基色信号的电平非1即0,由它们配出来的彩条, 没有掺白,且幅度最大, 所以称为100%饱和度和100%幅度的标准彩条。对应的Y、Cb、Cr数值见表1。

表1 Y,Cb,Cr数值表

(4)75%彩条分析。在屏幕上显示的8个彩条和100%彩条一样,只是其中三基色信号的饱和度为原来的75%。其FPGA分析过程和上面的一样,只是Y,Cb,Cr取值不一样。

(5)静帧分析。通过移动物体检测和像素变化统计等方法进行静帧检测,其中,移动物体能被快速检测,单色场需要一个较长的时间进行对比判决(单色场默认5秒),无规则的静帧则需要更长的统计时间(默认10秒)。

4.8 音频分析模块

解嵌模块已具备是否含有嵌入音频、音频采样率等信息,音频分析模块主要对音量进行分析。通过对音频数据进行峰值检波,对音量数据进行提取。

4.9 切换控制模块

该模块提取各路信号的视频、音频状态,对各路信号进行排序,自动优选一路信号输出。可以预先设置各路的切换优先级,在信号都正常的条件下,切换控制模块通过优先级切换。

4.10 其他模块

(1)串口模块:该模块将音量等状态数据发送到RS232串口,也通过该接口进行参数配置。

(2)网口模块:通过组播输出与串口相同的数据,方便客户端进行集中监控。

(3)按键模块:按键防抖处理后,将按键信息反馈至切换控制逻辑。

(4)FLASH模块:控制外围FLASH芯片的读写。(5)LED模块:指示按键状态、信号状态、切换状态。

5.电路设计和调试

SDI接口芯片选择的是TI公司的专用SDI接收芯片LMH0034、SDI驱动芯片LMH002。该组芯片性价比很高,应用广泛。LMH0034高标清自适应电缆均衡器,单片集成了SDI传输电缆均衡器功能,支持125 Mbps到1.485 Gbps,支持SMPTE 292M,SMPTE 344M和SMPTE 259M,可单端或差分输入驱动。LMH0002 SDI高标清自适应串行数字电缆驱动芯片,支持SMPTE 259M和SMPTE 292M标准,支持最高1.485 Gbps数据率。输入输出原理图如图7所示。

电路板采用Altium Designer进行原理图和PCB板的制作,Altium是基于一个软件集成平台,也是一个专业应用软件,方便快捷,容易使用,通过这个软件制作的主板实物如图8所示。

图7 输入输出电路

图8 电路主板

FPGA开发软件采用ALTERA的QUARTUS II进行编程设计。程序功能完成后通过FPGA的AS接口下载到FPGA的配置芯片内部。Quartus II是Altera公司推出的CPLD/FPGA开发工具,提供了与电路结构无关的开发包环境,具有数字逻辑设计的全部特性。

6.系统测试与调试

信号源采用TG700信号发生器,测试仪器采用泰克WVR7120波形监视器,测试结果表明各种状态、功能一切正常,图9为输出眼图,技术指标符合GY/T159-2000《4∶4∶4数字分量视频信号接口》。图10为遥控终端软件界面,实物面板和软件界面基本做到了一致。

7.结束语

方便、快捷、设备的稳定及完善的功能是整个产品设计过程主导思想,在电路的设计中还需注意接地问题,模拟接地和数字接地应分开布线,电源和地应在单独的电路板层上,由于信号线频率较高,必须考虑信号传输过程中的谐波与阻抗匹配,使系统接地获得面积宽广,电压变动较小,提高设备稳定性。

图9 输出级眼图指标

图10 终端软件界面