大容量高速回放系统设计与实现 ?

2019-07-29黄刚

黄刚

摘 要:为满足无线通信设备回放工作过程数据文件的要求,設计了一种实时高速的数据回放系统。系统采用固态硬盘作为存储介质,将Aurora高速串行总线和以太网作为数据传输接口,实现海量数据的高速实时存储和回放。系统已经在工程中进行应用验证,性能良好。

关键词:数据回放;固态硬盘;SATA 3.0;高速总线;Aurora;以太网

中图分类号:TP39;TN91文献标识码:A文章编号:2095-1302(2019)06-00-03

0 引 言

在过去的几十年里伴随着信息化的推进与无线通信技术的飞速发展,很多新的算法不断被提出。但采用新算法的无线通信设备通常需要消耗大量资源进行外场调试和验证,如果可以获得大量原始数据,那么在实验室环境就可以通过原理样机对算法进行较好的验证和优化。数据回放系统是获取真实环境中不易得到的信号的重要手段,根据文献[1-3]可知,回放系统已经在雷达、医疗、电力等领域被大量运用。一般情况下,设备将采集的数据存储于数据回放系统中,然后利用数据回放系统中的数据进行数据分析、算法验证和优化等。为了使无线通信系统的算法能够方便验证和优化,本文设计了一种大容量高速数据回放系统,首先分析了系统的整体架构和工作原理,然后对数据回放系统的硬件和软件进行设计,最后对系统做出性能评估。

1 系统总体方案

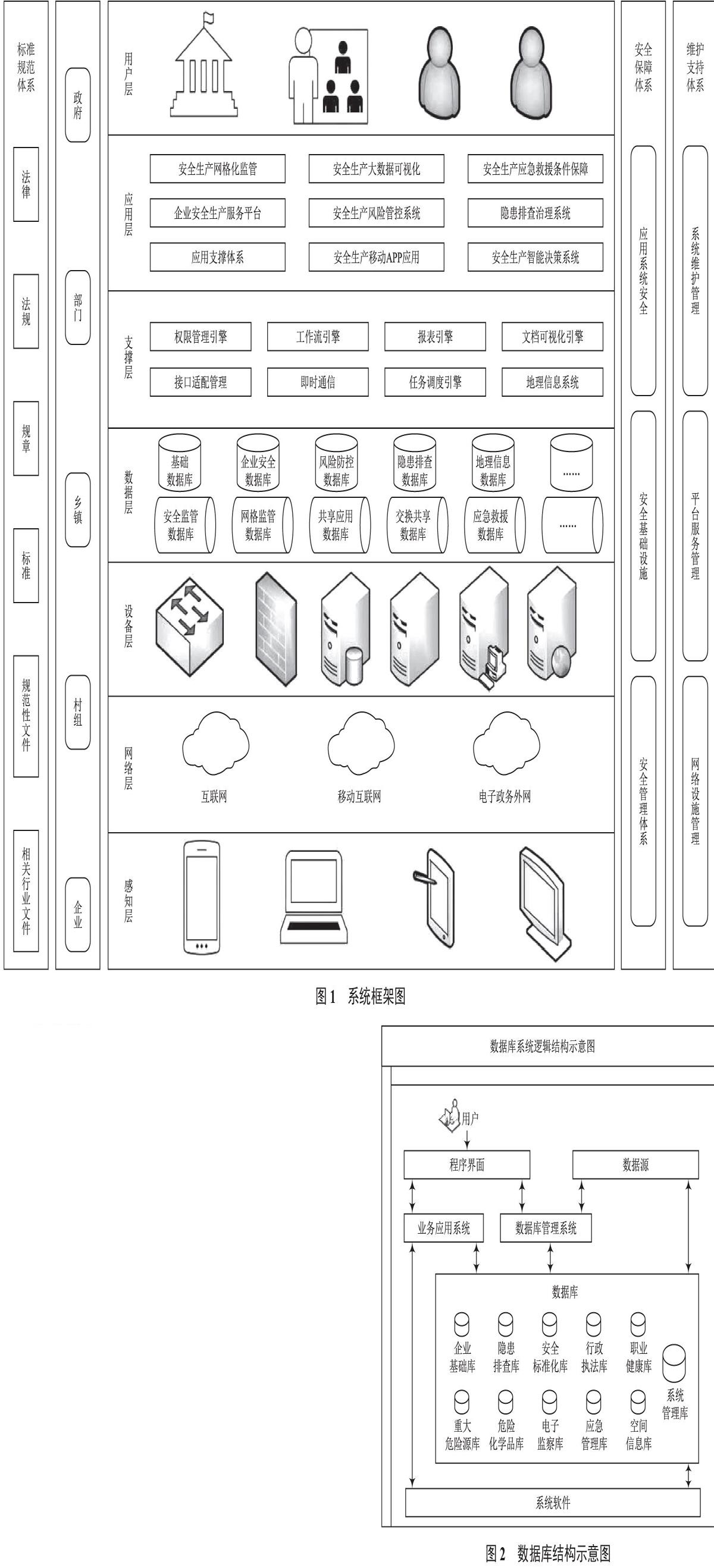

回放系统整机设备示意如图1所示。整机设备主要由信号处理系统和数据回放系统组成。数据回放系统和信号处理系统通过Aurora高速串行总线和I2C总线连接,同时数据回放系统预留以太网接口用于与计算机通信。数据存储和回放指令通过I2C总线或者以太网下发给数据回放系统,信号处理系统和计算机分别通过Aurora总线和以太网与数据回放系统进行数据传输。

本文设计的数据回放系统硬件架构如图2所示,主要由FPGA单元、存储单元、高速缓存单元、以太网单元等组成。项目选择XC7K325T-2FFG900型号的FPGA芯片作为数据回放系统的核心主控单元,其他高速总线、第三代双倍数据速率同步动态随机存储器(DDR3)和固态硬盘(SSD)等器件外挂在FPGA芯片上。对于数据存储过程,外部数据通过Aurora总线传输到数据回放系统,数据进入接收缓存FIFO,然后被搬移至DDR3,最后通过SATA控制器将数据存入SSD中。数据回放过程:SATA控制器从SSD中取数据,将数据缓存到DDR3,再将数据存入发送缓存FIFO中,最后通过Aurora总线回放至信号处理系统或通过以太网回放至本地计算机。

2 数据回放系统设计

2.1 硬件设计

2.1.1 Aurora接口电路设计

Aurora总线是Xilinx公司开发的一种轻量级点对点链路层协议[4],与SRIO和PCle高速串行总线相比,它具有简洁、开销小、链路数量和速率选择灵活等特点。因此,本文采用一路双向Aurora X4总线实现数据回放系统和信号处理系统之间的数据传输。对于系统内部,Aurora总线挂接在FPGA的GTX口上;对于系统外部,VPX连接器很好地支持Aurora高速串行总线。XC7K325T型号的FPGA的GTX接口支持最大速率达12.5 Gbps,VPX连接器传输速率高达6.25 Gbps,单lane的Aurora总线速率配置为5 Gbps,因此系统可以适应高速数据的传输。

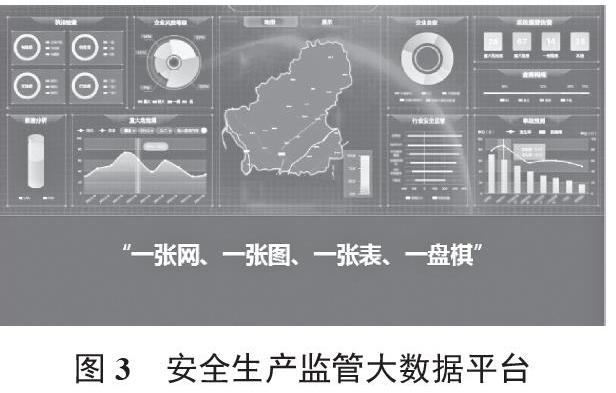

Rocket I/O是一种内嵌在FPGA内部的高速串行收发器,可以支持Aurora,PCIe等多种通信协议[5]。本文采用基于高速串行收发器Rocket I/O的Aurora IP核实现Aurora通信。Aurora传输数据过程如图3所示,其中IP核配置为流模式传输,通信模式为全双工,单通道速率为5 Gb/s,输入系统的参考时钟为125 MHz,用户时钟为250 MHz,发送和接收数据位宽为64 bit。物理层进行了8 B/10 B编码,因此单通道速率可达4 Gbps。

2.1.2 以太网接口电路设计

数据回放系统要求通过计算机实现数据导入、导出以及发送控制命令。采用以太网技术的设备可通过TCP/IP协议进行数据传输,无需进行传输协议转换,使用和维护设备简单[6]。系统采用FPGA外挂千兆以太网的方案实现计算机和数据回放系统之间的通信。千兆以太网采用全双工模式,传输速率可选10 Mbps/100 Mbps/1 000 Mbps,接口电气特性遵循IEEE802.3标准。

通常,网络传输协议包含TCP和UDP两种[7]。为保证数据的高可靠性,系统采用TCP协议传输数据。以太网实现框图如图4所示,其中网络PHY芯片选用MARVELL的88E1111芯片,TCP/IP IP核通过Verilog硬件描述语言实现TCP/IP协议栈。

2.1.3 高速缓存电路设计

为防止接收的数据丢失,采用DDR3对接收的数据进行缓存。本文选用的DDR3芯片型号为MT41K256M16HA-125IT:E。两片DDR3数据位拼接成32位用于数据缓存,拼接的DDR3接到FPGA的高性能I/O口HP上,最高带宽可达6 400 MB/s。

FPGA和DDR3的通信通过Xilinx公司的MIG IP实现。DDR3的MIG IP核包含用户接口模块、存储控制模块和物理层模块[8]。MIG IP核通过物理层接口与DDR3连接,用户接口与FPGA用户逻辑连接,从而实现用户逻辑与DDR3的桥接功能。

2.1.4 存储电路设计

SSD是以FLASH代替传统硬盘盘片作为存储介质,使用SATA系列类型接口的新型存储设备[9]。SSD在访问速度、功耗和可靠性等方面相比传统硬盘有着明显优势,因此文本采用SSD作为数据存储介质。存储单元采用4个标称容量为1 TB的mini-SATA(mSATA)接口的固态硬盘来存储信号处理系统采集的数据。mSATA SSD全部外挂在FPGA的GTX高速接口上,且mSATA SSD与FPGA之间的通信采用标准的SATA3.0通信协议[10]。

本文采用图5所示的基于SATA的存储方案,方案的核心是实现SATA 3.0协议。SATA协议由应用层、传输层、链路层和物理层组成[11]。应用层主要完成命令的设置;传输层将命令层数据封装成FIS帧格式的数据帧;链路层主要完成数据的CRC校验和加解扰处理;物理层负责将上层并行数据转换成串行码流并传输出去。本项目首先通过硬核GTX构建物理层高速串行收发器和OOB信号的检测来实现物理层,然后利用Verilog硬件描述语言实现SATA 3.0协议的链路层和传输层,最后将上述三层协议封装成SATA IP核。项目利用Xilinx的Vivado软件内建一个MicroBlaze软核,将SATA IP核作为MicroBlaze的外设。系统利用Xilinx公司提供的EDK开发环境将SATA IP核挂载到AXI总线上,通过这种方式EDK便可以灵活定制MicroBlaze的外设。

2.2 软件设计

上位PC机软件主要包含显示控制程序和通信管理程序。显示控制程序实现人机交互界面,而通信管理程序则负责完成与数据回放系统之间的TCP/IP协议通信。本文设计的上位PC机软件界面如图6所示。

3 性能评估

在实验室环境下,回放系统设备上电后实测结果如下:

(1)数据回放系统最大存储速度为1 200 MB/s,最大回放速度达1 800 MB/s。根据信号处理系统的A/D采样速率和后续基带信号处理的时钟速率,数据回放系统可以自适应降速存储和回放。

(2)千兆以太网最大导入数据速度约为98 MB/s,最大导出数据速度约为70 MB/s。

(3)如果按照600 MB/s的速率存储数据,数据回放系统可以连续存储2 h以上。

4 结 语

本文设计了一种大容量高速率的数据回放系统。采用mSATA SSD盘作为存储介质,Aurora总线作为数据传输总线,千兆以太网作为数据导入、导出接口。该回放系统体积小、存储容量大、存储和回放速度高、稳定性好。经工程验证,该系统可以较好地满足整机设备对数据回放的要求。

参 考 文 献

[1]黄俊,陈春辉,陈亚骏.高速雷达数据回放系统的实现[J].信息技术,2007(2):91-94.

[2]张宁,王言章.便携式动态心电记录仪及数据回放系统设计[J].长春理工大学学报,2006,29(4):16-18.

[3]梁言,郎兵.超高压可控并联电抗器录波回放系统设计[J].工业仪表与自动化装置,2012(4):53-56.

[4]李维明,陈建军,陈星锜.基于Aurora协议的高速通信技术的研究[J].电子技术应用,2013,39(12):37-40.

[5]陈长林,邱兆坤.Rocket I/O及其在高速数据传输中的应用[J].单片机与嵌入式系统应用,2010(11):25-28.

[6]韦宏,付友涛,孔凡鹏,等.基于FPGA的千兆以太网设计[J].现代电子技术,2012,35(18):56-59.

[7]徐俊. 基于FPGA的嵌入式TCP/IP协议栈的实现[D].上海:华东师范大学,2008.

[8]王红兵,强景,周珍龙.Xilinx MIG IP核的研究及大容量數据缓冲区的实现[J]. 电子产品世界,2016(8):43-46.

[9]杨宇光.SSD技术及应用[J].信息技术与标准化,2010(4):17-20.

[10]吴从中,但德东,刘盛中.SATA3.0协议物理层握手模块设计与验证[J].合肥工业大学学报(自然科学版),2014,37(5):6041-608.

[11]杨亚涛,张松涛,李子臣,等.SATA 3.0物理层设计与FPGA实现[J].计算机工程与应用,2017,53(20):38-42.