使用FPGA设计高可靠SpaceWire路由器*

2019-07-29王梅群李明莉

姚 睿,王梅群,吴 军,胡 杰,李明莉

(1. 南京航空航天大学 自动化学院, 江苏 南京 211106; 2. 北京控制工程研究所, 北京 100190)

空天任务中,主控计算机与外围设备或大容量存储器之间需要进行大量的数据交换,一些重要星上控制数据也需要通过一体化的总线传输,这对设备之间的信息交换和传输提出了较高要求。SpaceWire(SpW)是由欧空局推出的一种面向航天应用的专用通信标准,可提供高速(2~200 Mbit/s)、双向、全双工的数据链路[1]。通过SpW链路连接路由器和节点,可以灵活组建不同规模和拓扑结构的数据传输网络,提升航天电子系统的可扩展性、稳定性和规范化,降低系统组建成本。目前,很多空间任务已将SpW作为通信标准,一些空间仪器中也增加了SpW接口[2-3]。SpW网络中,各节点通过路由器互联,实现数据链路的复用和数据交互。因此,SpW路由器的可靠性在信息传输过程中十分重要。

当前商用SpW路由器通常由专用集成电路实现,如欧空局开发的SpW-10X[4]、Aeroflex Gaisler与IMEC联合开发的GR718[5]。这些抗辐射路由器价格昂贵,且无法根据应用需求进行修改。现场可编程门阵列(Field-Programmable Gate Arrays,FPGAs),特别是静态随机存取存储器(Static Random-Access Memory,SRAM)型FPGA,具有灵活性高、成本低、开发周期短等特点和硬件功能在轨升级的能力,越来越受空间工业的青睐[6]。然而,空天应用中SRAM型FPGA的逻辑电路可能发生各种故障,其数据通路和配置存储器均可能因辐射效应产生单粒子翻转(Single Event Upset,SEU),对系统可靠性造成严重威胁。因此,迫切需要采取措施提高基于FPGA的SpW路由器的可靠性。

目前,SpW路由器的可靠性主要通过协议层的容错措施来保证,且针对专用集成电路实现的路由器IP核多采用硬件描述语言(Hardware Description Language,HDL)开发。然而,文献[7]中对路由器IP核的模拟SEU故障注入实验结果表明,SpW协议不能确保100%的故障检测。因此,研究人员开始研究增强路由器IP故障检测和容错能力的措施,如:文献[8]通过故障注入实验评估路由器IP核中对SEU最敏感的组件,并对关键组件进行寄存器传输级(Register Transfer Leve,RTL)加固,如采用独热状态机、奇偶校验等;文献[9]采用具有错误检测和纠正功能的定制先入先出(First Input First Output,FIFO)存储电路来加固路由器的发送/接收 FIFO单元;文献[10]采用冗余容错技术对SpW收发器进行加固。

上述技术仅对路由器部分组件进行加固,要确保基于FPGA的SpW路由器的可靠性,需要采取系统级保护措施。三模冗余(Triple Modular Redundancy,TMR)是一种应用广泛的经典容错方法,可屏蔽系统中一个模块发生的故障,但其无法纠正SRAM型FPGA的主要故障——配置存储器中SEU故障。虽然该故障可通过配置刷新(即定期刷新配置内存内容)进行纠正[11],但刷新过程将暂时中断系统功能。动态部分刷新(Dynamic Partial Scrubbing,DPS)可仅刷新配置存储器的一部分,而保持其余部分不变。因此,本文将系统级TMR和DPS技术结合,设计基于FPGA的SpW路由器,使其具有错误屏蔽和修复能力;并采用位流重定位技术减少位流文件的存储空间。

此外,DPS虽可修复故障模块的功能,但无法确保修复后该模块中时序电路的状态与其他二个健康模块一致,因而无法使系统恢复至初始容错能力,可能因二次故障导致系统崩溃。实现TMR系统状态同步最简单的方法是重启整个系统。为避免重启系统,可采用回卷恢复[12]或前滚恢复[13]技术。故障发生时,回卷恢复将系统状态恢复至前一个无故障检测点备份的状态,前滚恢复直接将当前无故障冗余模块的状态拷贝至故障模块。虽然前滚恢复的性能优于回卷恢复,但其必须确保状态拷贝过程中无故障模块停止操作,否则后者状态可能发生新的变化。为此,文献[14]将前滚恢复和检测点技术结合,提出了一种改进的前滚恢复方法。在检测点发现故障时,首先缓存系统输入,并将无故障模块的状态拷贝至故障模块;恢复完毕再对缓存的输入进行处理。该方法通过使三个模块停止接收新的输入实现故障模块与健康模块的状态同步,但需对当前输入进行缓存,且状态恢复过程中系统并未真正对外提供服务,造成系统功能延迟。而且,该方法需要系统中所有寄存器的详细信息。为此,文献[15]和文献[16]分别提出了一种基于多扫描链的通用前滚恢复方法及其改进版本。然而,文献[14-16]的状态同步均需与检测点结合,且同步过程会造成系统功能的中断或延迟。因此,本文提出了一种基于工作输入和健康现态的TMR系统状态同步技术(Present-Input and Healthy-State based State Synchronization technique for TMR,PIHS3TMR),该方法无须设置检测点或缓存,且同步过程不会造成系统功能中断或延迟。

1 SpW路由器结构和容错机制设计

1.1 路由器系统的总体结构

如图1所示,路由器的整体结构采用基于SRAM型FPGA的可编程片上系统结构。

图1 系统总体设计结构Fig.1 Overall structure of the system

其中软核处理器MicroBlaze用作修复控制器,缓存用于存储其指令和数据;自定制IP核Router_Core具有TMR结构,用于执行SpW路由器的主要功能;所有位流文件均存储于外部CF卡中。检测到一个模块故障时,通过System ACE控制器从CF卡读取相应的位流文件,并由位流配置引擎HWICAP下载到FPGA的配置存储器中,从而修复故障模块。UART用于实现FPGA与PC之间的通信。

1.2 Router_Core的容错设计与故障修复机制

Router_Core的结构如图2所示,由三个可重构模块(Reconfigurable Module,RM)组成,分别命名为RMA、RMB和RMC;表决与检测模块不仅可对RMA、RMB和RMC的输出(即Ya,Yb和Yc)进行表决得到系统输出Y,且可进行故障检测和定位,并向修复控制器输出相应故障指示信号。

图2 Router_Core的结构图Fig.2 Structure diagram of the Router_Core

图2中,RMA、RMB和RMC是三个执行相同路由功能的独立模块;某模块发生故障时,TMR结构将通过多数表决屏蔽该模块。然而,TMR系统在任何时刻均只能容忍一个模块的故障;当两个模块同时故障时,系统将输出错误结果。为了使系统能从软错误中恢复,本文采用DPS技术。任一模块发生软错误时,表决与检测模块将检测到它并向修复控制器发送故障指示信号;修复控制器将通过System ACE从CF卡读取相应位流文件以修复故障模块。由于本文系统具有自修复能力,下文将其称为可修复TMR(Repairable TMR,RTMR)。

DPS技术虽可恢复系统中组合电路的逻辑,但无法确保修复后模块中时序电路的状态与其他两个模块一致。若不进行状态同步,修复后模块将无法跟上无故障模块的步伐,无法使系统恢复至原始容错能力。因此,本文提出一种称作PIHS3TMR的基于工作输入和健康现态的TMR系统状态同步技术来实现状态同步,并确保系统在状态同步过程中提供正常服务。

另外,为节省位流存储空间,本文采用位流重定位技术,只存储一个功能模块的部分位流文件,在修复过程中进行修改并配置到另外两个模块中,可减少三分之二的位流存储空间,并降低原始位流故障的可能性。

1.3 状态同步技术

1.3.1 时序逻辑电路的模型

时序电路具有记忆功能,其输出由电路当前输入和现态共同决定。大部分时序电路可建模为如图3所示的由组合逻辑电路(Combinational Logic Circuits,CLCs)和触发器(Flip-Flops,FFs)组成的状态机。

图3 时序电路模型Fig.3 Model of the sequential logic circuit

图3中,X=(x0,x1,…,xi)和Z=(z0,z1,…,zj)分别为电路外部输入和输出;D=(d0,d1,…,dk)为触发器的驱动输入;Q=(q0,q1,…,qm)为电路的状态,即触发器的状态;CP=(cp0,cp1,…,cpn)为时钟脉冲。X、Z、D、Q之间的关系可用式(1)~(3)描述。

Zn=F1(Xn,Qn)

(1)

Dn=F2(Xn,Qn)

(2)

Qn+1=F3(Dn,Qn)

(3)

其中:n和n+1分别代表两个相邻的离散时刻tn和tn+1,Zn、Dn和Xn分别表示tn时刻Z、D和X的值;Qn表示tn时刻电路的状态,称作现态;Qn+1表示tn+1时刻电路的状态,称作次态。式(1)为电路输出的表达式,称作输出方程;式(2)为触发器输入的控制方程,称作驱动方程;式(3)为电路次态与其现态及电路当前工作输入的关系,称作状态方程或次态方程。显然,Z和D由组合逻辑实现,故tn时刻的输出仅取决于该时刻的输入;而Q由触发器实现,故其tn+1时刻的输出Qn+1由当前输入Dn和现态Qn共同确定。

使用DPS技术虽可恢复TMR系统中故障模块的电路,但不能保证修复后模块的现态与无故障模块一致。因此,必须进行状态同步。

1.3.2 状态同步技术PIHS3TMR

为了确保无故障模块正常工作并在状态同步过程中提供正常服务,提出了如图4所示的实时自修复TMR系统状态同步方法PIHS3TMR。

图4 状态同步技术PIHS3TMRFig.4 PIHS3TMR,state synchronization technique

图4中,将TMR系统中每个模块(记作模块y)的状态机进行改造,在系统工作输入X和时钟输入的基础上,增加了健康现态输入Qh(q0h~qmh)和状态同步控制信号SCy以及二选一多路复用器;状态输入Q(q0~qm)可由SCy控制在本模块现态Qy(q0y~qmy)和健康模块的现态Qh(q0h~qmh)之间选择,如式(4)所示。

(4)

正常工作过程中SCy为0,选择本模块现态Qy作为CLC的输入,所以模块y根据自己的状态机独立工作。状态同步过程中SCy为1,选择健康现态Qh作为CLC的输入,可根据系统工作输入和健康现态立即构造出模块y的次态,确保模块y的状态与其他模块同步。此外,在整个电路恢复和状态同步过程中,无故障模块一直正常工作,为外界提供服务,无须中断系统的运行。

图4中健康现态可由三个模块的状态表决得到,亦可直接使用任一无故障模块的现态。由于为每个FF的输出插入表决器将加大面积开销和关键路径延迟,本文直接采用相邻模块的现态作为健康现态,如式(5)~(7)所示。

Qh1=Q2

(5)

Qh2=Q3

(6)

Qh3=Q1

(7)

其中,Qhi(i=1,2,3)代表模块i的健康现态。

1.4 位流重定位技术

执行DPS时,传统设计流程为某一部分重构区域(Partially Reconfigurable Region,PRR)产生的部分重构位流(Partially Reconfiguration Bitstream,PRB)不能重定位到其他PRR。如图5所示,PRR1的位流adder_1无法配置到PRR2和PRR3中[17]。

图5 DPS系统的位流配置Fig.5 Bitstream configuration of DPS system

为实现位流重定位,应遵循以下两个步骤。

步骤1:设计时确保PRR完全相同,要求如下。

1)可重构资源的数量相同;

2)可重构资源的相对布局一致;

3)代理逻辑的相对位置一致;

4)代理逻辑和静态区域之间互联的相对路由路径一致;

5)静态区域的信号布线不能穿过动态区域。

步骤2:重定位之前必须修改配置位流。关键是修改帧地址和循环冗余校验(Cyclic Redundancy Check,CRC)值。帧地址为16进制命令字(30002001)后第一个字,表示PRR的起始地址。CRC值为16进制命令字(30000001)后第一个字,用于检查位流的有效性。创建重定位位流时,必须先用目标PRR的帧地址替换原始PRR的帧地址;然后根据式(8)重新计算CRC值并替换原CRC值。

x32+x28+x27+x26+x25+x23+x22+x20+x19+

x18+x14+x13+x11+x10+x9+x8+x6+1

(8)

2 实验结果和讨论

使用Xilinx Virtex-5 FPGA开发套件ML507,以具有4个端口的SpW路由器为例来验证所提出的系统结构和自修复机制。

2.1 SpW路由器的典型结构

如图6所示,SpW路由器通常包含若干SpW端口和一个交换矩阵。前者为所有SpW节点和路由器提供接口,后者用于实现各端口间数据的交换。

图6 SpW路由器的典型结构Fig.6 General block diagram of the SpW router

端口通常由状态机、发送器、接收器、发送FIFO和接收FIFO组成。其中状态机控制端口的所有操作;接收器对链路数据进行解码并将其传输至接收FIFO,再由接收FIFO传输至主机接口;发送FIFO将来自主机接口的用户数据传输至发送器,再由发送器编码后传输至链路。

交换矩阵包含地址识别和矩阵路由两部分。前者解析包头所包含的目的地址,后者调控数据包的传输路径。

2.2 状态同步技术的结果

以图7所示SpW端口的状态机为例,验证所提出状态同步技术的有效性。

图7 链路状态转换图Fig.7 State transition diagram of the state machine

TMR结构的SpW端口上电时状态机处于“错误复位”状态,发送端与接收端的链路接口将自动连接,并最终处于“运行”状态。某一模块发生错误时,将对其进行DPS纠正错误,之后其状态机进入“错误复位”状态,但此时其他模块仍处于“运行”状态并正常运行。三个模块共享链路并与同一个节点进行通信,因此没有握手信号使该模块与节点再次自动建立连接。若不进行状态同步,该模块将一直处于“错误复位”状态,无法转换为“运行”状态。PIHS3TMR技术可使修复后模块根据工作输入和健康现态进行状态转换,实现与无故障模块的状态同步。采用HDL语言设计该状态机的PIHS3TMR系统,在Xilinx ISE软件中的仿真结果如图8所示。

图8中,clk为时钟输入,rst、sc和state分别为复位信号、状态同步控制信号和状态输出信号;active表示建立链路连接的“运行”状态。所有以“sanmo”为前缀的信号表示健康状态,以“yimo”为前缀的信号表示修复模块(记为RMy)的状态;矢量信号的显示格式为“n′hxxx”,其中“n”是原始矢量的位数,“hxxx”是其十六进制值。由图8可见,在第1~3个时钟周期,三个模块均处于“运行”状态并正常工作,因此其状态相同,均为“3′h5”。在第4个时钟周期,RMy的复位信号有效(模拟修复后RMy的初始状态),其状态(yimo/statem/state)为“3′h0”(错误复位),与其他模块不一致。由于采用了状态同步技术,第5个时钟周期,RMy的sc有效,故其状态立即根据健康现态(sanmo/statem/state)从“3′h0”跳到“3′h5”,与其他模块一致;且active再次有效。第6~7个时钟周期,三个模块均正常工作。可见PIHS3TMR的理想状态同步时间仅为1个时钟周期。尤为重要的是,状态机在整个工作过程中均提供正常服务,不会中断系统功能。

2.3 SpW路由器的实现结果

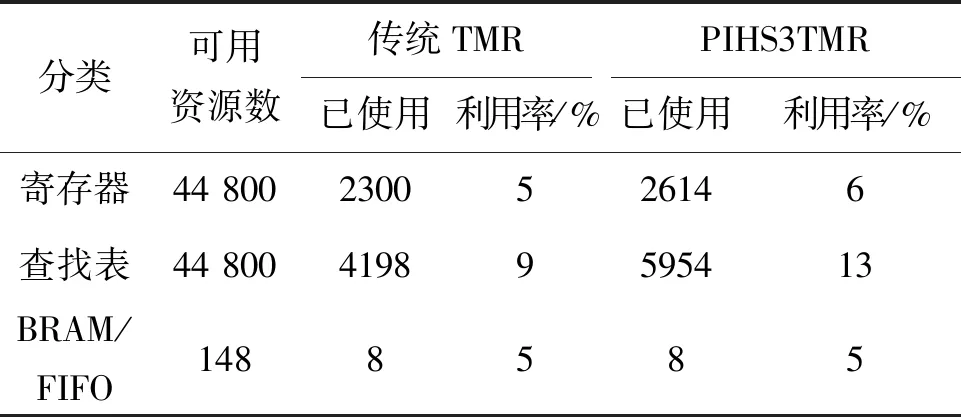

使用VHDL语言分别设计PIHS3TMR结构和传统TMR结构的四端口SpW路由器,二者实现结果比较见表1。

图8 状态机的PIHS3TMR状态同步仿真结果Fig.8 Simulation results of the PIHS3TMR design for the state machine

由表1可见,与传统TMR相比,PIHS3TMR所用BRAM/FIFO资源数量相同;所用寄存器和查找表资源的数量分别增加了约13.7%和41.8%,但所用资源占可用资源总量的比例依然很少(分别为6%和13%)。所用资源数量增加的主要原因在于PIHS3TMR结构的状态同步需要增加多路选择器。由于FPGA有大量的资源冗余,所以PIHS3TMR的资源代价是可接受的。

表1 SpW路由器的实现结果比较

2.4 位流重定位技术的结果

在ML507开发板上实现了所提SpW路由器的系统结构,并分别采用位流重定位技术(本文方法)和非位流重定位技术(传统方法)进行DPS,所需部分位流文件数量和存储器空间大小如表2所示。由表2可见,传统方法所需部分位流文件数量是本文方法的3倍。由于每个部分位流文件的大小为133 Kbit,因此本文方法可以节省266 Kbit,即大约66.7%的存储空间;同时也降低了原始位流本身故障的可能性。

表2 位流重定位和非位流重定位技术的比较

目前仅考虑SEU之类软故障的纠正,每个模块仅需一个位流文件;未来考虑硬故障修复时,每个模块均需多个位流文件以应对FPGA不同位置的硬故障,位流重定位技术的优势将更明显。

DPS所需时间可用式(9)描述,其中Tcf为读取位流文件并将其存储至System ACE缓冲区所需时间,Ticap为利用位流文件刷新配置存储器所需时间,Tadd为修改帧地址和CRC的额外时间开销。

Trec=Tcf+Ticap+Tadd

(9)

Tcf的值可由式(10)[18]计算,其中L为以位(bit)为单位的位流文件大小,0.634 18为System ACE控制器以MByte/s为单位的平均带宽值,Tcf的单位为ms。

Tcf=L×10-3/0.634 18

(10)

Ticap的值可由式(11)计算,其中L′是以字节(Byte)为单位的位流文件大小,CLK是以Hz为单位的内部配置访问端口(Internal Configuration Access Port, ICAP)时钟频率,ICAP宽度是以Byte为单位的ICAP宽度。

Ticap=L′/(CLK×ICAP宽度)

(11)

本文系统的时钟频率为100 MHz(周期为10 ns),位流文件大小为133 Kbit,因此据式(10)和式(11)可算出Tcf和Ticap的值分别约为209.72 ms和42.56 μs。由于修改帧地址和CRC所需时间仅为几十纳秒(几个时钟周期),故与Tcf和Ticap相比,Tadd可忽略。因此,DPS时间约为209.76 ms。

2.5 可靠性和可用性分析

2.5.1 系统可靠性模型

MicroBlaze和表决与检测模块未来可进一步采取措施加固,故分析系统可靠性时,暂时忽略其故障影响,仅考虑Router_Core核的可靠性。

假设图2所示RTMR结构的Router_Core核有三种状态——正常状态(三个模块均正常工作),修复状态(存在故障模块并正在修复)和故障状态(存在两个或更多故障模块),并假定在相当短的时间Δt内,两个或多个模块同时发生状态转换的概率是Δt的高阶无穷小,可以忽略,则该系统的马尔可夫状态空间模型可用图9表示。

图9 自修复TMR系统状态空间图Fig.9 Self-repair TMR system state space diagram

图9中,0表示正常状态,1表示修复状态,2表示失效状态;λ为每个模块的故障率;μ为修复率;Δt为时间间隔。则RTMR系统的可靠度如式(12)[6]所示。

式中,λ为单个模块的故障率,即每小时失效次数,k=μ/λ;μ为修复率,即每小时成功修复次数。传统TMR系统的可靠度[6]为:

RTMR(t)=-2e-3λt+3e-2λt

(13)

2.5.2 系统可靠性分析

系统的平均修复时间(Mean-Time-To-Repair,MTTR)包括DPS时间和状态同步时间。由于PIHS3TMR的状态同步仅需1个时钟周期,故其MTTR约等于DPS时间,即约为209.76 ms,可得修复率μ=3600/MTTR≈1.72×104次/h。假设Virtex-5器件工作于地球同步轨道(Geostationary Earth Orbit,GEO)(36 000 km),则典型日SEU故障率为3.8×10-10次/(bit·d)[19],因此SpW路由器每个模块的SEU故障率为λ=3.8×10-10×133×103×24≈1.21×10-3次/h;进而可得k=μ/λ≈1.42×107。因此,由式(12)和式(13)可得RTMR结构(本文结构)和传统TMR结构的SpW路由器的可靠度,如图10所示(这里仅考虑软故障)。

(a) 0~2500 h的可靠度对比(a) Reliability from 0 h to 2500 h

(b) 0~100 a的可靠度对比(b) Reliability from 0 a to 100 a图10 TMR和RTMR结构SpW路由器可靠度对比Fig.10 Reliability comparison of the SpW routers with TMR structure and RTMR structure

由图10可见,随着持续工作时间的增加,传统TMR系统的可靠度呈指数规律递减;持续工作2300 h后,其可靠度快速递减至0。而本文RTMR系统的可靠度近似保持不变;若仅考虑软故障,甚至持续工作100 a后,其可靠度仍可达到约0.999 6。这种高可靠度特别适合要求高可靠性和长寿命的空间应用。

2.5.3 系统可用性分析

可用度可定义[7]为:

(14)

其中,平均故障间隔时间(Mean-Time-To-Failure,MTTF)定义为SpW一个模块持续无故障操作的时间,平均检测时间(Mean-Time-To-Detect,MTTD)定义为配置存储器发生错误到该错误被检测到的时间间隔。无错误发生时,MTTD和MTTR均为0,故Av为1,意味着FPGA器件是完全可用的。配置存储器中发生SEU时,若设计对其敏感,将会发生错误,则表决与检测模块将会立即检测到该错误,因此MTTD可以忽略。所以,对本文系统,式(14)可以简化为

(15)

本文系统的MTTR约为209.76 ms,即5.827×10-5h,MTTF=1/λ=1/(1.213×10-3) h,因此由式(15)可得其可用度约为0.999 999 9,非常接近于1。而对于传统TMR结构,当两个以上模块发生故障时,MTTR为无穷大,因此其可用度为0。

3 结论

首次将系统级三模冗余、动态部分刷新、位流重定位技术,以及基于工作输入与健康现态的实时状态同步方法PIHS3TMR结合,提出了一种基于SRAM型FPGA的高可靠SpaceWire路由器设计方法。PIHS3TMR技术的引入保证了路由器工作过程中始终提供正常服务,不会引起系统功能中断或延迟;且状态同步时间仅为1个时钟周期,有助于减少平均修复时间。位流重定位技术的采用将所需存储空间减少三分之二,同时也降低了原始位流本身故障的可能性;当每个模块需要多个位流以应对不同位置硬故障时,其优势更为明显。

经三模表决后路由器数据交换更可靠,且路由器自身硬件可自修复,可靠性和可用性高。Virtex-5器件工作于GEO时(典型日SEU故障率为3.8×10-10次/(bit·d)),若仅考虑软故障,持续工作100 a后,其可靠度仍可达到约0.999 6,且其可用度约为0.999 999 9,非常接近于1。

所提系统结构和设计方法是通用的,可用于设计其他需要高可靠性、好实时性、小批量和易于升级的系统。目前仅对SpW路由器核心功能区进行了TMR加固,未来将进一步研究修复控制器和表决与检测模块的加固。