基于多仿真器的牵引传动系统实时仿真研究

2019-07-12武明康郭希铮唐一果

武明康, 郭希铮, 李 诚, 唐一果

(北京交通大学 电气工程学院, 北京 100044)

高速列车牵引传动系统包括牵引传动系统和辅助变流系统,前者通过牵引变流器控制牵引电机为列车提供牵引力或者制动力,后者为列车辅助负载(如列车制动系统、冷却系统、照明等)提供电源。牵引控制单元(Traction Control Unit, TCU)和辅助控制单元(Auxiliary Control Unit, ACU)是高速列车牵引传动系统的核心控制部件。在开发其控制策略与算法的过程中,硬件在回路(Hardware In the Loop, HIL)实时仿真通过实时仿真器模拟被控对象(牵引变流器、辅助变流器等),与真实的控制器构成闭环测试系统,以无试验风险、高研发效率、低研发费用、能够测试极限工况等优势被应用于大功率牵引传动系统的研发过程[1-5]。

早期的实时仿真器大多用中央处理器(CPU)执行模型求解任务,仿真步长通常为40~100 μs[6-7]。但是随着电力电子器件开关频率增加,“抖动问题”将对仿真结果产生较大影响[8]。基于CPU的实时仿真器难以进一步降低仿真步长,无法从根本上解决该问题[9]。基于FPGA(Field Programmable Gate Array)实时仿真器利用FPGA并行计算的优势,使仿真步长可以达到1 μs甚至几十纳秒,从根本上解决电力电子系统实时仿真的“抖动问题”,提高仿真精度[10-12]。但是随着仿真对象的规模日益庞大,单个FPGA实时仿真器难以解决有限的硬件资源与仿真步长之间的矛盾问题。多实时仿真器联合仿真成为复杂电力电子系统实时仿真的趋势。

目前国内牵引传动系统的单实时仿真器应用案例较多,但还没有关于多仿真器、多步长的相关研究。文献[2]以牵引逆变器-异步电机单元为研究对象,建立基于dSPACE(德国dSPACE公司开发的实时仿真器)系统的HIL模型,模型较为简单,仅能测试牵引电机的工况,无法测试整车牵引系统的各个部件相互作用和影响。文献[5]以交直交牵引系统为研究对象,建立基于RT-LAB实时仿真器HIL模型,不涉及辅助变流器部分的建模与实现,也没有针对多仿真器系统的相关论述。文献[13]实现三电平牵引逆变器-牵引电机单元的HIL实时仿真,使用两套dSPACE仿真器分别建立网侧和电机侧模型,实现仿真步长60 μs的基于CPU的实时仿真。但并没有关于多仿真器系统如何构成、CPU+FPGA架构下多步长仿真如何实现的论述。

牵引变流器和辅助变流器含有大量电力电子开关器件,对其准确的建模是工作的难点。在电力电子开关器件数量较少时,把它们等效为理想开关是一种常见的做法。当开关器件较多,这种做法在模型求解时需要实时计算逆矩阵,导致计算量过大,不适合FPGA求解[14-16]。考虑到开关器件的寄生参数特性,Hui等[17]学者提出ADC(Associate Discrete Circuit)建模,不需要实时求解逆矩阵,在实时仿真系统中具有较好的应用前景[18-21]。

本文以高速列车牵引传动系统为研究对象,使用ADC建模法建立牵引变流器和辅助变流器的数学模型;通过合理地分割系统模型,降低系统矩阵维数;搭建基于Gigalink通信网络的dSPACE多仿真器实时仿真系统,详细阐述多仿真器、多步长下基于dSPACE的CPU+FPGA硬件在回路实时仿真系统的实现过程,完成整车级的HIL实时仿真,测试牵引传动系统各种工况下的控制性能,缩短TCU/ACU的控制算法开发周期。

1 基于多仿真器的牵引传动系统构成

1.1 高速列车牵引传动系统拓扑结构

本文研究的高速列车牵引传动系统结构[22]见图1,受电弓从单相交流电网(25 kV AC)取电,经过工频牵引变压器降压之后(1.77 kV AC),由双重四象限PWM整流器整流,经过中间直流环节后接两台牵引逆变器-牵引电机单元。辅助变流器以四象限整流器的高压直流输出(3.6 kV DC)为输入,通过两个串联的半桥零电流(HB-ZCS) DC-DC降压电路降压(600 V DC),后接辅助逆变器产生三相交流电压(380 V AC),为辅助系统负载供电。

图1 牵引传动系统功率电路

1.2 模型的划分

硬件在回路仿真系统包括牵引、辅助供电系统,分别由实车的TCU和ACU进行控制。同时为了模拟真实环境,还需要设置TCU/ACU的上电启动逻辑和弓网侧电压等模型。因此,整个系统的模型十分庞大,无法由单处理器实现多仿真步长、大量数据接口。

因此,整体的模型需要被合理地划分,使各个子模型分布在相应的CPU中并行执行,充分利用硬件资源以达到更高的计算性能。为了实现更高效的多处理器实时仿真,模型的划分可以参考以下准则:

(1) 尽可能减少处理器之间的通信。

(2) 具有强耦合的部分不宜拆分。

(3) 尽可能把计算任务平均分配到各个处理器。

(4) 处理器之间的通信方式可以选择异步回转缓存协议(Unsynchronized Swinging Buffer Protocol)以进一步降低可能的等待时间。

综合考虑系统各个部分的固有属性和功能设定,以及相应的控制器接口特点,将整个系统模型划分为三个子系统模型:牵引变流器模型、辅助变流器模型、弓网系统和上电启动逻辑系统模型,见图2。三个子系统分别由三个CPU核心完成任务,子系统之间的模拟信号传递仅为牵引变压器二次侧电压电流(er1,er2,ir1,ir2)信号,辅助变流器高压直流侧电压电流(udc2,idc2)信号。

图2 系统模型划分

1.3 多仿真器系统的构成

dSPACE实时仿真器具有高速的计算性能、丰富的I/O接口、模块化的硬件构成等特点,多仿真器系统的构建可以在单仿真器系统的基础上快速地完成。DS1006板卡是单仿真器系统的核心板卡和拓扑网络的关键节点,一方面通过工业标准结构(Industry Standard Architecture, ISA)总线与工作站连接,在工作站上完成模型下载和实时监控;另一方面通过高速外设总线(Peripheral High Speed, PHS)连接各种不同功能的I/O板卡,32位I/O总线最大传输速率20 MB/s,根据本文HIL仿真需求配置相应板卡见表1。

表1 dSPACE实时仿真系统板卡

仿真器Ⅰ和仿真器Ⅱ组成的多仿真器系统见图3。仿真器Ⅰ以DS1006板卡为核心,通过PHS总线挂载4块I/O板卡,模型求解的任务主要由DS1006和DS5203板卡完成,4块I/O板卡与TCU/ACU通过信号调理箱(图中未画出)连接,同时也可以在示波器上观测相应的电平信号,与工作站监测的信号互为对照。仿真器Ⅱ的构建与仿真器Ⅰ类似。

图3 dSPACE多仿真器系统硬件拓扑连方式

单仿真器系统的DS1006板卡搭载一颗AMD四核CPU,CPU的每个核心都可以独立运行仿真任务,核心之间通过内部Gigalink连接,采用局部存储器实现通信,完成多核并行仿真任务。

多个单仿真器系统通过DS1006板卡的DS911 Gigalink 模块与外部通信,由光纤线缆作为通信媒介。这种连接为外部Gigalink连接。

所有的板卡和相应的连接方式,都可以在工作站注册后识别,在Matlab/Simulink中方便地调用所有板卡的对应模块。例如处理器核心之间的通信在软件层面由dSPACE公司提供的IPC (Interprocessor Communication,IPC)模块设置(包含在Simulink的RTI库中),为CPU之间的通信设置提供友好的人机窗口。

1.4 多步长仿真系统

高速列车牵引系统是电气和机械系统的综合体,不同部件的时间常数差别很大。例如牵引变压器模型、电机的运动方程模型、继电器逻辑模型等,其时间常数在毫秒级,微秒级的仿真步长即可满足精度要求,完全可以交由CPU运行仿真。综合考虑计算任务复杂程度、多仿真器之间通信延时等因素,设置仿真步长h1为60 μs。而部分电力电子变流器模型的时间常数在微秒级,由CPU执行仿真无法满足精度要求,因此由FPGA执行小步长的仿真任务更加合适,设置仿真步长h2为10 ns,见图4。

图4 多步长仿真系统

在仿真器Ⅰ中,DS1006负责牵引电机的运动方程模型和工频变压器模型,DS5203负责四象限整流器、牵引逆变器和异步电机电磁方程模型;在仿真器Ⅱ中,DS1006负责辅助风机的运动方程和其他辅助系统负载模型,DS5203负责半桥降压DC-DC斩波器模型和辅助逆变器模型。DS1006和DS5203之间的模型通过dSPACE提供的实时仿真接口(Real Time Interface, RTI)完成软件层面的连接。整个实时仿真模型建立在多仿真器、多仿真步长的模式下,依据各部件的固有特点充分利用硬件资源,达到最优的仿真性能。

2 牵引传动系统实时仿真数学模型建模

牵引传动系统由变压器、电机、电力电子变流器等不同类型的电气设备组成,具有非线性、强耦合、高频化等特点,建模时需要以控制器算法开发、调试为导向,合理地建立相应的数学模型,尽可能真实地还原受控对象的电磁特性。限于篇幅,本文仅以辅助变流器为例,介绍时域下的数学模型。其他部分也可以通过同样的方法建模,不再赘述。

考虑到电力电子开关器件的寄生参数,开关在导通时等效为一个小电感L,在关断时等效为一个小电容C与一个阻尼电阻R的串联支路。必须说明的是,L/C等效后的开关模型可以选择不同的离散化方法离散该连续系统,所对应的等效导纳和注入电流源公式也不同。综合考虑,后向欧拉法的数值稳定性、收敛性、计算量等方面比前向欧拉法、梯形法等更高阶的数值算法更优,在小步长的条件下高阶算法的精度优势不明显[23],因此选择后向欧拉法离散化L/C等效开关模型,见图5。图5中,Vs为开关电压;js为等效电流源;is为开关电流,Gs为等效导纳;h为仿真步长;n为迭代计算步数。

图5 等效开关模型

为保证系统矩阵H为常数矩阵,则需要保证不同开关状态下等效导纳相等,需满足

Gs=(R+h/C)-1=h/L

(1)

通过MNA(Modified Nodal Approach)获得系统矩阵为

Hxn+1=bn+1

(2)

式中:H是常数系统矩阵;x是节点电压和支路电流向量;b是电源输入向量,包括电压源和电流源。

电流源js包含在向量b中作为系统的输入,其数值大小与该开关的导通状态有关

(3)

辅助变流器作为前级四象限整流器的负载,通过半桥逆变器、中频变压器(4 kHz)、二极管整流桥、软开关谐振支路、LC滤波器实现降压。实车的辅助变流器为了降低开关器件的应力,采用输入串联、输出串联的方式,由两组DC-DC电路组成,如图1辅助变流器部分所示。在建模阶段,可拆分为单组DC-DC电路模型,见图6。经过DC-DC降压之后,三相辅助逆变器与三相LC滤波器构成三相四线制供电方式,为辅助系统负载提供电源。

图6中辅助变流器共有13个开关,再加上电感、电容等储能器件,导致系统矩阵维数达到23。若再考虑辅助系统负载模型,矩阵维数将会进一步增加,不利于模型在FPGA中实现。因此,本文采用输入-输出方法将辅助变流器模型分为5个子系统,见图7,每级子系统之间互为输入-输出关系,子系统1为半桥逆变模型,其输出电压为后级子系统2的输入电压;子系统2的输入电流为前级子系统1的输出电流。前级向后级传递电压信号,后级向前级反馈电流信号。

中频变压器以理想变压器为模型,m为变比,一次侧和二次侧电压电流关系为

(4)

式中:u2sec为变压器副边电压;u1pri为变压器原边电压;i1pri为变压器原边电流;i2sec为变压器副边电流。upq、ipq、jpq(p=1,2,…,q=1,2,…,)均表示相应节点电压和支路电流变量。

再用ADC方法分别建立各个子系统的离散化电路,见图8,可以通过MNA方法得出4个子系统的数学模型见式(5)~式(8)。

图6 辅助变流器电路拓扑

图7 辅助变流器子系统划分原理

图8 辅助变流器ADC开关等效模型

以Matlab/Simulink的SimpowerSystem(SPS)仿真作为对照,与离线仿真的结果对比。仿真参数见表2。

表2 辅助变流器参数

输出电压见图9(a),占空比固定为0.274。在t=0 s到t=0.007 s的暂态过程中,相对误差较大,在电路到达稳态后,输出电压的相对误差小于0.01。在电路暂态过程中,电压电流变化剧烈,开关等效L/C没有达到稳态就进入下一个暂态,导致开关电压电流振荡较大,引起误差较大。在电路稳态时,等效L/C经过短暂的暂态过程后很快达到稳态,即L等效为短路,C等效为开路,使仿真误差很小,此时的误差主要来源于定点运算的截断误差和量化误差。图9(b)所示变压器的二次侧电流在S+或者S-开通时产生震荡,在稳态时误差很小,印证上述分析。通过选取合适的参数Gs,电流就会很快到达稳态,本文Gs选为0.1。

(5)

(6)

(7)

(8)

式(5)~式(8)中所有G为图6、图7中相应电感、电容、电阻的等效导纳;u为元件的两端电压;r为电阻;Udc为电源电压。

图9 输出电压vout、二次侧电流i2sec和相对误差

3 数学模型的实现

文中的数学模型可以在MATLAB/Simulink中进行浮点运算,但浮点数据的计算耗费资源较多,尤其在FPGA中执行计算任务时,有限的片上资源是必须考虑的问题。在计算量较大时,通常需要在片上资源、数据精度、计算时间等方面做出平衡。

定点计算在数值精度方面略低于浮点计算,但可以显著地加快任务执行速度,并且降低硬件资源的消耗。只要选择合适的数据精度,定点计算也能得到理想的计算结果。因此本文选择定点计算。数据精度的选择分为以下3步:

Step1定义基准电压Vbase和基准电流Ibase,使系统参数标幺化。

Step2根据所有系统参数和系统变量的数据位数,选择合适的整数位和小数位。

Step3在FPGA中实现模型。

本文选择定点数据精度为40Q35,即35位小数精度,4位整数精度,1位符号位。两块基于Xilinx Virtex-5 FPGA的DS5203板卡分别实现牵引系统和辅助变流系统的数值解算工作。

基于FPGA的数字信号处理系统具有并行计算的优势,在满足FPGA时序约束的条件下,计算任务量的增加对应着所需FPGA内部资源的增加,但每一步计算所需时间基本不会变化,经过算法的优化,可以尽可能地提高计算的并行度,充分利用已有的FPGA片上资源,如片上RAM单元、DSP单元,使系统的整体性能达到最优。数学模型在FPGA和CPU中的实现,见图10。每个子系统向后传递电压信号,向前反馈电流信号。

图10 模型的实现

4 硬件在回路仿真实验结果

高速列车牵引传动系统硬件在回路仿真实验平台由信号调理板、TCU/ACU和dSPACE三大部分组成。信号调理板作为TCU/ACU和dSPACE的通信接口,实现控制器(TCU/ACU)和仿真器(dSPACE)的实时数据交换。dSPACE仿真器通过ISA总线与工作站通信,开发人员在工作站通过相应的配套软件完成模型搭建、编译、下载、管理、调试、监控等一系列工作。三大部分组成了高度集成化和自动化的高速列车牵引传动系统硬件在回路仿真平台,可以在改平台上进行各种工况测试和试验。牵引传动系统参数见表3。

表3 牵引传动系统功率电路参数

图11 四象限整流器波形

四象限整流器的空载启动波形和半载突增至满载波形见图11。整流器采用软启动方式,减小启动时的冲击电流,抑制电压超调量;由半载突增至满载时,电压跌落至3 300 V,调节时间小于40 ms。

图12 牵引传动系统HIL实验波形

图13 辅助变流器HIL实验波形

牵引电机定子频率在10、42 Hz时闭环实时仿真波形见图12,分别为电机A相电压、电流波形,完成牵引电机的调速测试。

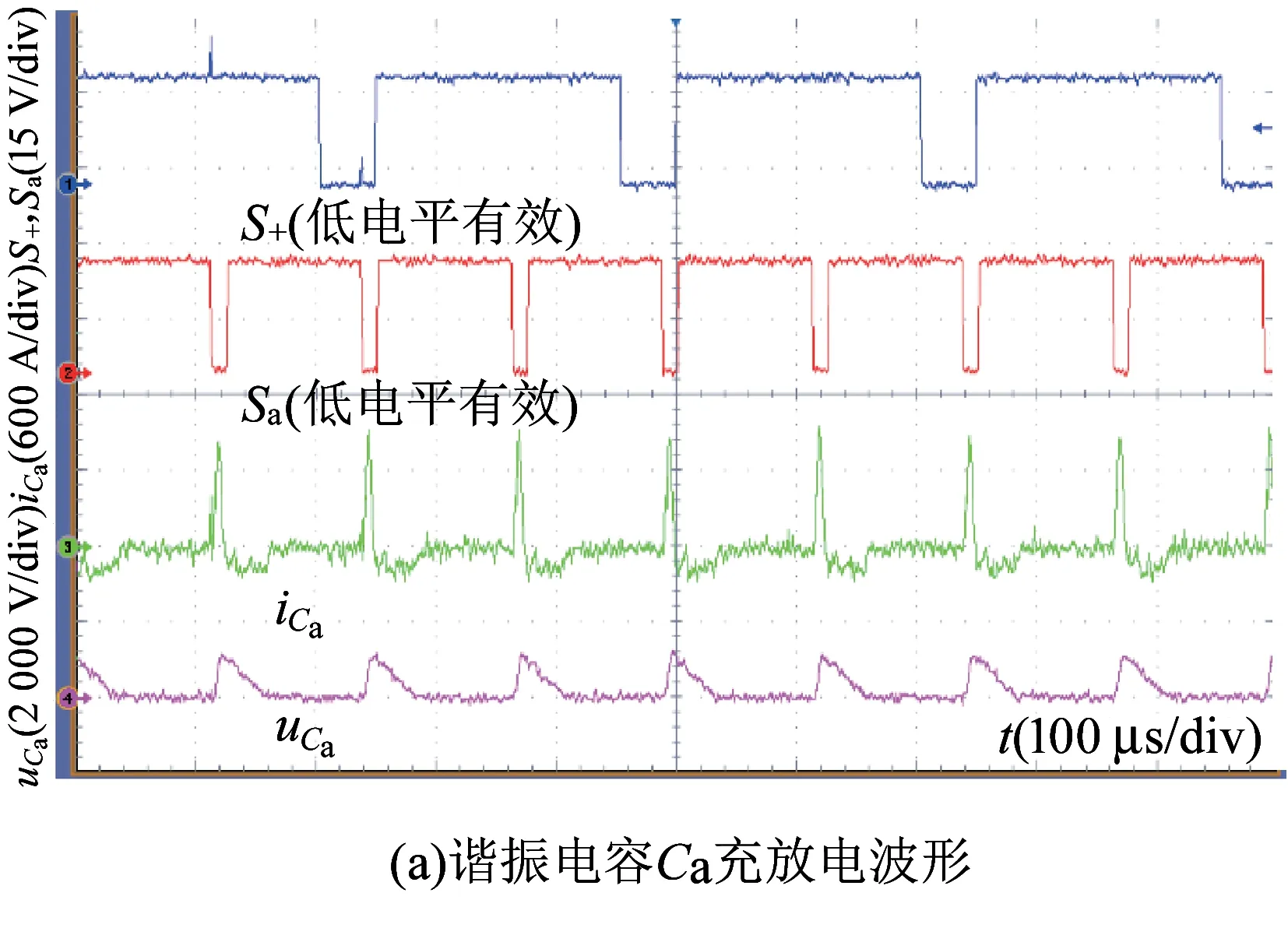

辅助变流器谐振电容Ca充放电波形见图13(a)。电容Ca在辅助开关Sa开通时刻充电,关断之后放电,与理论分析结果一致。辅助变流器投切负载的输出电压电流波形见图13(b),经过ACU闭环控制,使辅助变流器的输出电压和电流具有较好的稳态性能和动态响应,达到理想的实验效果。

5 结论

(1) 对于复杂被控对象的硬件在回路实时仿真,可以采用多仿真器协同、多步长配合的方式实现,达到对控制器在各种工况条件下进行系统级性能测试的试验目的。

(2) 在dSPACE实时仿真器提供的硬件、软件资源基础上,开发人员可以根据需要对被控系统的模型进行合理的分割,根据系统各部分的时间常数选择合适的仿真步长,再配置仿真器各子系统的通信接口以及与控制器的接口,就能够实现复杂系统的多仿真器、多仿真步长的硬件在回路实时仿真。这种测试方法不受现场试验条件的制约,可以提高测试控制器的质量和效率。

(3) ADC建模法可以获得定常参数的系统矩阵,在通过FPGA实现纳秒级实时仿真时可以大大节省FPGA的片上资源,同时也能保证必需的仿真精度,为实现系统级实时仿真提供有利条件。