基于HfNx∶Zn薄膜的负微分阻变存储器

2019-07-01王中强凡井波严梓洋李壮壮

王中强,张 雪,齐 猛,凡井波,严梓洋,李壮壮

(东北师范大学 a.物理学院;b.物理学国家级实验教学示范中心(东北师范大学),吉林 长春 130024)

随着大数据时代的来临,信息存储量呈现爆发式增长,对信息存储器件的存储密度以及擦写速度等性能提出了更高要求[1-2]. 对目前通用的Flash存储器而言,其器件可靠性将会随着尺寸进一步缩小而变差[3]. 因此,近年来涌现出多种新型的非易失性存储技术用于取代Flash型存储器,包括铁电存储器、磁存储器、相变存储器、阻变存储器等[2,4-7]. 其中,阻变式存储器因具有存储密度高、擦写速度快以及低功耗等优势,有潜力成为新一代存储器[1-2]. 多家国际著名电子公司都在此领域开展了研发工作,如三星、惠普、东芝、索尼、闪迪、IBM等. 阻变层材料包括很多种类,如金属氧化物、硫化物、氮化物以及有机材料等均能观察到阻变现象[7-11]. 其中,氮化物由于具有导热率高、绝缘性好以及高电容率等特点,引起了广泛的关注[12-14]. Hong和Kim等基于SiN/AlN材料,实现了优异的阻变性能,例如快速的转换时间(<10 ns)、高循环耐受性(108次)及较低运行电流(<10 μA))[12,14]. 然而,目前氮化物体系的阻变机制尚未明确. 同时,氮化物基阻变存储器运行过程中经常存在着很大的随机性,从而引起较高的阻变参量波动性,如高低阻态和转变电压. 因此,高可靠性氮化物阻变存储器件的构筑同样是非常重要的. 本文利用原子层沉积方法,制备了基于HfNx∶Zn薄膜的阻变式存储器件,探究了器件的阻变行为,分析了出现负微分电阻现象的原因及其阻变机制. 本文工作是在近代物理实验教学过程中结合实际现象,培养本科生发现问题和解决问题能力的一次课程尝试.

1 实 验

实验器件制作方法如下:

1)利用原子层沉积方法将HfN与ZnN薄膜交替沉积在Pt/Ti/SiO2/Si衬底上. Pt/Ti/SiO2/Si衬底提供Pt金属底电极,是阻变存储器制备过程中常用的衬底[9,15-16]. Pt金属层(100 nm)作为器件的底电极,SiO2/Si(200 nm/500 μm)硬质衬底与CMOS工艺相兼容, 而引入Ti层(30 nm)能够增加Pt与SiO2/Si硬质衬底两者间的粘附性[15-16]. 其中Pt金属层的横向电阻约为20 Ω,经计算其电阻率约为4.0×10-7Ω·m,接近于常用金属丝的电阻率(2.2×10-7Ω·m),具有很好的导电性. 在薄膜交替生长的周期中所采用的载气气体均为N2,吹扫时间均为30 s. 铪源(四二甲氨基铪)和锌源(二乙基锌)的剂量控制时间为0.2 s,等离子体的反应时间为20 s. 薄膜沉积过程循环了100个生长周期,其沉积温度和压强分别为250 ℃和0.1 Torr(1 Torr≈133.3 Pa).

2)薄膜制备结束后,放置于马弗炉内600 ℃退火30 min.

3)在直径为400 μm掩膜版的辅助下,利用热蒸镀的方法将Au制备于HfNx∶Zn薄膜上,形成顶电极.

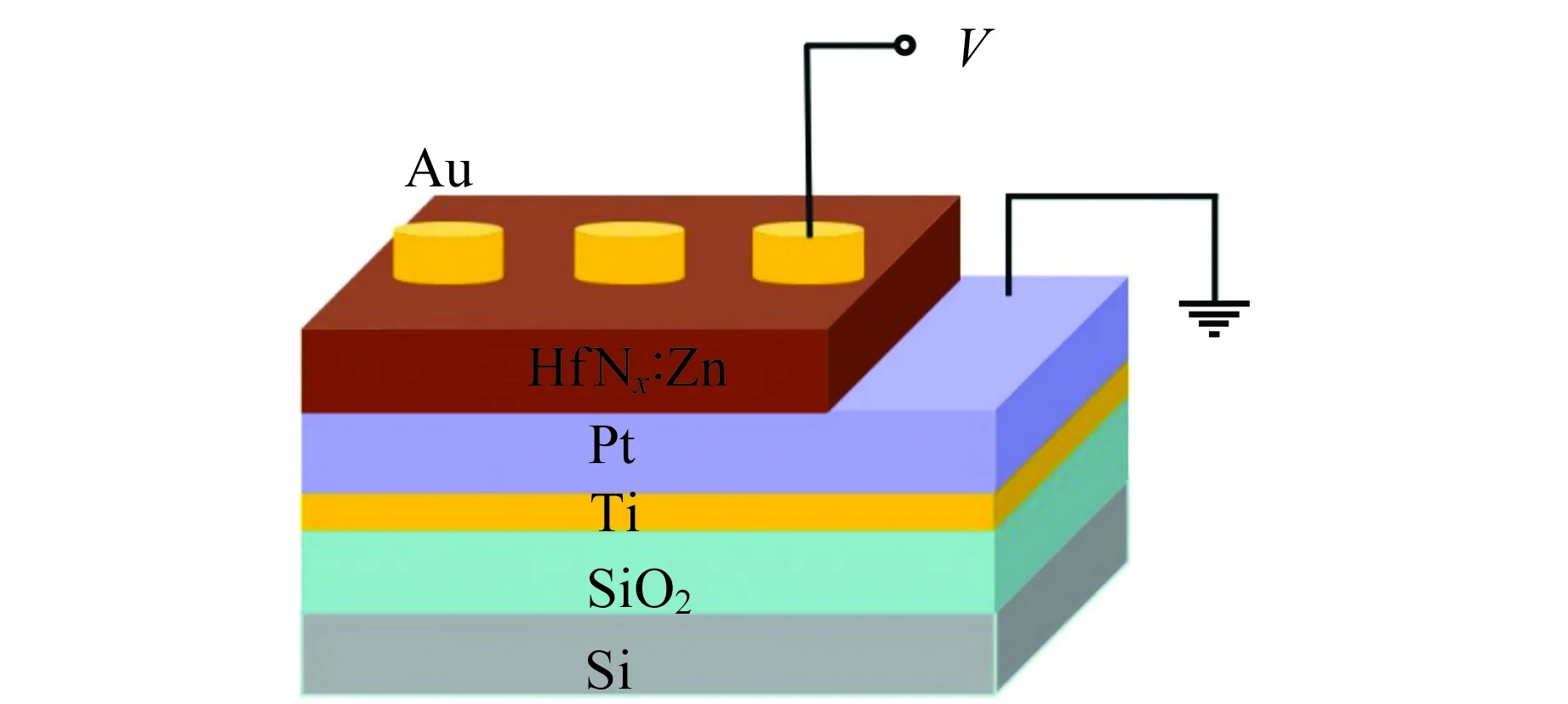

最终所获得的Au/HfNx∶Zn/Pt阻变式存储器件结构如图1所示. 利用美国安捷伦公司的Agilent B1500A半导体分析仪分析与测试器件的电学性质. 在测试中,将Pt底电极接地,在Au顶电极施加正或者负电压.

图1 Au/HfNx∶Zn/Pt阻变式存储器件的结构图

2 结果与讨论

2.1 HfNx∶Zn薄膜的表征

采用德国布鲁克公司的DIMENSIONICON型号原子力显微镜和日本理学公司的D/MAX2500型号X射线衍射仪对HfNx∶Zn薄膜的结构组成以及物相结构进行表征.

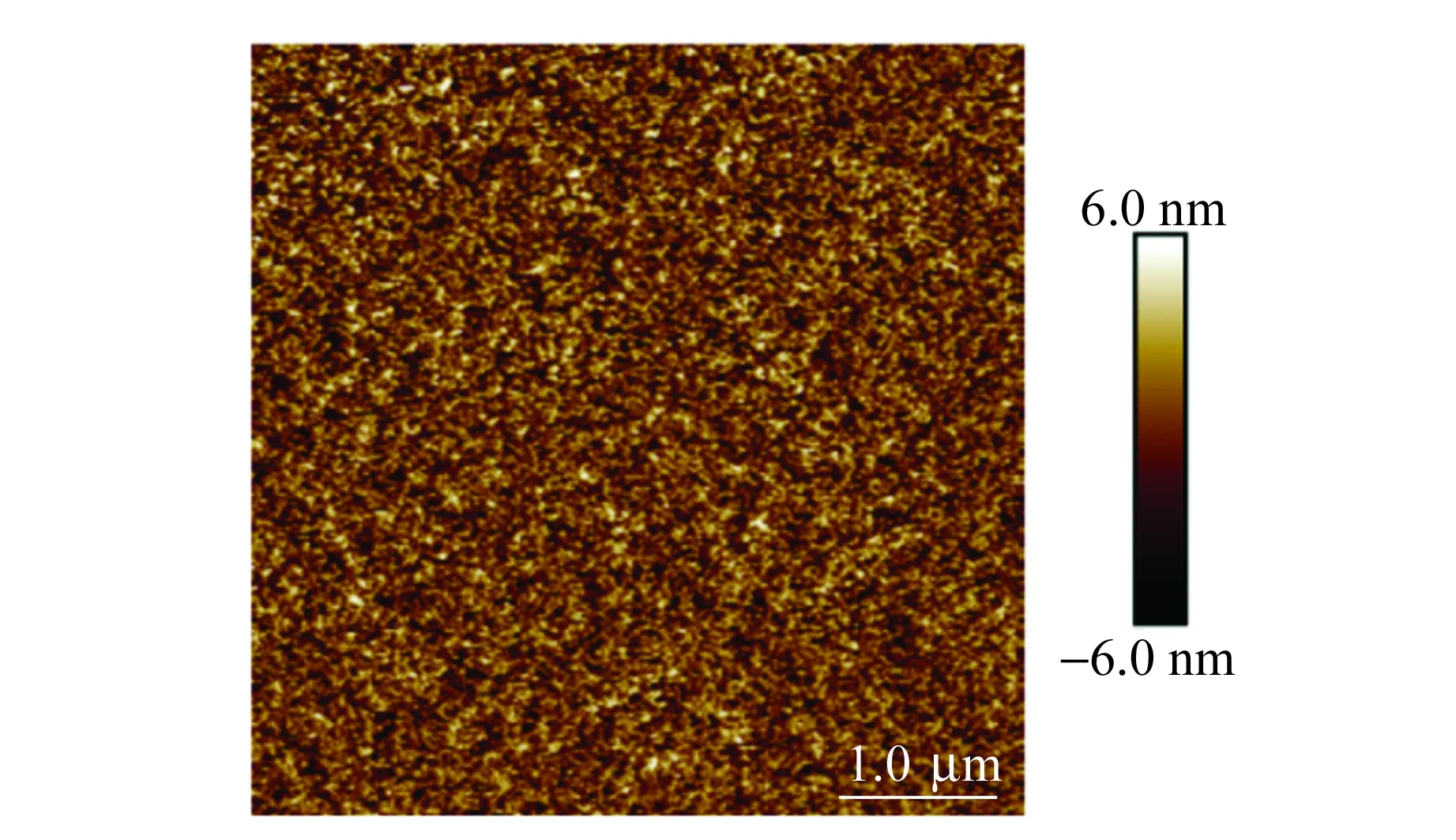

图2是HfNx∶Zn薄膜表面的AFM测试图像,其粗糙度Ra=1.41 nm,结果表明该薄膜生长具有高均一性.

图2 HfNx∶Zn薄膜表面的AFM测试图像

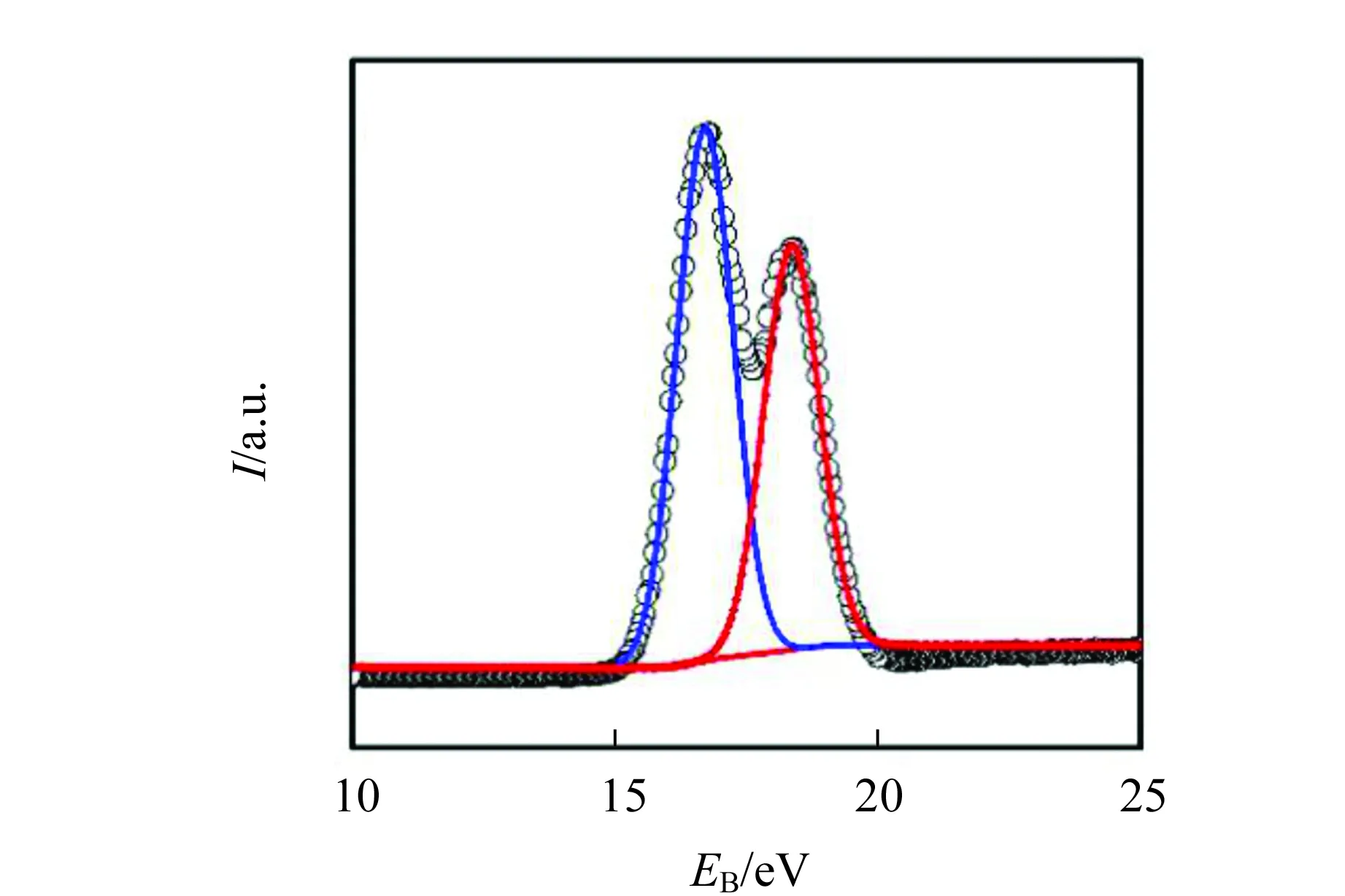

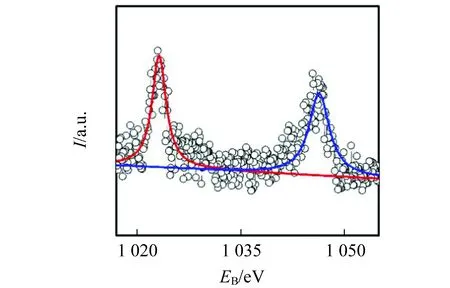

图3是HfNx∶Zn薄膜的XPS能谱,其中Hf 4f,Zn 2p,N 1s峰位分别位于18.4 eV和16.8 eV,1 046.3 eV和1 023.2 eV,398.3 eV,与文献[17-18]报道的能级一致. 结果表明薄膜是由Hf,Zn和N元素组成,各元素所占的质量分数分别为42.3%,9.2%和48.5%. N元素的质量分数较HfN理论化学式有一定程度降低,这证明Zn元素的掺入在薄膜中引入了大量的N空位缺陷.

(a)Hf 4f

(b) Zn 2p

(c) N 1s图3 薄膜中Hf 4f ,Zn 2p和N 1s的XPS 能谱

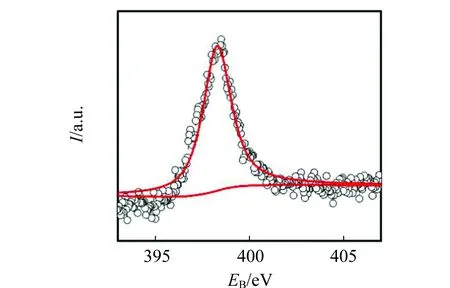

图4是HfNx∶Zn薄膜与掺杂Zn前的HfNx的X射线衍射图谱. XRD图谱显示在HfNx掺杂Zn元素之前,其晶格结构是非晶状态. 而HfNx∶Zn薄膜的XRD图谱则显示出一些尖锐的特征衍射峰与Zn3N2的结构标准谱图一致[19],这说明在HfNx∶Zn薄膜中存在Zn3N2的结晶体,也验证Zn元素的确掺入了薄膜.

图4 HfNx∶Zn薄膜的XRD能谱表征

2.2 HfNx∶Zn器件阻变性能表征

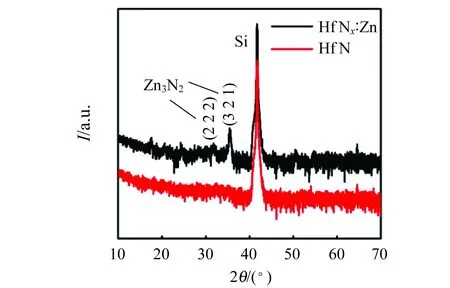

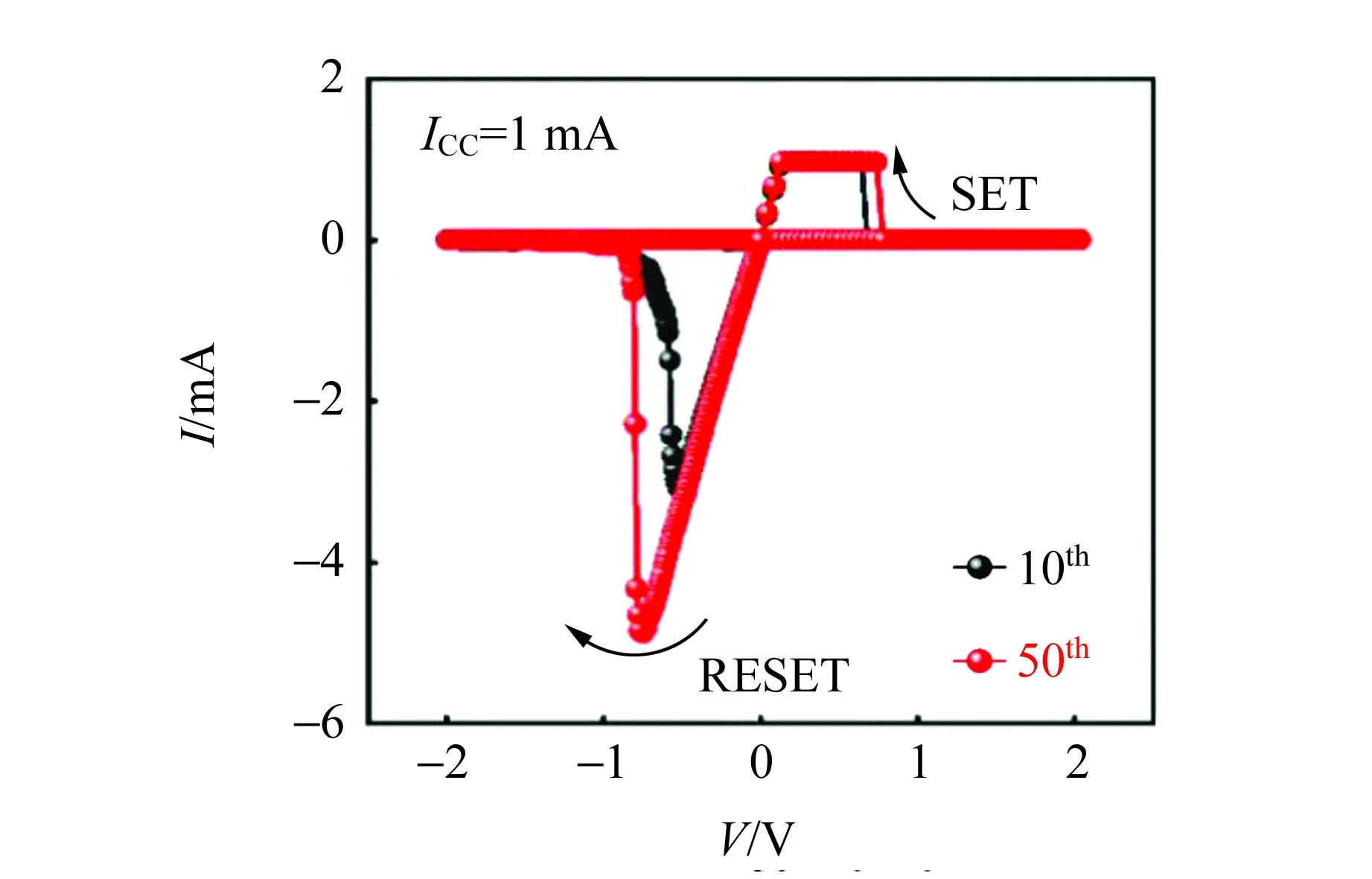

器件运行过程中设置1 mA的限制电流(ICC),用于避免器件产生永久性击穿. 器件测试中采用直流扫描电压模式,器件开启(SET)与关闭(RESET)的电压扫描区间分别为0 V→2 V→0 V 和0 V→-2 V→0 V. 定义电流正方向为由顶电极流向底电极.

图5所示为Au/HfNx∶Zn/Pt器件的I-V特征曲线. 在器件开启过程中:在正向电压扫描区间为1.5~2 V时,器件电流随着电压增大而减少,即负微分电阻效应[11,20];而当正向电压由2 V回扫至约0.7 V时,电流量级突然增加,器件由高阻态(HRS)向低阻态(LRS)转变. 此时的电压被称为开启电压(VSET). 在器件关闭过程中,通过对器件施加反向扫描电压0 V→-2 V→0 V,在电压达到约-0.7 V时器件电流达到最大值后发生急剧降低,器件状态由LRS向HRS转变. 此时的电压和最大值电流被称为关闭电压(VRESET)和关闭电流(IRESET).

图5 Au/HfNx∶Zn/Pt器件的单次I-V特征曲线

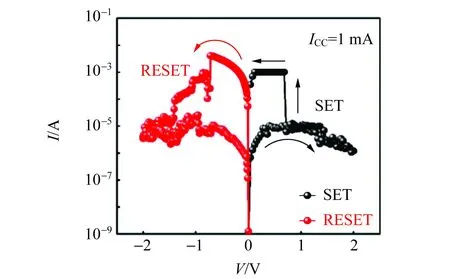

如图6所示,器件在进行50组I-V特征曲线的循环过程,器件电阻可以通过开启和关闭过程在高阻态和低阻态之间进行相互切换,展示了器件良好的运行重复性.

图6 Au/HfNx∶Zn/Pt器件多次循环的I-V特征曲线

上述结果表明,Au/HfNx∶Zn/Pt器件具有双极性的阻变特性,将之应用于信息存储有很好的发展潜力.

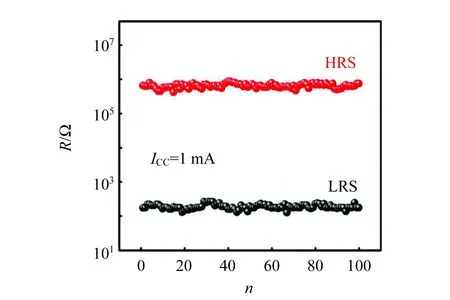

为了进一步测试Au/HfNx∶Zn/Pt器件运行的可靠性,对连续100组循环耐受性I-V曲线进行统计.

图7是器件高阻态和低阻态随循环次数的变化情况. 器件高阻值主要分布在105~106Ω之间,而低阻值主要分布在102~103Ω之间. 因此器件的存储窗口值基本保持在大于103的范围内,足以用于区分HRS与LRS.

图7 100次连续循环测试中器件的 高阻态和低阻态分布

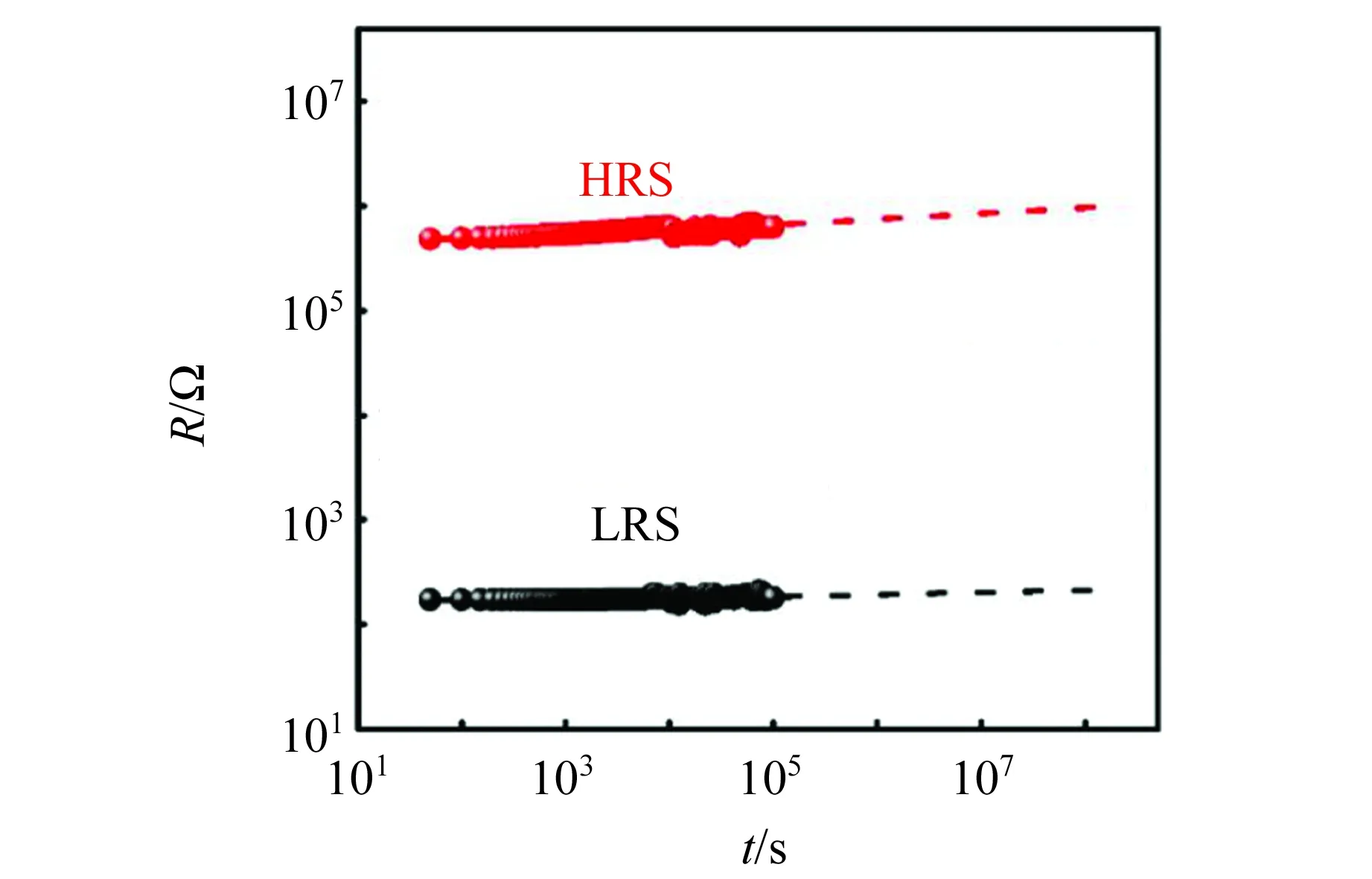

研究器件的保持特性,如图8所示,即使在85 ℃下器件也具有良好的保持特性. 在105s的信息保持时间下,器件的高阻和低阻并无明显的退化,也证实了器件信息的非易失性.

图8 在85 ℃下器件高阻态和低阻态的信息保持特性

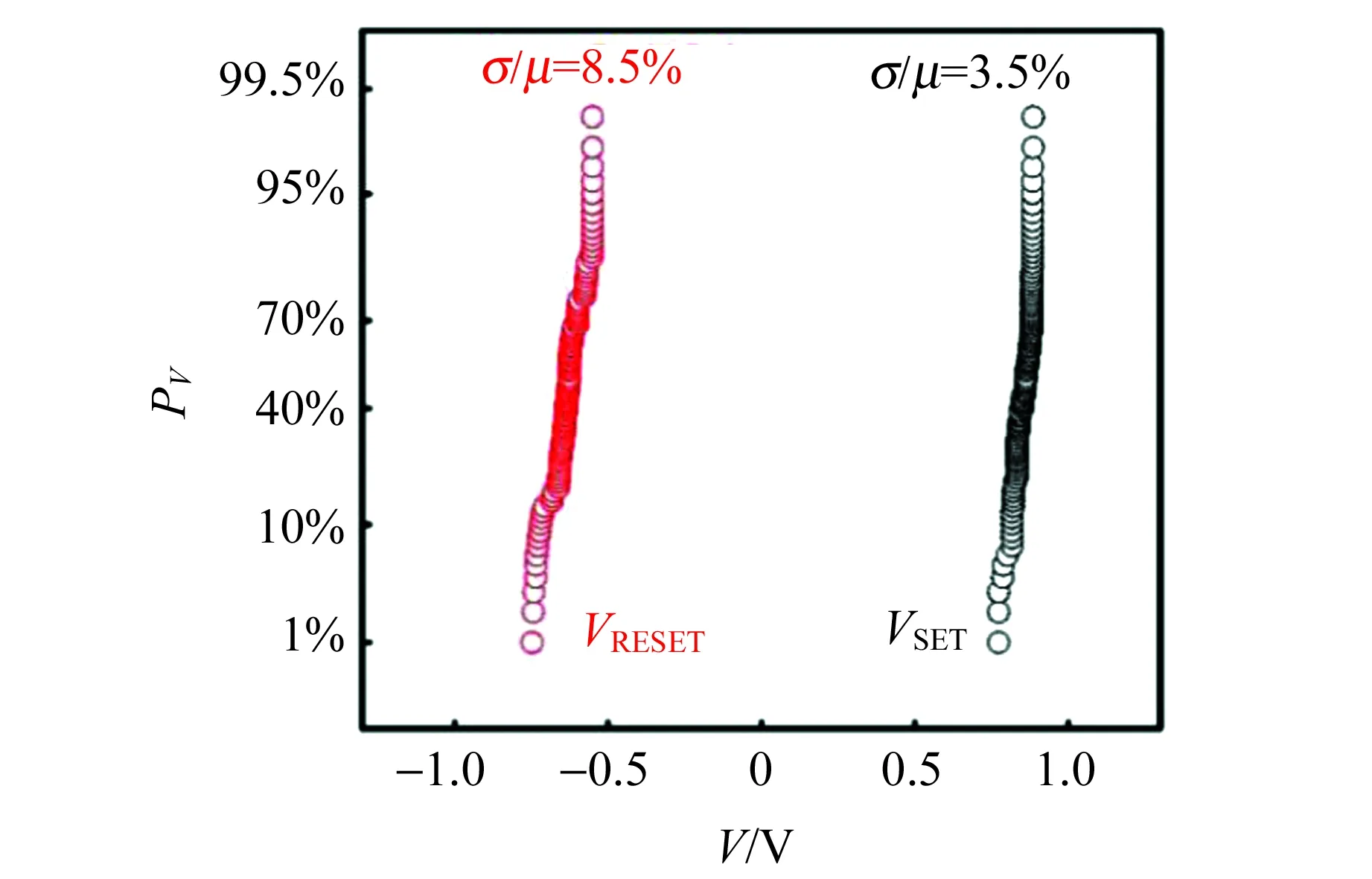

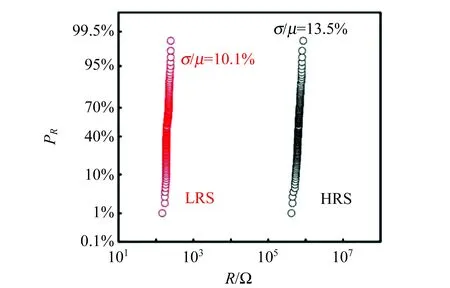

图9(a)是器件在100组循环后VSET与VRESET的累计概率分布,其波动性大小分别为3.5%和8.5%,其中波动性被定义为电压分布标准差与平均值的比值. 图9(b)是100次循环测试器件高低阻的累计概率分布,其波动性大小分别为13.5%和10.1%.

(a)电压

(b)电阻图9 100组循环后器件的电压与电阻波动性累计概率

综上所述,Au/HfNx∶Zn/Pt器件具有较低的阻变波动性和可靠的阻变性能.

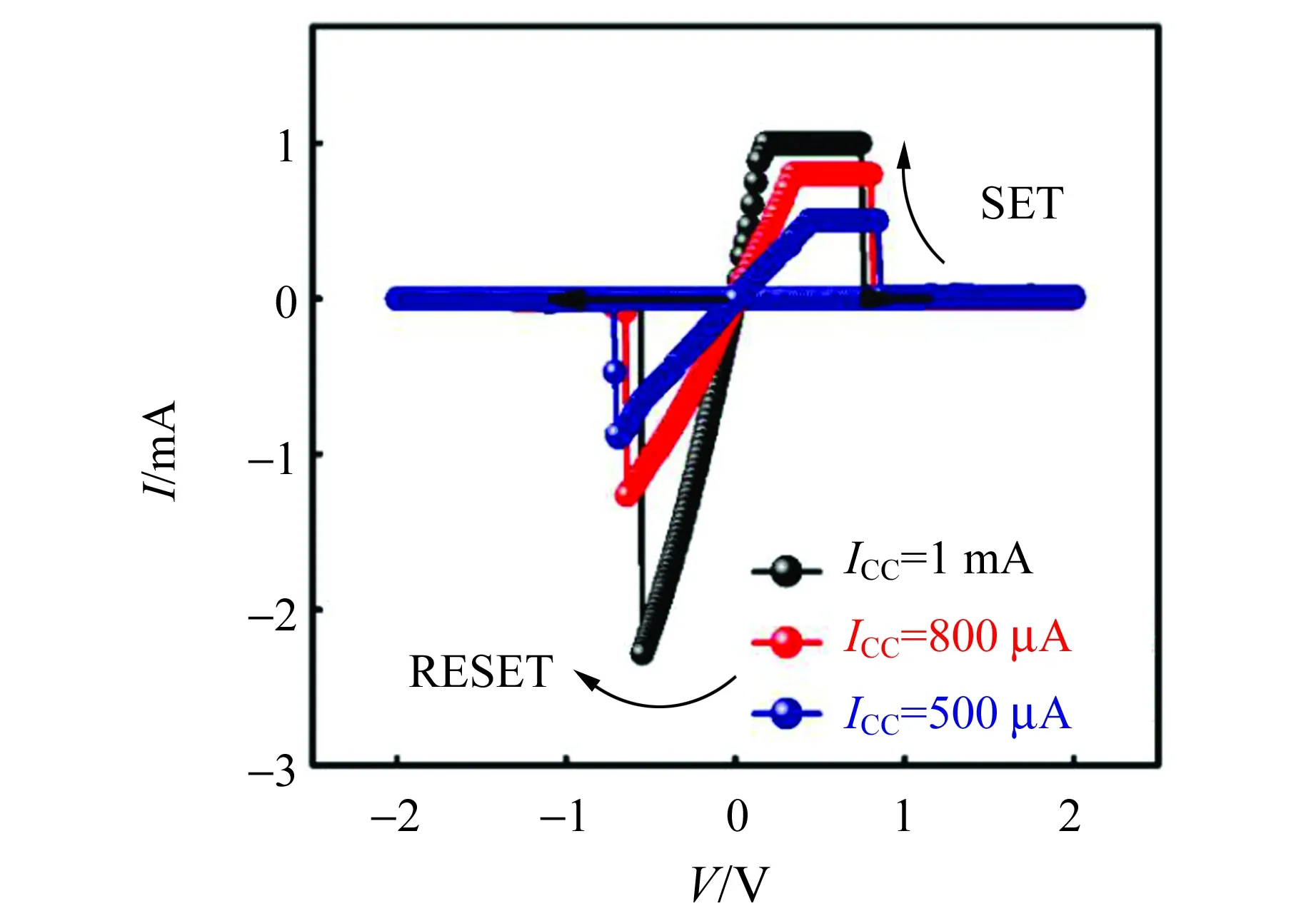

Au/HfNx∶Zn/Pt器件能够展示多级存储的功能. 根据文献[8]报道,器件的低阻值能够通过限制电流大小进行调节. 如图10所示,通过将限制电流由1 mA改变至800 μA 和500 μA,器件低阻可以由约102Ω调节至约103Ω. 从图10可以看出,以上3种低阻态可以清晰地得到分辨,能够在实现多级存储时避免运行过程中的误读操作.

图10 不同限制电流下Au/HfNx∶Zn/Pt器件 典型的I-V曲线

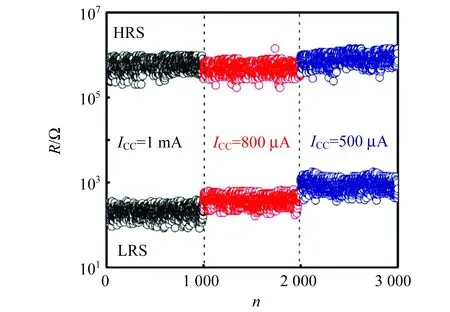

图11是器件各阻态1 000个循环周期的耐久性测试,器件并未出现任何明显退化,其窗口值仍然能够保持在100左右.

图11 1 000组循环耐受性测试电阻的分布

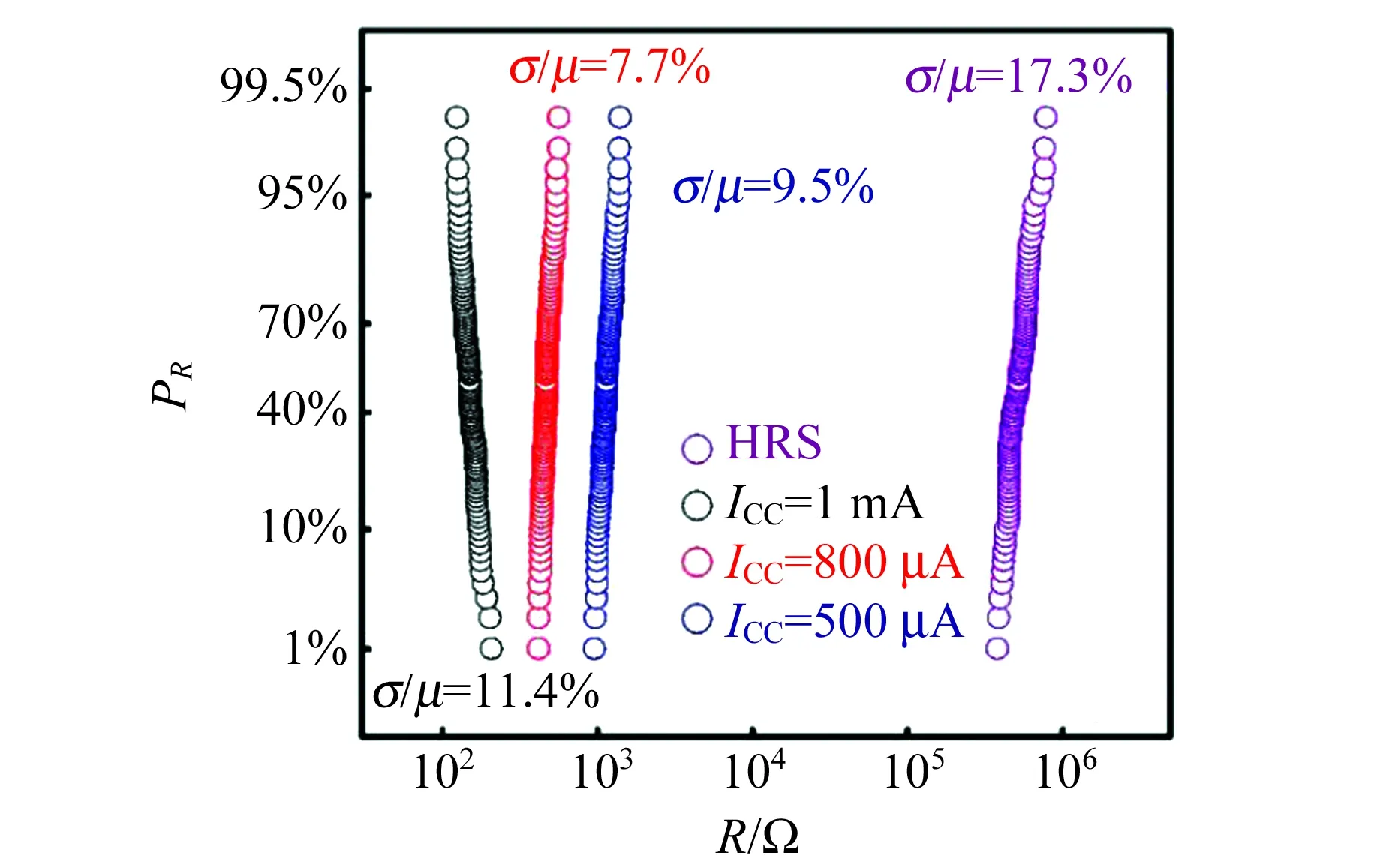

图12是通过定量统计的不同限制电流下窗口值的波动性,在1 mA,800 μA和500 μA的限制电流下,器件多级电阻态的相对波动分别仅为11.4%,7.7%和9.5%. 高度均一的阻变行为和高窗口值确保了电阻态之间没有误读现象,这也表明了Au/HfNx∶Zn/Pt器件在高密度多级存储具有潜在应用.

图12 1 000组循环耐受性测试电阻波动性的统计

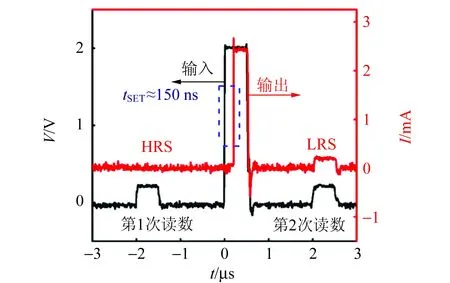

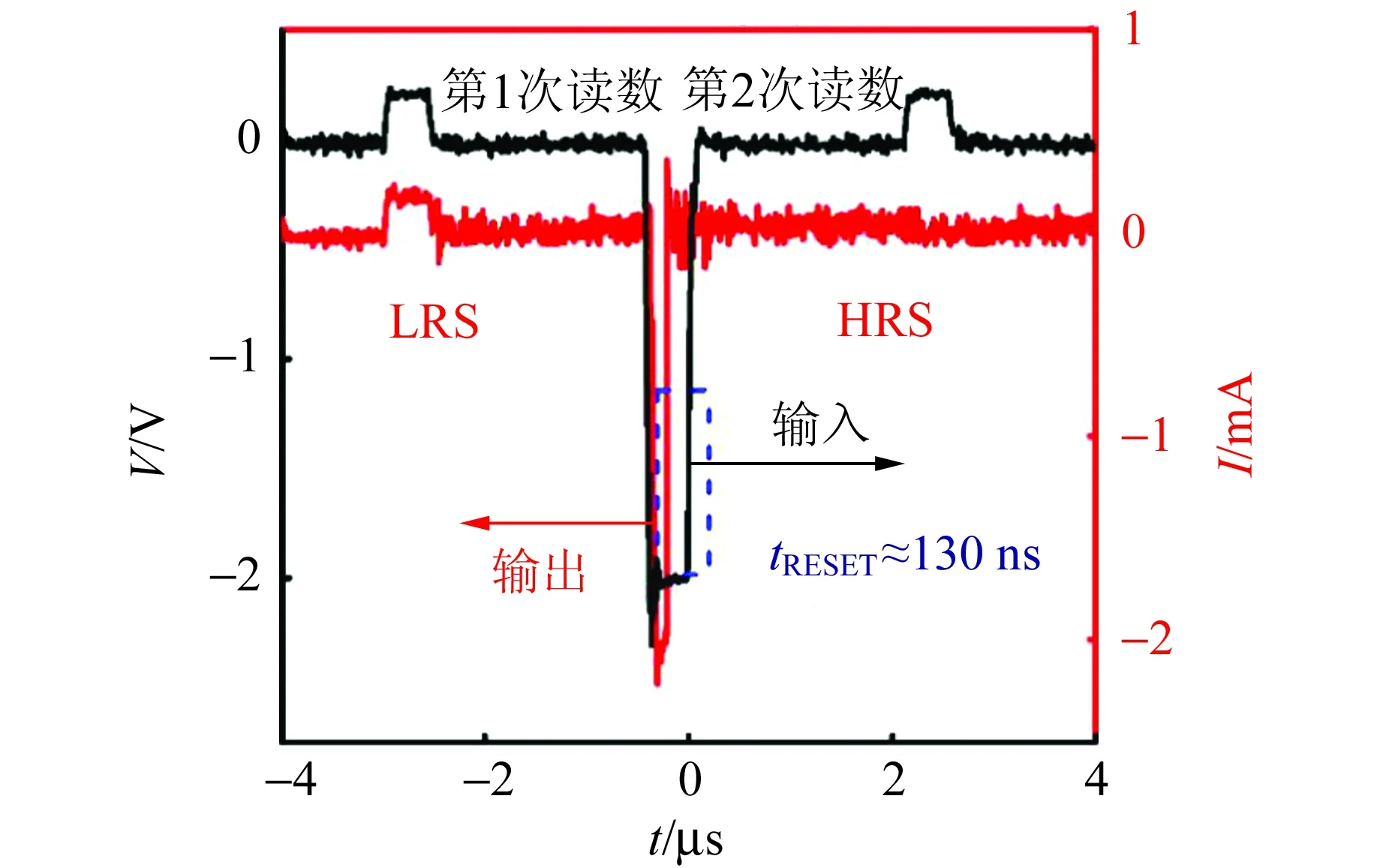

为了评估器件的擦写速度,采用的实验设备包括脉冲发生器(3390,Keithley)、示波器、存储器单元和负载电阻器. 通过阻变过程中“输入信号”和“输出信号”之间的延迟时间来估算阻变的切换速度. 图13将幅度和宽度为[2 V/0.5 μs]/[-2 V/0.5 μs]的SET/RESET脉冲施加在器件上,实现器件在高阻态与低阻态间的切换,其开启和关闭时间分别约为150 ns和130 ns.

(a)器件开启

(b)器件关闭图13 器件开启和关闭的时间脉冲测试

上述结果说明Au/HfNx∶Zn/Pt器件具有快速擦写功能.

2.3 阻变机制讨论

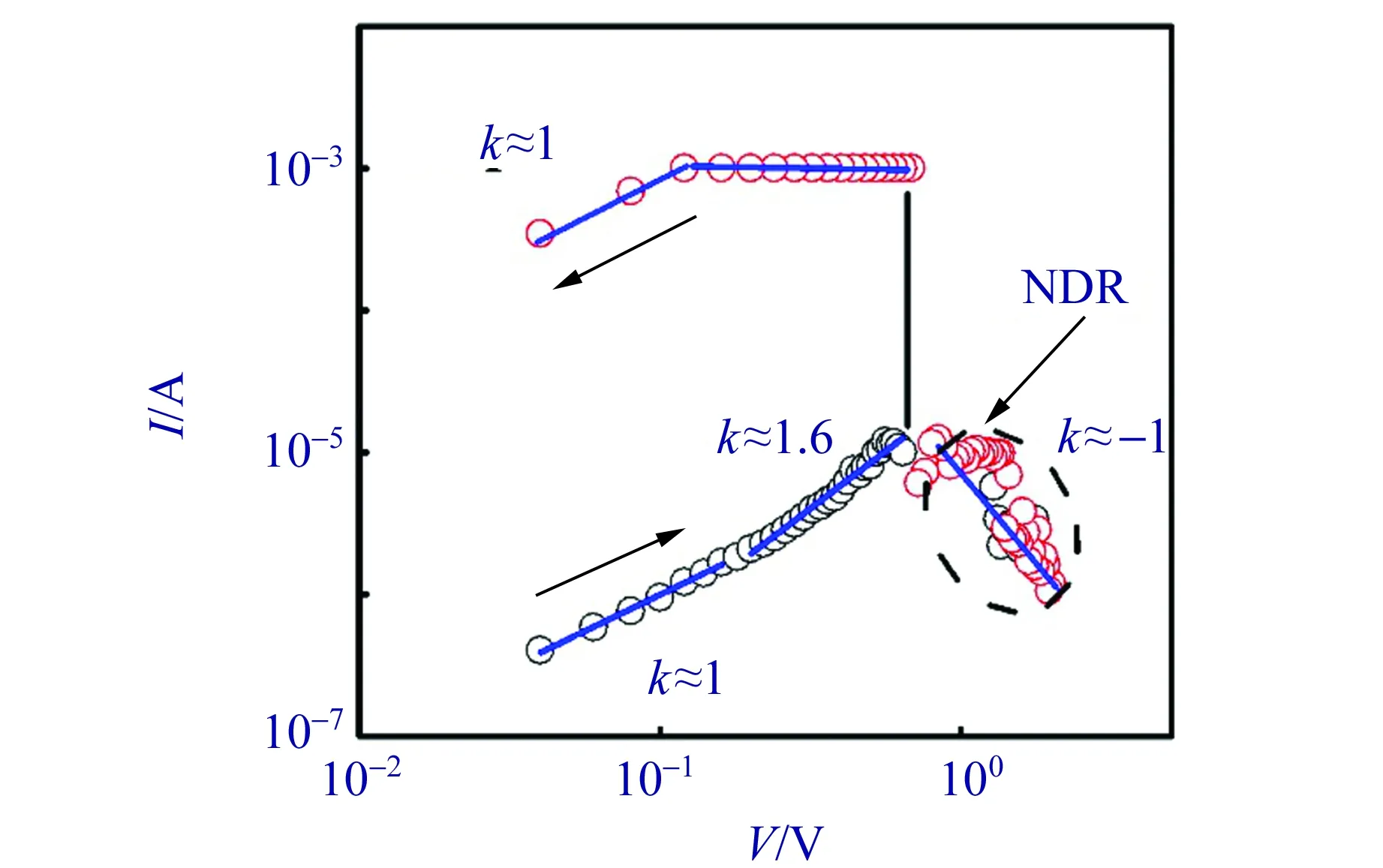

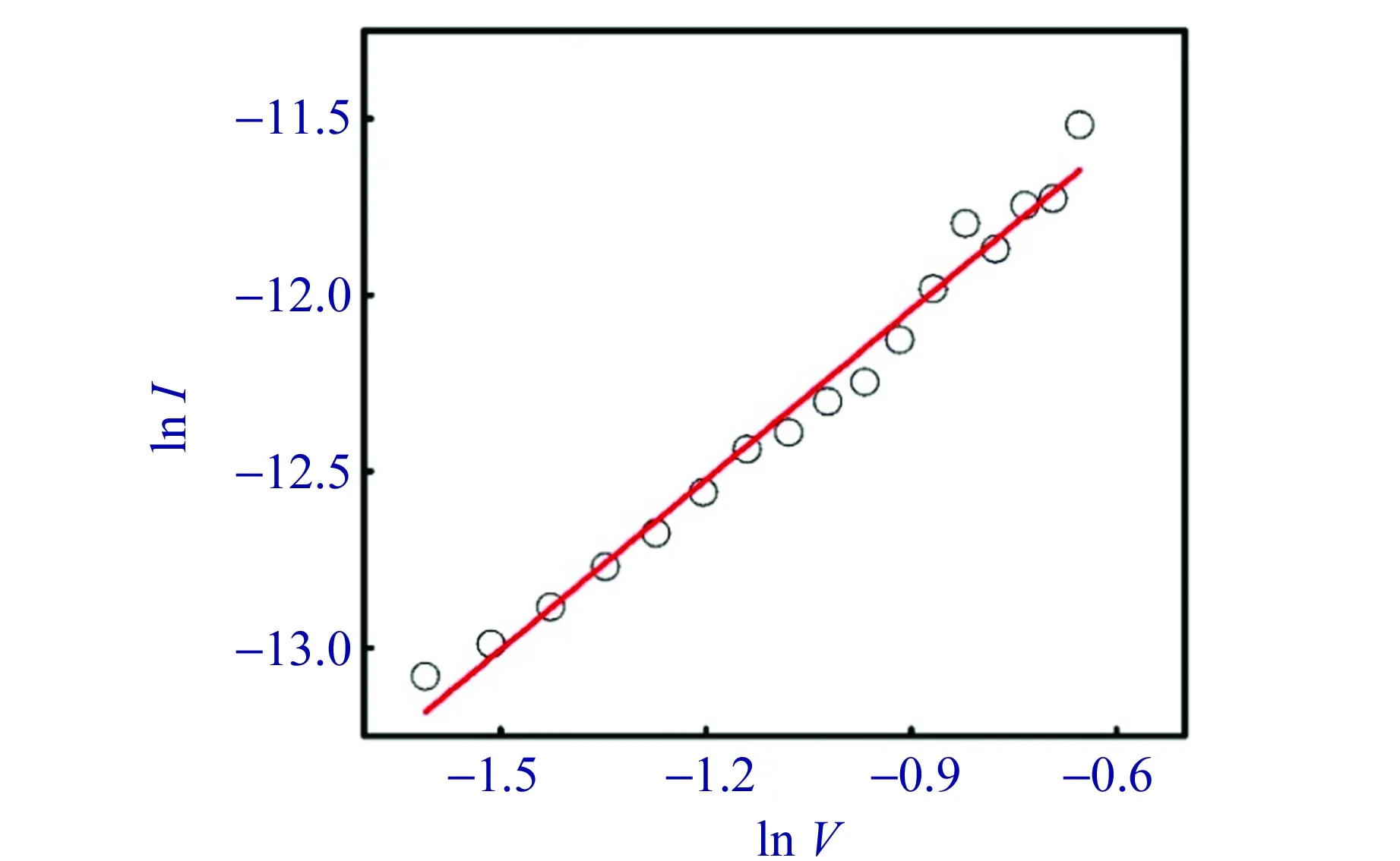

为了探究Au/HfNx∶Zn/Pt器件运行的阻变机制,对器件高阻态和低阻态的导电机制进行了分析. 图14是器件高低阻态在对数坐标下的伏安特性曲线,图15是HRS高电压区域电流与电压的拟合.

图14 器件在高阻态和低阻态对应的对数I- V曲线

图15 HRS高电压区域电流与电压的拟合

可以看出高阻态和低阻态呈现着不同的导电机制. 器件低阻态中电流与电压的对数曲线呈线性依赖性,其曲线斜率接近于1,表明其符合欧姆定律. 而对于高阻态I-V曲线则相对复杂,主要由3个区域组成:

1)在低电压区域(<0.3 V),曲线斜率接近于1,符合欧姆定律,其电子传输机制能够被热离子发射所解释[21].

2)在较高电压区域(0.3~0.7 V),其曲线斜率接近于1.6(如图15所示),此I-V曲线能够通过陷阱控制的空间电荷限制电流(SCLC)模型表示为[21-22]

其中,lnI与lnV成线性关系,n和nt分别是自由电子和捕获电子的浓度. 因此,此区域的传输特性主要依赖于薄膜体内缺陷态对于电子的捕获作用[22]. 与图3中XPS能谱分析结果相对应,HfNx∶Zn薄膜中存在的大量N空位缺陷态可能在此阶段起到主要作用.

3)在高电压区域(0.7~2 V),器件电流随电压增加而降低,呈现典型的负微分电阻(NDR)效应. 根据文献[20]报道,不同于上一阶段的体内缺陷态起主要作用,具有负斜率的负微分电阻行为很有可能与界面缺陷态有关. 根据图14所示的SCLC传导机制[20],从Pt电极注入的载流子被体内缺陷态. 随着体缺陷态的填充,导致薄膜电阻降低,最终施加的偏压逐渐开始作用于界面态. 因此,施加相对高的偏压(>0.7 V)会导致Au/HfNx界面处的费米能级显著上升,电子将被低于费米能级的界面态捕获[11]. 因此,电流随着电压的增加而降低,在器件开启过程中出现了负微分电阻现象.

3 结 论

利用原子层沉积的方法,通过HfNx∶Zn薄膜制备了可以稳定运行的Au/HfNx∶Zn/Pt阻变式存储器件. 该器件具有很高的窗口值(103)、良好的保持时间(85 ℃下105s)以及快速擦写速度(约150 ns),展示出了优异可靠的器件性能. 通过调节限制电流的大小,能够有效地调节器件的低阻值,实现了多级存储的功能. 通过对开启过程中不同电压区域的I-V曲线拟合,可以得知阻变机制是由体内缺陷态诱导的空间电荷限制电流引起的. 同时,器件阻变过程中所发生的负微分电阻现象,可以归因于界面态变化所致. 上述结果表明,Au/HfNx∶Zn/Pt器件在发展信息存储方面具有非常好的前景,有望成为新兴电子器件的重要选择之一. 遵循“发现新现象-探究物理原因-探索新应用”的新思路,本文工作也是培养本科生理论与实验结合能力的课程改革的有益尝试.