基于Labwindows/CVI的铯原子喷泉钟时序控制系统研制*

2019-06-14刘浩刘丹丹阮军王心亮张首刚

刘浩,刘丹丹,阮军,王心亮,张首刚

(1.中国科学院 国家授时中心,西安 710600;2.中国科学院 时间频率基准重点实验室,西安 710600;3.中国科学院大学,北京 100049)

0 引言

铯原子喷泉钟以脉冲方式工作,时序控制系统通过输出控制信号,同步调控光学系统、微波频率综合器,实现原子的冷却—上抛—选态—微波激励—探测等周期性运行。通过数据采集系统采集铯原子的飞行时间信号,经过计算获得伺服控制系统的参数,实现频率锁定[1]。目前运行在NTSC-F1铯原子喷泉钟上的时序控制系统,由于其硬件版本较低,系统整体性能提升空间不足。同时其系统通用性不理想,时序的各项参数设置修改比较繁琐,所以需要研制一套界面友好,操作人性化,性能更优的时序控制系统应用于NTSC-F2铯原子喷泉钟上。

本文针对NTSC-F1时序控制系统存在的不足,并依据NTSC-F2铯原子喷泉钟对控制时序的要求,基于Labwindows/CVI平台,通过系统模拟、硬件选型、软件设计、性能测试等流程完成了时序控制系统的研制,实现了19路同步时序的控制与输出。

1 工作原理

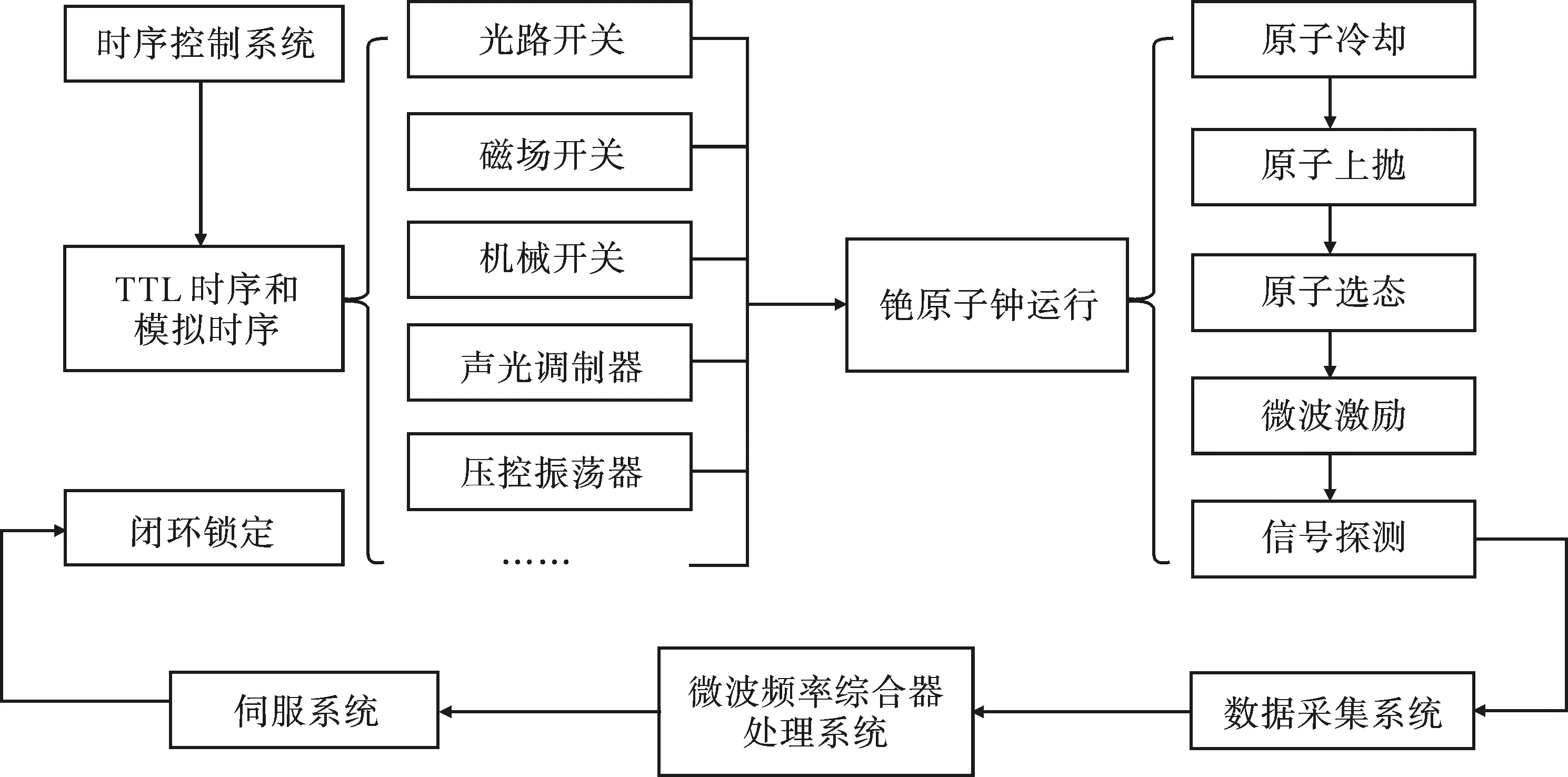

时序控制系统需要输出特定的时序,控制光开关、磁场开关、声光调制器、压控振荡器等的关断,实现铯原子在高真空、高磁屏蔽的物理环境中冷却—上抛—选态—微波激励—探测等过程的周期性运行[2]。时序控制系统首先通过输出TTL信号控制二维磁光阱(2D MOT)冷却光和磁场开启,制备水平方向慢速原子束。同时打开三维磁光阱(3D MOT)冷却光和磁场,等慢速原子束注入3D MOT真空腔后,俘获并囚禁铯原子束,实现铯原子团装载。装载完毕后关闭磁光阱内磁场,通过激光对原子团进行冷却。随后改变上下两组俘获光失谐,实现铯原子的上抛。上抛约1.5 ms后通过时序控制激光频率失谐量的增加和激光功率的减小,实现对原子团的进一步冷却。之后,利用抽运激光将上抛中的铯原子全部抽运至|F=4>态上。|F=4>态的铯原子上抛进入选态腔,经由选态腔中的微波场作用,使得|F=4,mF=0>态的原子跃迁到|F=3,mF=0>态上。跃迁后的铯原子飞出选态腔后,打开选态推光将|mF≠0>态的铯原子推走。经选态后的铯原子再进入激励腔与微波场发生作用,随后铯原子继续上升达到顶峰后开始回落,在回落过程中再次进入激励腔,再次与微波场发生作用,完成整个Ramsey 跃迁过程。铯原子团继续下落进入探测区进行飞行时间信号的探测。利用数据采集系统计算铯原子跃迁几率[3-5]。调控微波频率综合器的频率获得Ramsey跃迁条纹,在Ramsey中心频率附近进行调制,根据其两侧跃迁几率差值得到误差控制信号,经PID运算后输出伺服控制晶振,实现频率锁定。NTSC-F2时序控制系统工作原理如图1所示。

图1 时序控制系统工作图

2 时序控制系统研制

NTSC-F2铯原子喷泉钟的运行由19路时序信号来控制,其时序波形如图2所示。这19路时序由15路TTL信号和4路模拟信号组成,依次编号为第1路,第2路,……,第19路。其中信号周期为2 s,信号延时为t,用时为T。

图2 NTSC-F2的控制时序

2.1 系统模拟

基于LabWindows/ CVI 为平台设计时序控制模拟系统界面,通过C语言进行编程,利用控件触发程序运行,实现波形输出与显示。具体流程为,通过LabWindows/ CVI搭建系统界面,并设置各控件初始参数。再利用GetCtrlVal函数获取界面输入参数,包括起始电平、用时、延时、周期和相位等参数。再由算法将所获得的波形参数转化为信号生成SquareWave函数所需参数,并由SquareWave函数生成时序,其公式表示为

X[i]=V0×SquareWave (φ0+f×360×i),

(1)

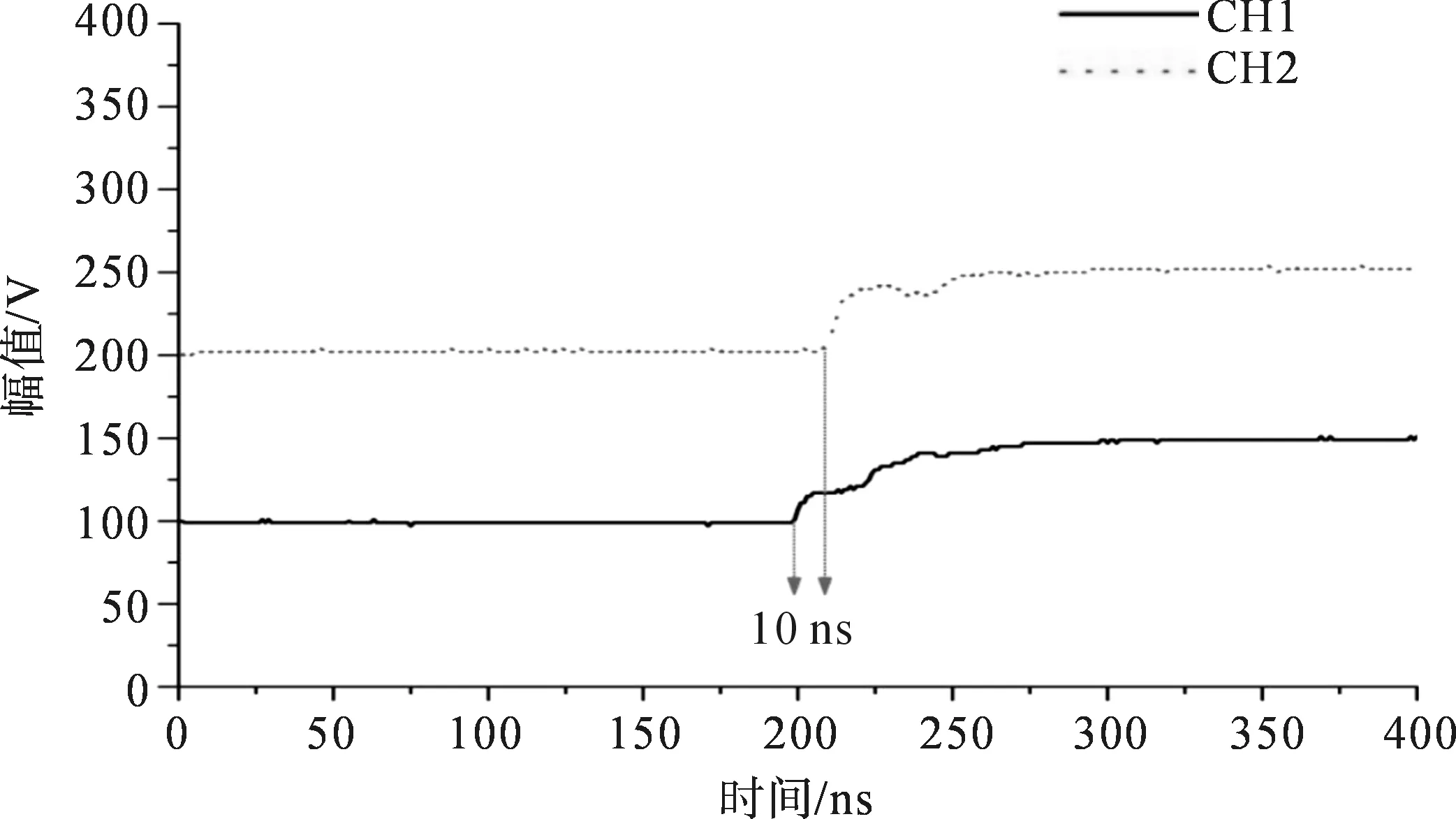

{SquareWave[i]=1.0 0 SquareWave[i]=-1.0 (duty/100.0×360.0) 式(1)中,数组X[]用于存储一个周期的信号数据点,V0代表起始电平,φ0代表初始相位,f代表频率,modulo为取模运算,duty代表占空比。 最后利用函数PlotY将各路波形显示在Graph控件上。时序控制模拟系统运行效果如图3所示,信号波形与期望值基本一致,并可以通过参量设置实现对时序信号的控制。 图3 时序控制模拟系统 在铯原子喷泉钟的运行过程中,原子冷却、上抛,探测过程中激光频率、功率的变化,以及时序信号控制的各开关关断需要在极短的时间内完成,这对硬件性能提出了较高的要求。选择NI公司基于PXI总线的工控机作为硬件模块的核心,PXI总线的传输速率为132~264 MB/s,各模块板卡接入10 MHz参考时钟,能够有效进行多板卡信号的同步处理[6]。PXIe1082工控机内部集成嵌入式控制器PXIe-8840,采用两块计数器卡PXI-6602输出15路TTL信号,一块模拟输出卡PXI-6733输出4路任意波模拟信号,并通过多功能I/O卡PXIe-6361来实现信号采集。 PXIe-8840是一款基于Intel Core i5-4400E处理器的高性能嵌入式控制器,具有2.7 GHz基频、3.3 GHz双核处理器和单通道1 600 MHz DDR3内存,极适合用于处理器密集型、模块化仪器和数据采集应用。PXI-6602卡有5 V,8通道的计数器/定时器,用于输出时序中的TTL电平信号。PXI-6733卡有8路模拟输出通道,可同时控制8路不同硬件,单通道输出更新率最高可达1 Ms/s[7-8]。将上述板卡插入PXIe-1082机箱内,通过配套的线缆接入接线盒,再由BNC接连接线盒输出端与被控子系统,这便构成了时序控制系统的硬件模块,其总体结构如图4所示。 图4 硬件模块框架图 软件系统用于实现对硬件模块的控制,基于时序控制模拟系统进行开发,在工控机平台上,通过程序算法调用并控制硬件模块输出特定的19路时序信号,实现各开关和子系统按照特定的方式运行,完成铯原子喷泉钟的稳定工作。 首先借助时序控制模拟系统开发的系统界面,完善Command Button、Numeric、Text等控件作为时序参量输入、时序开关和辅助功能调用键。随后针对各控件编写相应的回调函数,由DAQmxCreateAOVoltageChan配置物理通道,再通过GetCtrlVal函数获取各时序波形参量,包括时序的起始电平、用时、延时和相位等,并利用算法将这些参量再转化为信号生成函数所需的各参数。通过DAQmxCreateCOPulseChanTicks函数配置计数器源、TTL电平的极性、高电平时间、低电平时间、延迟时间。同时利用DAQmxCfgSampClkTiming函数设置采样时钟源和采样速率,并通过DAQmxCfgDigEdgeStartTrig函数配置触发信号[9]。最后根据偏振梯度冷却时间、采样速率将一个周期的波形数据写入数组中。当接收到触发信号时,则将数据顺序输出,实现时序输出。一个周期运行完毕,将其放入循环系统中便能实现信号周期性输出。通道采用同一个参考时钟源,以保证各通道间时间顺序上的确定关系。时序输出的具体流程图如图5所示。 图5 时序生成流程图 图5中4路模拟时序通过GenSquareWave函数生成,其公式表示为 X[i]=V0×SquareWave (φ0+f×360×i), (2) {SquareWave[i]=(phase_i/360.0<=duty/100.0) ?V0:-V0} 式(2)中,数组X[]用于存储一个周期的模拟信号数据点,V0代表起始电平,φ0代表初始相位,f代表频率,duty代表占空比。 4路模拟信号每个周期都有一段用时(高电平向低电平跳变时所需时间),利用程序 A=(yongshi/zhouqi)×numElements; B=(yanshi/zhouqi)×numElements; for(i=k;i {SquareWave[i]=SquareWave[i+1]-DP×(i-A)/numElements+DP;} 和 for(i=A;i {SquareWave[i]=SquareWave[i+1]+DP×exp((A+B-i)/B)-DP;} 实现模拟信号高电平到低电平呈现线性下降和指数下降。 时序控制系统主体功能基本实现后,同时开发相应的辅助功能,如可以回采已输出时序,在界面上显示其波形的虚拟示波器,方便用户运算数据的计算器,用以保存重要参数和数据的记事本,DDS频率串口调控以及系统操作指南等功能。通过LaunchExecutable函数,实现辅助功能在操作界面上的统一调用。 时序同步是保证各模块协调工作的首要元素,NTSC-F2铯原子钟运行的各个过程要求各物理参量以一定时间顺序输出,需要各板卡间有极高的的同步性。多设备之间的同步主要依靠两种方法:①我们可通过共享主时基(或称之为参考时钟)避免了相位误差,并共享一个开始触发来实现同步。②可通过直接共享采样时钟,多个对象使用相同的采样率来完成同步。我们根据NTSC-F1时序控制系统研制的经验,第1种方法要求较高的频率信号,这里采用第2种方法,多块板卡的输出任务采用相同的采样率来完成同步[10]。我们将PXI机箱背板的10 MHz参考时钟作为各槽位板卡的采样时基,利用软件配置各板卡的时钟源,并设置相同的采样速率,通过PXI触发总线的星型触发方式,实现3块板卡之间的同步。同时在软件层面,优化算法,提升程序的响应速度。 打开NTSC-F2铯原子喷泉钟时序控制系统输出第1路TTL时序和第16路任意波模拟时序,信号波形如图6所示。两路信号的各项参数与设定值所一致。测量其他各路信号的参数,也均与设定值一致。 图6 时序输出波形 为评估时序控制系统的同步精度,我们先后观测了一块计数器卡PXI-6602输出的两路TTL信号,以及计数器卡PXI-6602和模拟输出卡PXI-6733输出的两路信号,其波形分别如图7和图8所示。可以看到同板卡所生成的时序同步性能极为优越,约在10 ns左右。影响时序同步精度的主要因素则是不同型号板卡所生成的时序,时序同步精度在300 ns以内。 图7 同板卡时序同步精度 图8 异板卡时序同步精度 本文着重介绍了NTSC-F2铯原子喷泉钟时序控制系统的研制,并对系统的性能进行了测试。目前系统精确输出并控制19路时序信号,信号各项参数也与期望值一致。时序输出同步精度达到300 ns以内,优于NTSC-F1的10 μs。同时相较于NTSC-F1时序控制系统,信号所有参数均可在界面上直接设置,同时实现了单路信号的输出和控制。接下来将主要针对时序控制系统操作界面的人性化进行完善,同时将通过共享主时基和共享采样时钟相结合的方式进一步提升时序同步精度。

2.2 硬件选型

2.3 软件设计

2.4 时序同步

3 系统测试

4 结论