一种新型高精度的RC振荡器设计

2019-06-13张明文尹勇生邓红辉

张明文,尹勇生,邓红辉

(1.武夷学院 机电工程学院,福建 武夷山 354300;2.合肥工业大学 微电子所,安徽 合肥 230009)

目前芯片的功能越来越多,集成度越来越高,时钟信号做为当前很多芯片必不可少的组成部分[1]。时钟可以用外部晶体振荡器产生,也可以用片内振荡器来产生。但片外的晶体振荡器,功耗较大,无法集成在芯片内部[2],成本较高,同时占用了PCB电路板的面积和芯片引脚。而RC振荡器由于结构简单、易于CMOS工艺集成、功耗低等优势[3]而成为目前片内集成振荡器的首选。但同时RC振荡器存在着频率不稳、易受电源电压、工艺偏差和比较器延时干扰等问题[4]。

在分析传统RC振荡器的基础上提出了一种改进型的RC振荡器,使其克服了频率不稳定、易受工艺偏差和比较器失调、延时影响等问题。

1 传统的RC振荡器及其工作原理

图1 传统RC振荡器及其时序图Figure 1 Traditional RC oscillator and its timing diagram

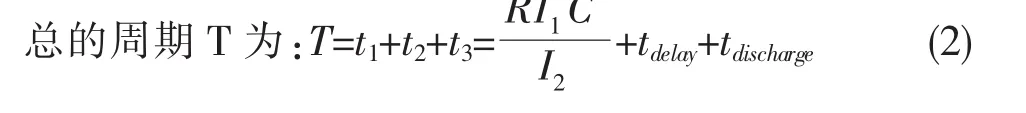

传统的RC振荡器结构和时序图[5]如图1所示。主要利用电流源在电阻R和电容C上产生电压,利用比较器比较其电压,并周期性对电容进行充放电来实现。具体工作原理如下:电路刚开始工作时假定VO为低电平,此时M1截止,电流I1在电阻R上产生VR=R*I1的电压,电流I2对电容C充电产生VC电压,当VC电压超过VR后比较器翻转,输出VO变为高,开关管M1导通,电容C通过M1开始放电,由于比较器失调和延时[6]的存在,输出VO并不是立即翻转,电容C会持续放电一段时间,VC电压趋近于0,此时VO变为低电平,开关管M1关断,电流I2开始对电容C充电。以上过程不断重复,电路就是在这样的循环中产生出振荡的VO。其时序图也见图1,VR=R*I1为定值,电容电压VC慢慢线性增加,在VC等于VR时由于比较器存在失调和延时,VO并不是立即翻转,而是保持原状态,直到VC电压上升到VC=R*I1+VOS,其中为VOS比较器的失调电压,这个时候VO才翻转,比较器的失调电压最终会转化成总的延时时间,充电时间主要取决于电阻R、电容C的大小、电流I1和I2的比例和延时时间。VO翻转后,M1开启,电容C开始放电,放电时间取决于电容C的大小和M1晶体管所允许流过的电流大小。在一个振荡周期中,其周期时间由充电时间tCharge、延时时间tdelay和放电时间tdisCharge组成[7],其中为了表示方便,将tCharge表示为t1、延迟时间tdelay表示为t2和放电时间tdisCharge表示为t3。由图1中可得式(1)、(2):

电容的充电时间为:

由上式(2)可知在振荡器的一个周期中,振荡器的振荡周期与电流I1、I2、电阻R的数值、电容C的数值、延时时间和放电时间都有关系。其中,放电时间又和电容C和M1晶体管有关。这样,从总体来看,振荡器的振荡周期与电流I1、I2、电阻R的数值、电容C的数值、延时时间和M1晶体管有关。为简化分析假定电流I1、I2成比例关系。这时振荡器的振荡周期只与电阻R的数值、电容C的数值、延时时间和M1晶体管有关。在振荡器设计中,频率是重要的指标,而频率和周期有关。为了保证频率稳定度,要做好这些器件参数的匹配、减小或者消除比较器的失调和延时、保证电阻R、电容C与M1晶体管的精度[8]。然而,1)在充电阶段,需要电阻R和电容C产生电压,在半导体工艺中,电阻R和电容C是两种不同的器件,它们的特性是不相同的,要使两者产生相同的电压是很困难的;2)在振荡器实际工作之间,振荡器的翻转主要靠比较器两端电压的差值来确定,这个差值又会受到比较器有限增益和失调电压的影响;3)放电时间很容易受到开关管和电容的影响;4)电路内产生的参考电压又很容易受电源电压和温度的影响。以上四点容易造成RC振荡器的频率不稳定。因此根据公式(2)和以上分析,传统的振荡器振荡周期由充电时间tCharge、延时时间tdelay和放电时间tdisCharge三部分组成,三部分时间相互独立又分别受不同的因素影响很难恒定,所以造成传统的振荡器振荡频率不稳定。基于此本文提出一种新的改进型RC振荡器,在新型振荡中,将只有充电时间tCharge和放电时间tdisCharge两部分组成,与延时时间tdelay没有关系。其中,放电时间tdisCharge占大部分周期时间,充电时间tCharge只占小部分周期时间,这样振荡周期基本只受放电时间tdisCharge的影响,从而实现了振荡频率的稳定。

2 改进的新型RC振荡器

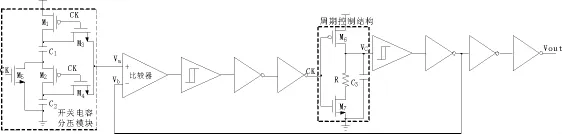

改进后的RC振荡器结构图如图2所示,主要由开关电容分压模块[9]、比较器、施密特触发器、周期控制结构和反相器组成。

图2 改进的RC振荡器Figure 2 Improved RC oscillator

其工作原理如下:当CK为0时,开关管M1、M2导通,等值的电容C1和C2开始通过电源电压储能,此时,M3和M4截止,Va输出低电平,同时开关管M6导通,开始给电容C3充电,VC电压开始上升,经施密特触发器和反相器整型后变成接近电源电压的数值,远远超过Va,这时比较器反转,输出低电平,CK变为高电平,开关管 M3、M4和 M5导通,M1和 M2截止,电容C1和C2并联往外输出定值电压,此时开关管M7导通,电容C3通过电阻R和M7开始放电,VC电压不断降低,经施密特触发器和反相器整型后变成接近0的数值,远低于Va,比较器反转,输出高电平。

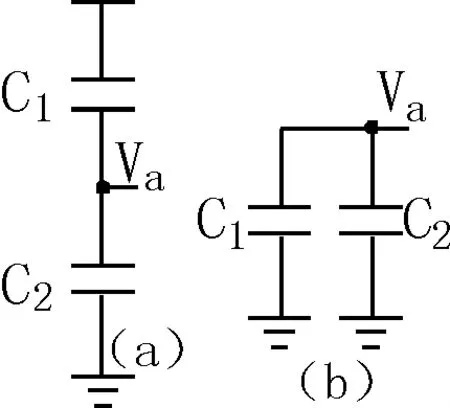

2.1 开关电容分压模块

图3 开关电容分压模块Figure 3 Switched capacitor voltage dividermodule

开关电容分压模块工作状态如图3所示,其中CK 为 0 即低电平时,M1、M2导通,M3、M4和 M5截止,开关电容分压模块可简化为如图3(a)所示,为储能阶段,储存的总能量为Q=2*C*Vdd,C1=C2=C则每个电容储存的能量为QC1=QC2=0.5*C*Vdd。当CK为1即高电平时,M1、M2截止,M3、M4和 M5导通,开关电容分压模块可简化为如图3(b)所示,此时两个电容C1、C2并联向外提供电压,其电压值Va=0.5*Vdd,约为电源电压的一半。

2.2 周期控制结构

周期控制结构见图2,当CK为0即低电平时,M6导通,M7截止,电容开始充电,VC电压开始上升,当超过施密特触发器的触发电平时,施密特触发器翻转输出低电平,经反相器整形后输出接近电源电压的高电平Vb,此时Vb远高于Va,比较器翻转,输出低电平,CK变为高电平,M7导通,M6截止,电容通过电阻R和M7开始放电,这里电阻R的作用一是让VC维持在一个比较大数值,二是延长电容C的放电时间,使传统结构中时钟信号的周期由充电和放电周期组成,变为放电时间占主要,充电时间只占很小的比例。由于充电和放电电流很难完全相等,所以充电和放电时间之和恒定是很困难的,但是保证一个电流一致是容易的。当低于施密特触发器的触发电平时,施密特触发器翻转输出高电平,经反相器整形后输出接近地的电平Vb,此时Vb远于低Va,比较器翻转,输出高电平,CK变为低电平。在该结构中,设流过M6的电流为ICharge,流过M7的电流为IdisCharge,则可得公式(3)

根据电荷守恒和式(3),可得公式(4)

由式(3)和式(4)可得:

即在这种结构中,最后的放电时间只和RC有关。据上面分析,tdisCharge远大于tCharge,我们按最后产生的时钟信号为90%占空比,则时钟信号周期T=tCharge+tdisCharge=1.11 RC。在本设计中,取 C3=1.5 pF,R=30 kΩ。

2.3 比较器和施密特触发器

图4 比较器和施密特触发器结构图Figure 4 Comparator and schmitt flip-flop structure

本设计采用的比较器和施密特触发器结构[10,11]如图4所示,比较器为传统的P输入两级结构。由于工艺制造偏差等因素,比较器会存在失调,由于本设计是低功耗设计,比较器的电流较小,所以比较器会存在延时,同时,延时还容易随着电源电压的变化而变化,失调和延时都会传递到比较器的输出端,进而都会影响时钟信号的频率稳定度,而本设计的结构则可以有效地抑制失调和延时的非理想因素影响。因为如果电路振荡出的CK信号受非理想因素影响,这种非理想性就会在Va上反映出来,同样,这种非理想性也会传递到Vb上,Va、Vb做为比较器输入端,两者的非理想性就会相互抵消,从而减小非理想性的影响。

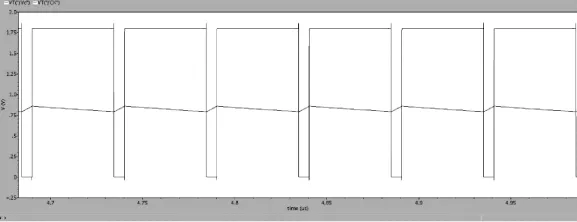

3 仿真验证

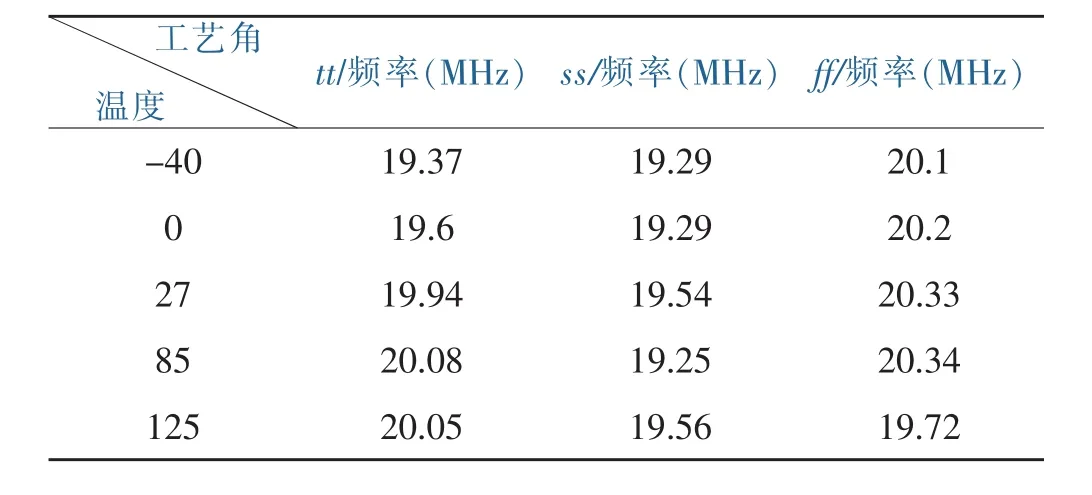

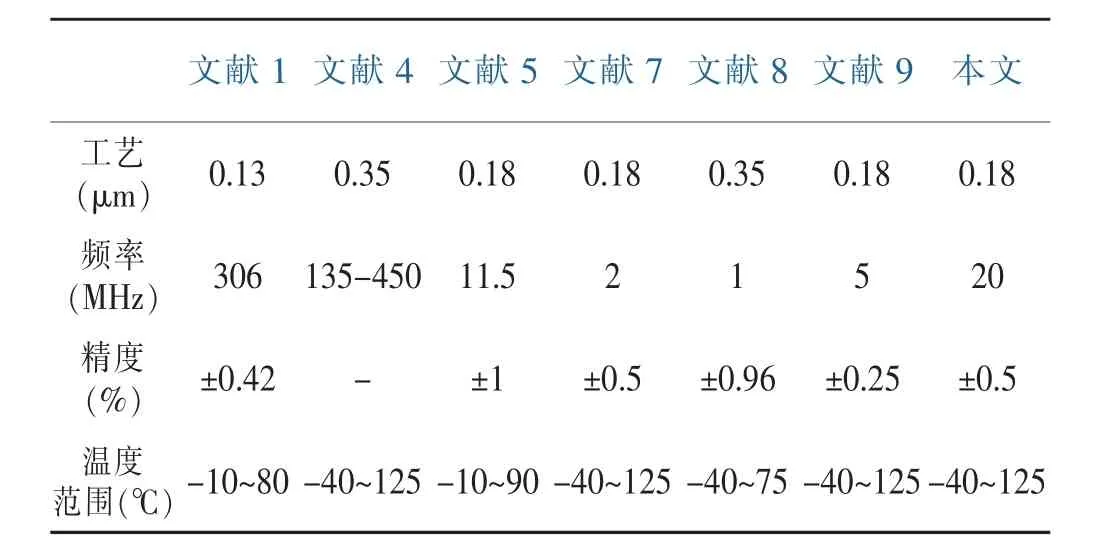

整个电路设计是基于tsmc 0.18μm CMOS 1.8 V工艺实现,其中,C1=C2=0.6 pF,C3=1.5 pF,R=30 kΩ。在Cadence spectre下仿真结果图5-7和表1、2显示:

图5 RC振荡器的Vout输出图Figure 5 Vout output diagram of RC oscillator

图6 周期控制结构Vc输出波形图Figure 6 Outputwaveform of periodic control structure Vc

图7 开关电容分压模块的输出波形图Figure 7 Outputwaveform of switched capacitor voltage dividermodule

Corner仿真结果如下:其中电源电压波动10%,

表1 电路的仿真测试结果Table 1 Circuit simulation test results

表2 与参考文献的比较Table 2 Comparisonswith references