一种GaAs HBT堆叠式功率放大器设计

2019-06-11崔晓婷张金灿

文/崔晓婷 张金灿

功率放大器(PA)作为射频收发信机必要的组成模块,其主要作用为放大射频信号,以便于下级模块较好地接收。为了在射频极端频率下工作,同时以高效率提供适当的功率输出,III-V族化合物半导体(例如:GaAs,InP和GaN)是射频功率放大器(PA)的首选集成电路工艺技术。该技术可提供具有高击穿电压水平的高速器件,以及低损耗无源器件,因此可以获得高功率密度和高效率。

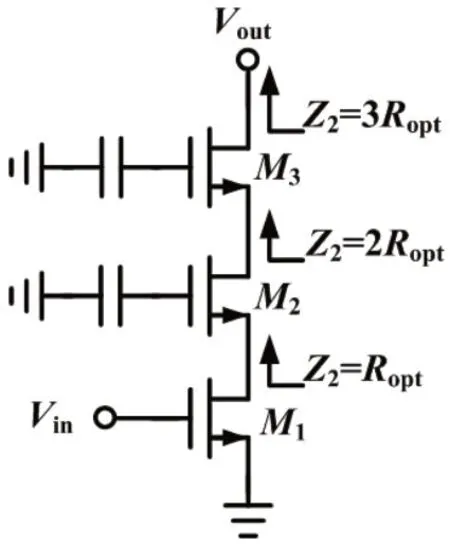

图1:堆叠FET概念

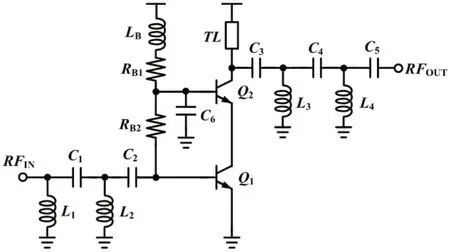

图2:2堆叠双极型放大器

图3:本文设计的PA电路

图4:S21仿真结果

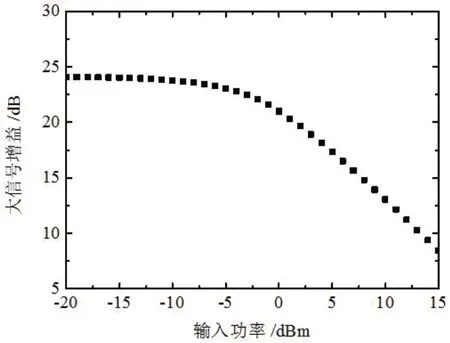

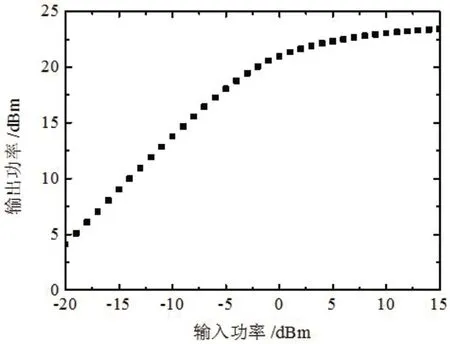

图5:大信号增益仿真结果

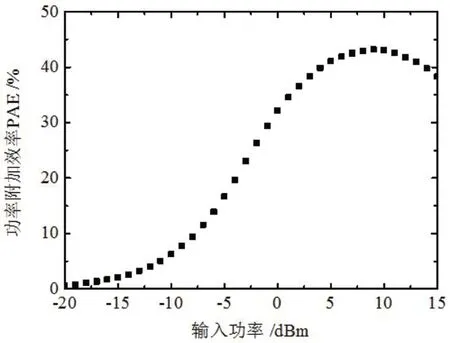

图6:功率附加效率PAE仿真结果

图7:输出功率仿真结果

为了提高PA的输出功率Pout,可以通过将器件串联组合并增加电压的方法来实现,从而代替通过增加电流的方式实现。串联连接最大的一个优点就是,增加了最佳负载,使器件更容易与系统阻抗匹配。堆叠式PA结构便是该技术应用的很好例子。堆叠式PA是基于电压倍增的Pout增强电路。该拓扑已应用实现了具有高输出功率的PA,其中共射晶体管用于驱动共基晶体管。

1 电路设计

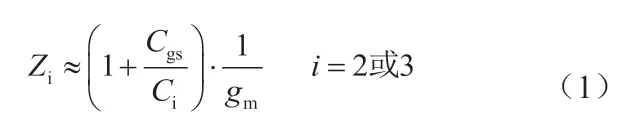

文献[2]中介绍的堆叠FET概念已被广泛应用于较低射频频段PA,以及CMOS射频PA设计中。该结构如图1所示,其输入端口为共源极结构FET的M1,结构中将M1电流馈入串联的晶体管M2和M3,以构成3堆叠式电路结构。C2、C3的引入与晶体管M2、M3的栅-源极间电容Cgs分别控制栅极摆幅的量以及晶体管M1、M2漏极处的阻抗,该结构中晶体管M2和M3漏极处的阻抗可表示为:

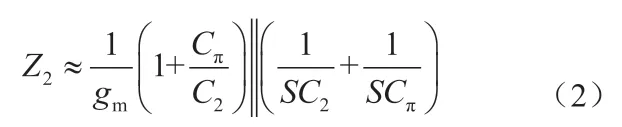

该概念可应用于双极型堆叠式放大器中,如图2所示。在这种情况下,晶体管Q1的集电极上呈现的阻抗计算如下:

其中S=jω。Cπ和gm分别为小信号基极-发射极电容和器件跨导。在工作频率f0远远小于器件截止频率fT时,Z2只剩下实数阻抗,并保持适当的同相运行。因此,堆叠双极型PA与堆叠FET工作的方式类似。

2 仿真结果与讨论

本文设计PA采用堆叠双极型放大器,如图3所示。PA输入阻抗在S11共轭处匹配,以获得最大增益条件。使用负载牵引技术匹配PA输出阻抗以获得最大输出功率Pout。输入和输出匹配网络均使用两个L型网络实现。

基于商用的2 μm GaAs HBT工艺对图3所示的PA电路进行设计,仿真采用ADS 2016软件。图4所示即为仿真得到的小信号S21参数,由图可见,小信号增益在4.3GHz处取得24.6dB的最大增益,并且PA的3dB带宽频段为3.3~5.4 GHz。图5给出了PA在4.3 GHz下,大信号增益的仿真结果,取得了24 dB的大信号增益。功率附加效率PAE仿真结果如图6所示,PAE最大值为43%。图7给出了输出功率的仿真结果,可见,输出功率达到了23.4 dBm的饱和值。

3 结论

本文基于商用的2μm GaAs HBT工艺,设计了一款堆叠式PA。电路仿真采用ADS 2016软件。仿真结果表明,该PA取得了3.3~5.4 GHz的3 dB带宽,在4.3 GHz频率下,取得了24 dB的大信号增益,43%的最大PAE,23.4 dBm的饱和输出功率。