基于FPGA的增益可调微弱信号采集系统设计

2019-06-06高文学孟立凡

高文学,孟立凡

(中北大学,电子测试技术国家重点实验室,仪器科学与动态测试教育部重点实验室,山西太原 030051)

0 引言

随着电子技术的不断发展,新型的数据采集系统正朝着集成化、通用化的方向发展。然而通用化采集系统只能针对普通的采集环境,却无法采集强度相对较弱的信号。针对以上问题,提出了基于FPGA的增益可调微弱信号采集系统。该设计是采用集成化设计,使用多级可调增益的放大电路,实现对微弱信号的多级放大,完成模数转换及信号采集。本系统能够实时采集和存储系统工作过程中的振动、冲击、压力和温度等信息,可广泛应用于车辆安全测试、运动安全器械研发等场合[1]。

1 系统方案设计

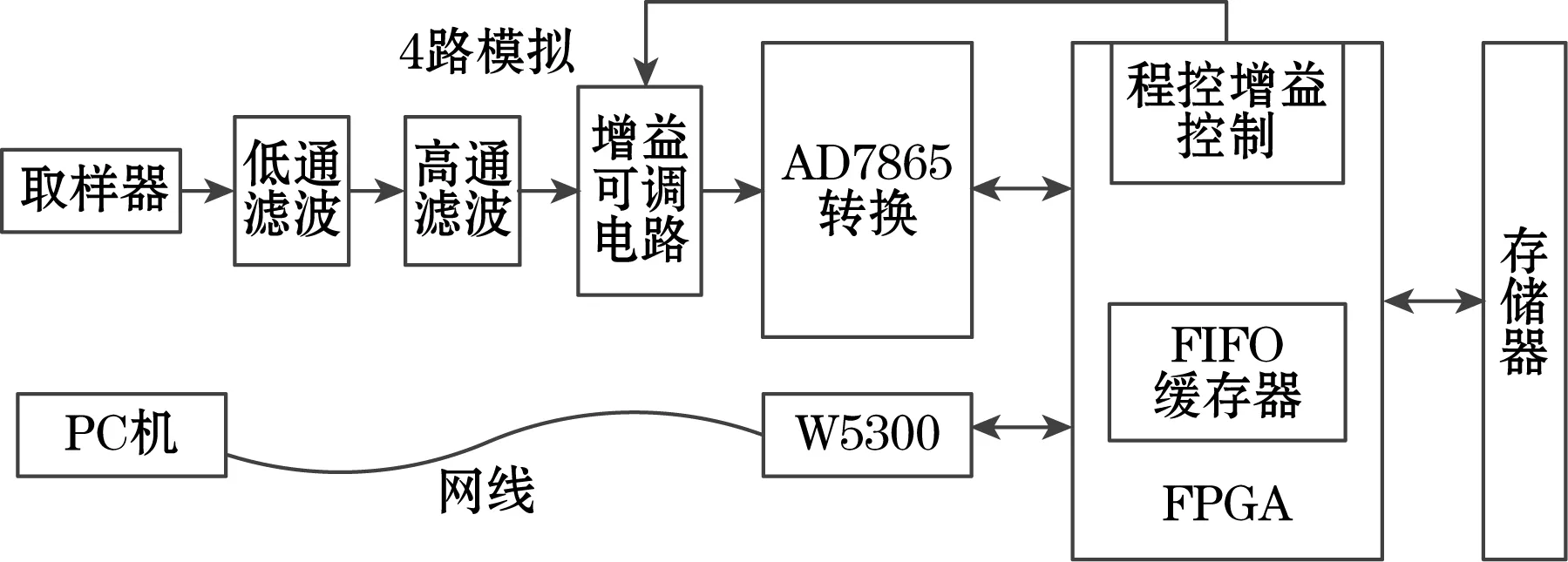

本系统要求采集3路微弱振动信号,1路噪声信号,频率分别为5 kHz和8 kHz,所以要求采样频率为230 kHz。根据以上需求本系统选取AD7865为A/D转换芯片,以FPGA为控制核心,以模拟开关DG611DY和集成运放器OP37G为增益可调放大电路。本系统工作流程为采样器将高频信号转换为低频信号,通过低通滤波过滤掉噪声,高通滤波过滤掉谐波,输入4通道增益可调放大电路,通过PC机下发指令至FPGA中,由FPGA控制模拟开关通断,使之组合10种放大倍率,最后在FPGA的控制下由ADC芯片将放大信号采集存储在Flash里。系统总体框图如图1所示。

图1 整体结构框图

2 系统硬件设计

2.1 增益可调电路设计

增益可调部分由4通道增益可调放大电路组成,每一通道由3个集成运算放大器OP37G和2个模拟开关DG611DY共同组成。输入信号通过电压跟随器U1进入模拟开关U2,通过U2与U3组成的第一级增益可调放大电路进行第一次放大倍率选择,然后将此放大信号输入U3与U4组成的第二级增益可调放大电路中进行第二次放大倍率选择,最后经过两级放大的信号通过电压跟随器输入至U5中,通过U5将增益可调放大电路的输出信号输入至ADC中,进行信号转换。增益可调电路如图2所示。

图2 增益可调电路结构图

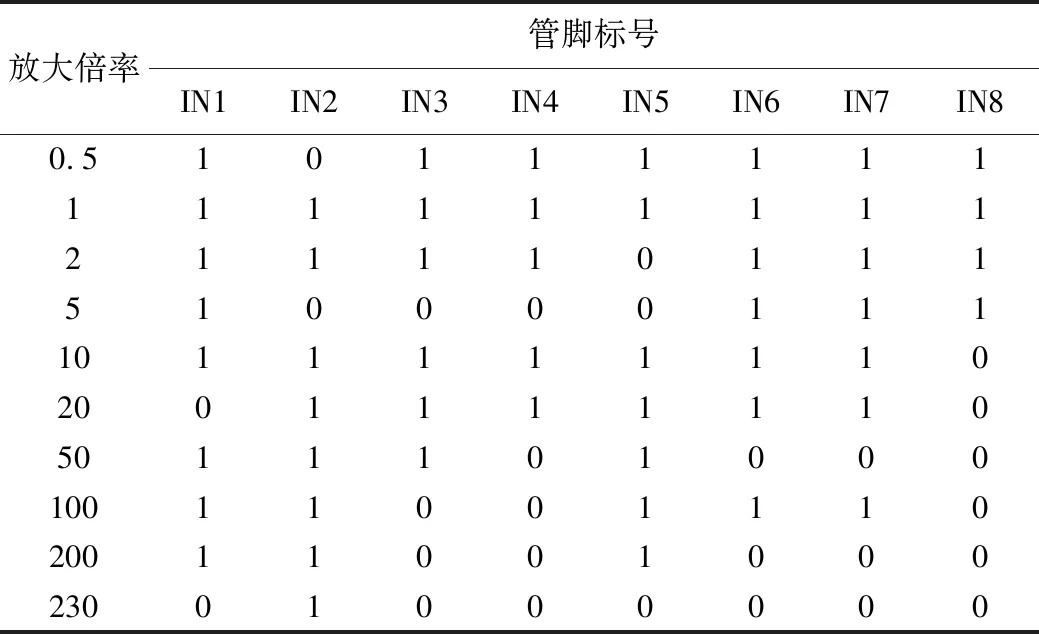

本系统的模拟开关选用DG611DY芯片,根据产品手册,当IN管脚的输入电压≤1V时为逻辑“0”,当IN管脚的输入电压≥4V时为逻辑“1”。增益放大控制如表1所示。

表1 增益放大控制

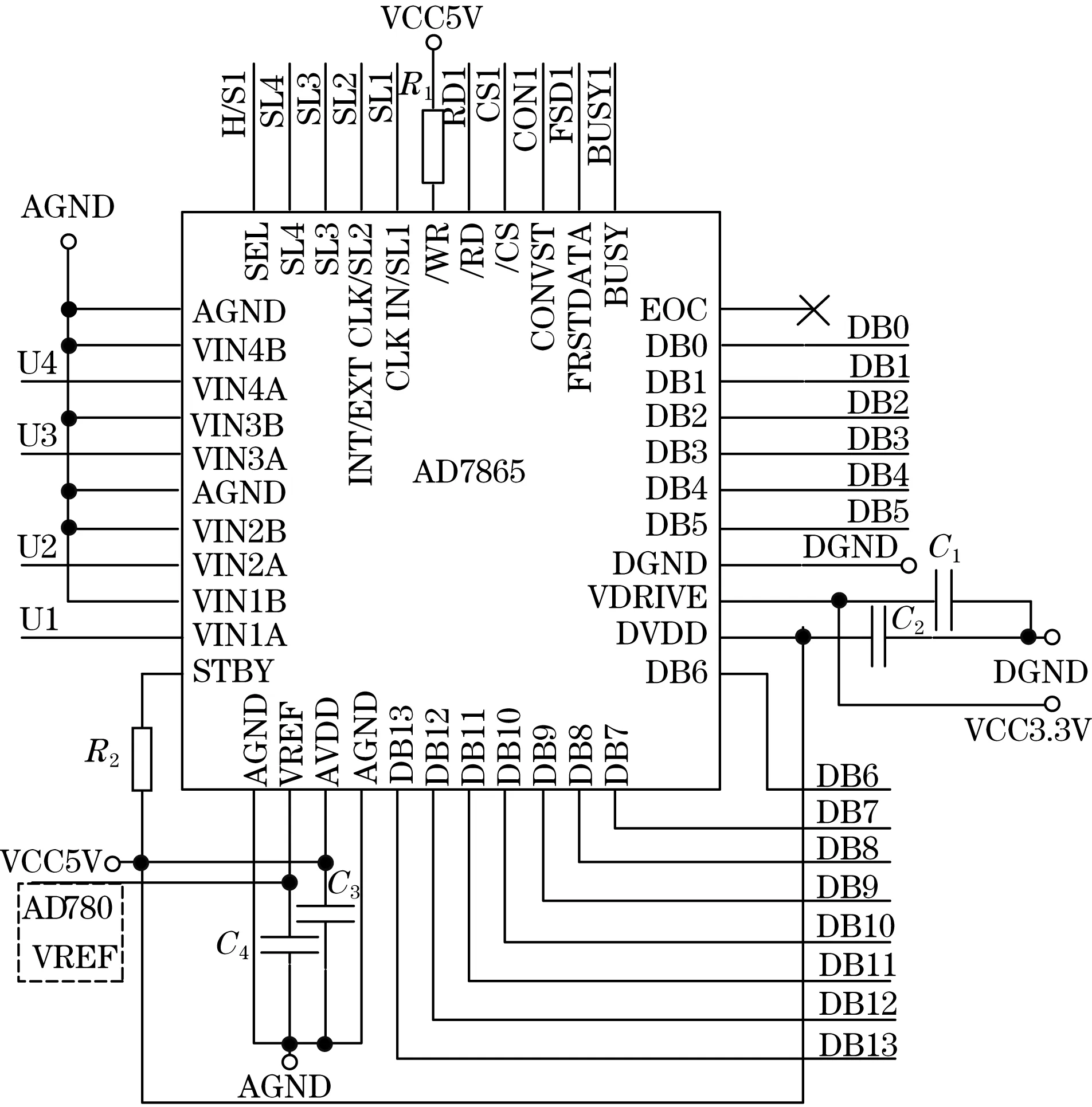

2.2 模数转换硬件电路设计

本系统采用高精度芯片AD7865-1作为转换芯片,该芯片的转换精度较高,具有快速的转换频率以及较多的转换通道,能够实现采样频率的灵活配置。电压输入范围选择±10 V,此时须将管脚VINXB接地,输入电压加在VINXA上。

VIN1A~VIN4A为AD7865-1的四个通道的输入端, AD7865-1芯片的3处供电部分分别为:(1)模拟部分AVDD采用+5 V供电,AGND接模拟地;(2)数字部分是与FPGA连接,DVDD接+3.3 V,DGND接数字地;(3)参考电压:VREF=2.5 V,由于参考电压的稳定性关系到芯片采集数据的精度,以高精度的稳压芯片AD780产生+2.5 V电压作为参考电压输入。本系统中将STBY管脚拉高,ADC即工作在normal模式下。配置SEL管脚选择硬件通道选择方式。同时,/WR写入管脚无效,做拉高处理。DB0~DB13为数据输出管脚,其他控制管脚如/RD、BUSY、FRSTDATA等均与数据输出管脚连接至FPGA,由FPGA给出控制信号[2]。管脚连接如图3所示。

图3 AD7865电路设计图

3 系统逻辑控制

本系统前端采集电路逻辑设计的主要功能包括对传感器输出信号的增益可调、A/D转换等部分,采集电路与控制电路在整个系统工作过程中密切配合。

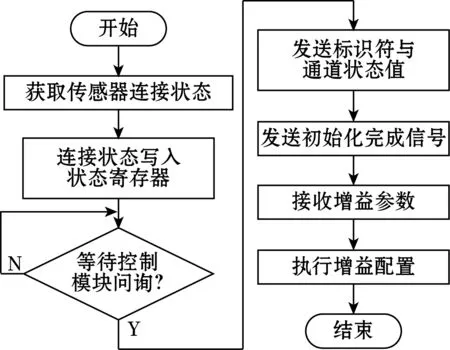

3.1 增益逻辑控制

系统上电工作后,首先通过判别电路判断4个采集通道的传感器连接状态,并将通道连接状态标识符写入状态寄存器中,待控制模块发送问询命令后,采集模块将状态标识符等信息编帧发送给控制模块,完成初始化操作;获取对前端采集电路进行配置的增益参数,采集电路的采样率参数等;待收到控制模块的触发采集指令后,采集模块开始采集数据并将数据保存在片上存储器中[3];待收到数据读取请求后开始向上位机回传数据。

本系统中,完整的指令帧结构由指令标识符、通道地址和指令正文构成。上位机将指令帧发送到FPGA中,首先根据标识符判断指令类型,设计规定增益指令的标识符为 01H[4];通道地址由2位组成,代表4个通道编号[5],各通道根据指令正文获取 4位增益控制参数,共16种增益倍率,本设计用到其中10种;增益可调采集系统获取增益参数后,控制由DG611DY与OP37G组成的增益可调电路。增益逻辑控制的工作流程如图4所示。

图4 增益逻辑控制工作流程图

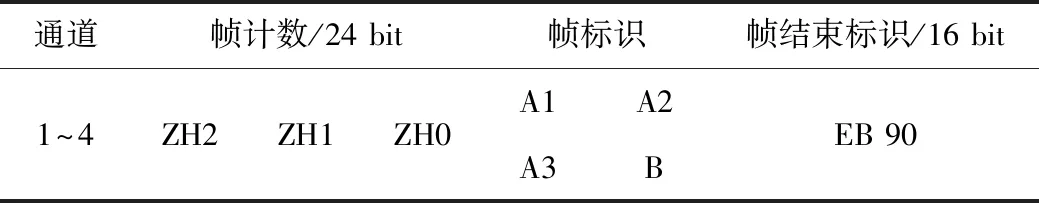

3.2 混合编帧格式

本系统对4路通道数据进行采样,分别为3路微弱振动信号(A1~A3),单通道采样率为5 kHz,1路噪声信号(B1),单通道采样率为8 kHz,数据的总采样率为230 kHz。为了使信号能够达到均匀采样,必须要保证一帧数据中同一信号采样点的时间间隔均匀,因此必须要对模拟信号设计一种均匀编帧结构[6]。每一帧的尾部添加上帧结束计数与帧标志信号,以便于检测出在数据采集的过程中有无误帧、丢帧的情况。初步设定帧结构的列数为47列。构成的数据帧为5×47的矩阵,最终得到的数据编帧结构如表2所示,其中EB和90为帧结束标志位,共16 bit,ZH2~ZH0为帧计数位,共24 bit。表中每个采样点均以1 kHz进行采样,其中帧计数位和帧标志位不占用采样率,总采样频率仍为230 kHz。其中数据编码格式如表3所示。

表2 数据编帧结构

表3 各路数据编码格式

3.3 模数转换逻辑控制

本系统中采用硬件通道选择方式,即在采样-转换过程中芯片自动进行通道切换。

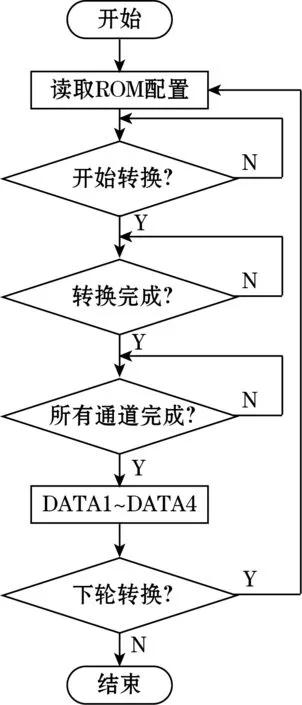

模数转换开始是由/CONVST的电平变化为起始的,/CONVST的一个上升沿代表转换过程的开始,这个上升沿还同时将AD7865-1内部的4个采样保持器固定在“保持”状态,第一个数据通道的数据即可被读出。每个数据通道的数据转换时间为2.4 μs,EOC信号的一个下降沿标志每个通道转换的完成,BUSY信号的下降沿则标志着所有通数据道转换的完成[7]。数据采集转换模块的软件设计流程如图5所示。

图5 模数转换工作流程图

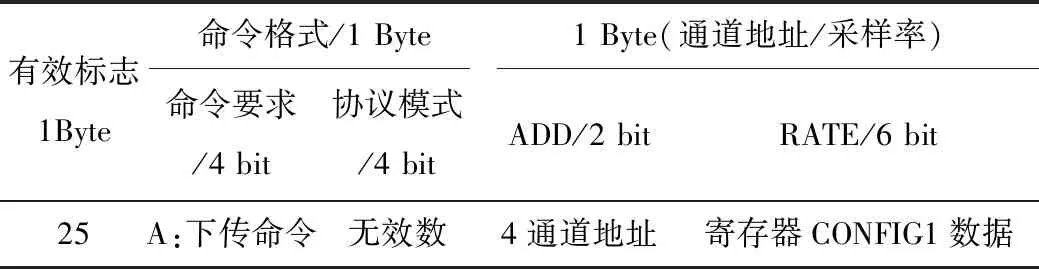

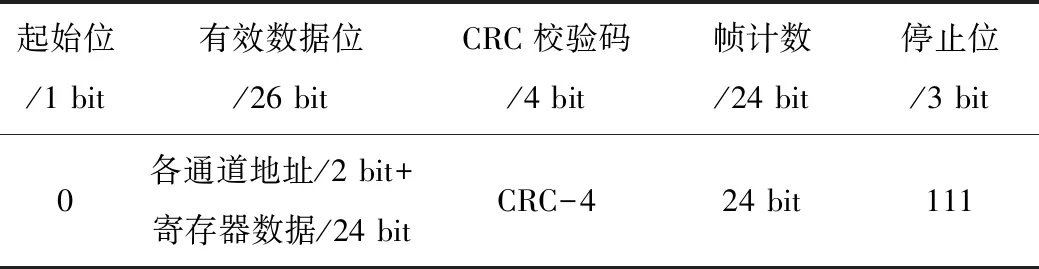

3.3.1 命令包与数据包格式

上位机下发的命令包与上传的数据包大小不同,所以其协议也不一样[8]。FPGA接收到下发的命令后,将命令进行解析,若命令有效标志为“25”,FPGA继续识别命令要求是否为“A”。2位ADD为各通道的地址位,最多可设置地址为4个。若命令有效标志为“25”且命令要求是“5”,此时FPGA转为接收状态,等待接收数据重组后上传给上位机。FPGA回传的模数转换数据每组数据有58 bit,含1 bit起始位、26 bit有效数据(2 bit地址位,24 bit数据位)、4 bit校验码、24 bit帧计数及3 bit停止位[9]。具体下发和回传数据包格式如表4和表5所示。

表4 下发命令包格式

表5 回传数据包格式

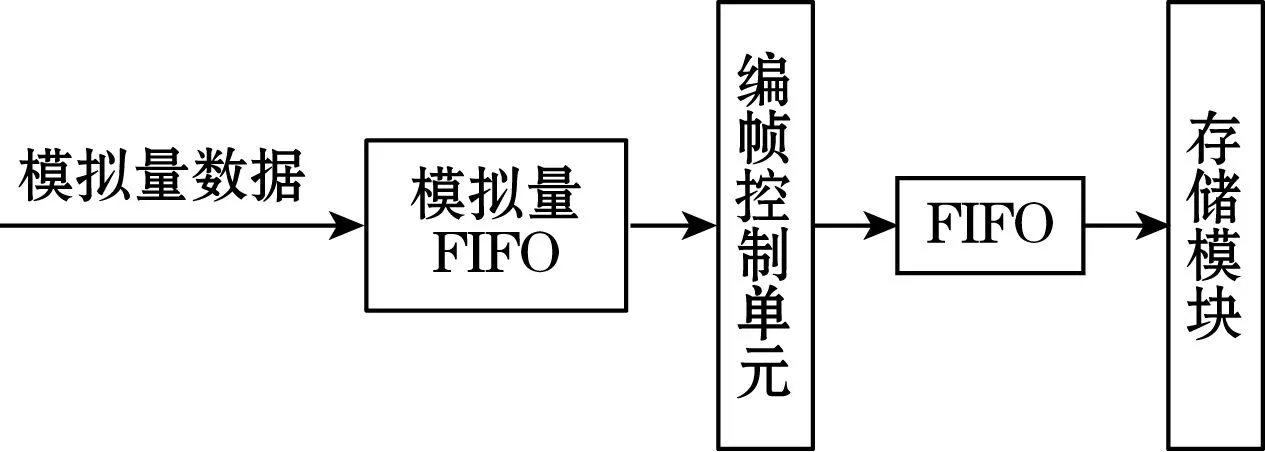

3.3.2 FIFO管理与数据编帧设计

本系统中3路50 kHz采样率的微弱振动信号和1路80 kHz采样率的噪声信号,这4路信号在转换位数为14 bit的情况下,在组帧进入Flash存储前,由于Flash芯片正处于边擦边写的无效块检测和块擦除阶段,其中典型的页读操作时间tR为35 μs,块擦除操作时间tBERS为1.5 ms,该段时间数据无法存储,为避免造成数据丢失,所以需要缓存这段时间传过来的数据。本系统采取在FPGA中开辟FIFO缓存数据的方法,所需空间为

(50×3+80)Ksps×14 bit×(35 μs×2+1.5 ms)=0.632 KB

所以选取1 KB FIFO足以满足缓存需求。数据流缓存示意图如图6所示。

图6 数据流缓存示意图

4 结果分析

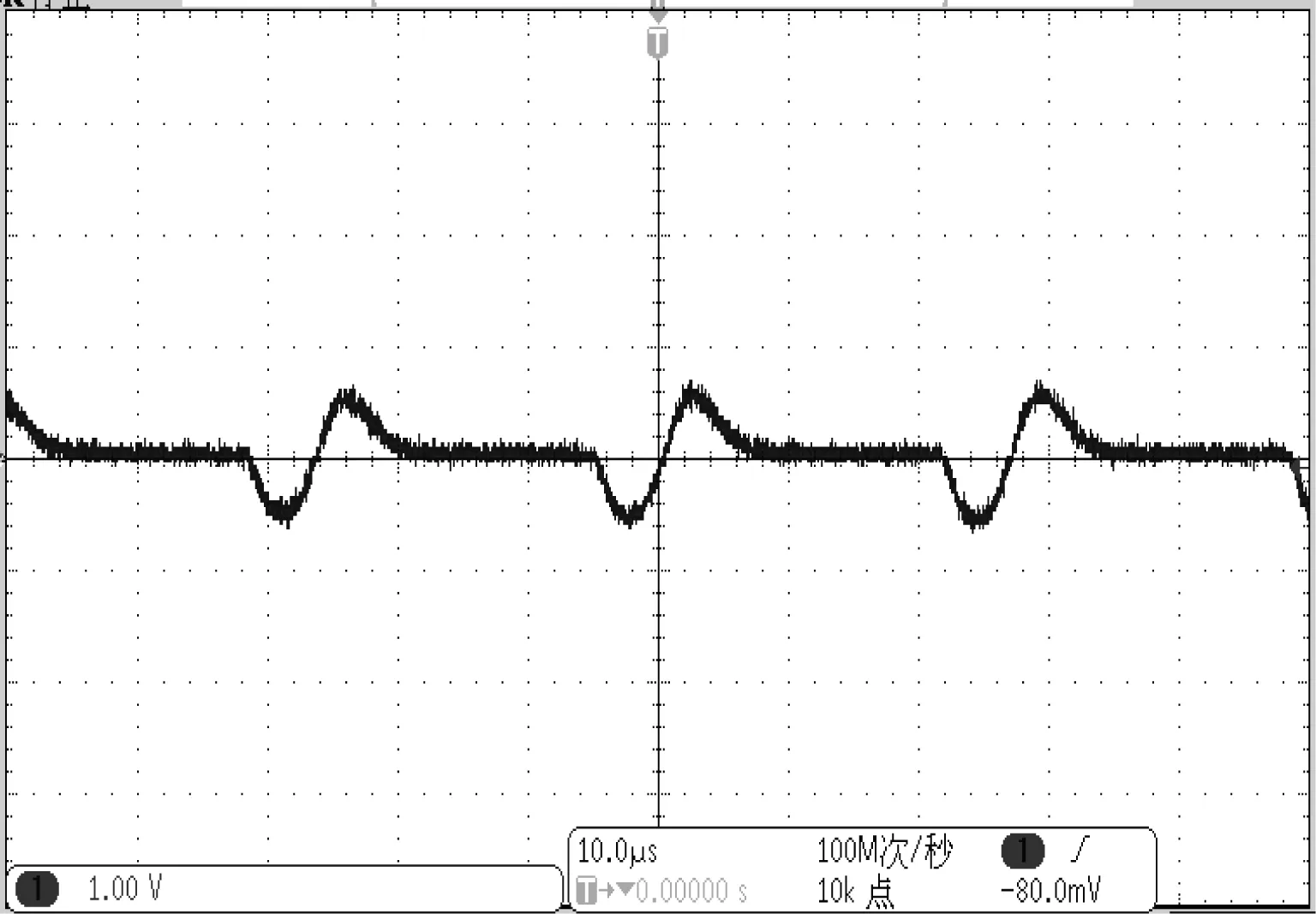

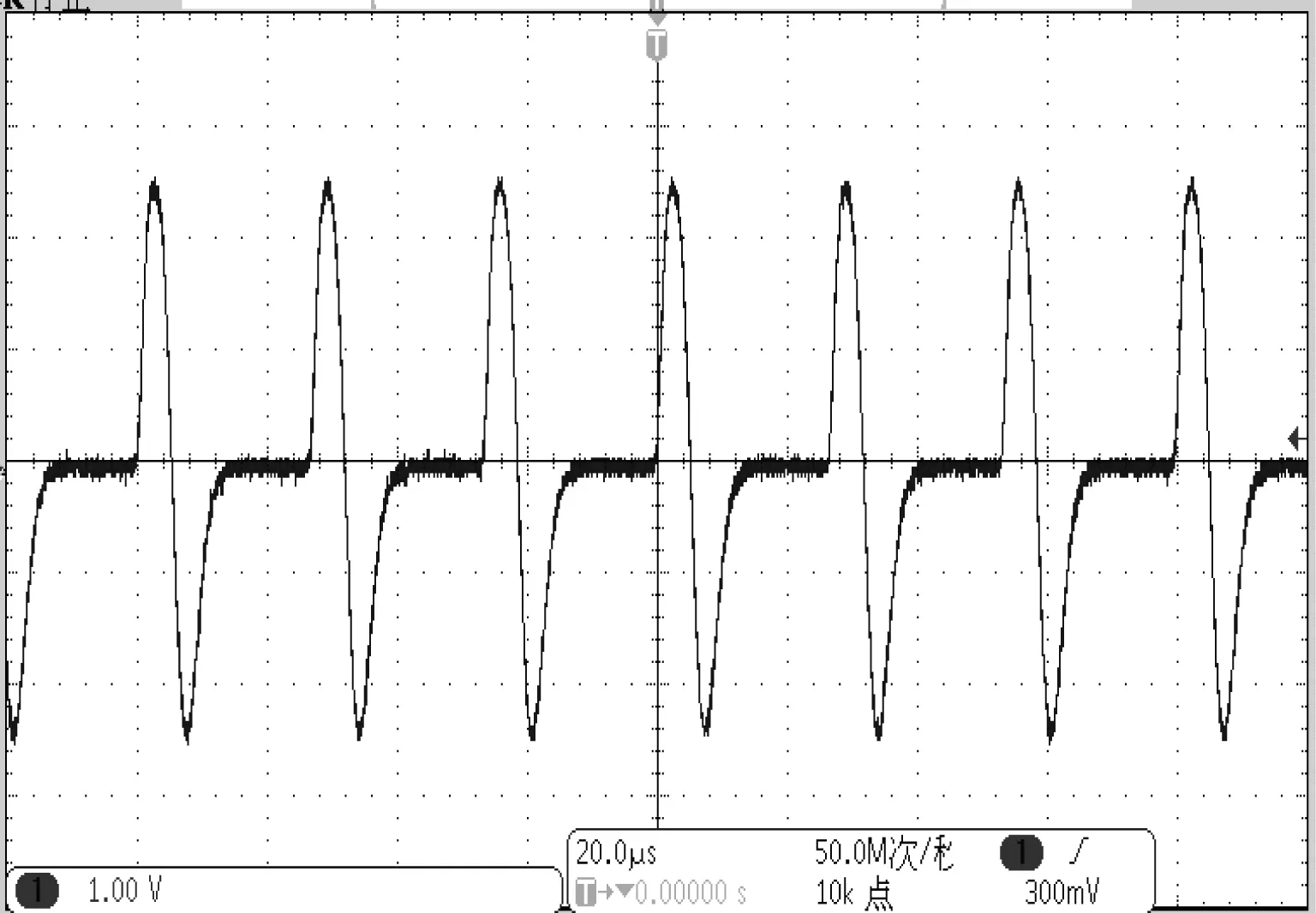

4.1 增益可调放大倍率

通过上位机选择增益倍率,下发命令到FPGA,FPGA经过解析进而控制开关芯片DG611DY的IN1~IN8引脚,实现了10种不同的增益倍率。为了验证系统的增益放大功能,选择1 V信号为原始输入信号,以此验证0.5倍增益放大功能;同理选择25 mV验证100倍增益放大功能。图7和图8分别为0.5倍和100倍实测图。

图7 0.5倍实测图

图8 100倍实测图

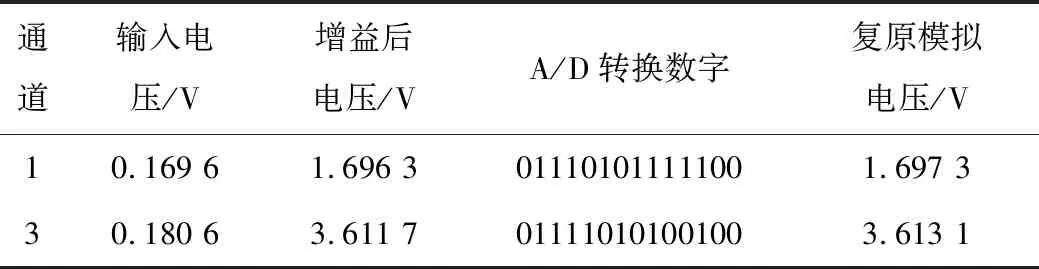

4.2 A/D转换精度分析

从4路模拟信号通道中选取微弱信号1与3通道的信号作为数据采集效果分析。AD7865-1的工作电压为±10 V,根据芯片手册的计算公式1 LSB=FSR/16 384,本设计中FSR为20 V,由此计算得1LSB为1.22 mV。A/D转换后输出16位数字量,其中D15、D14为通道标识位,因此取D13~D0进行计算,每路从采集结果选20个数据取平均数代入计算。各通道转换结果如表6所示。

表6 转换结果

通道1对输入信号增益为10倍的采样精度为(1.697 3-0.169 6×10)/(0.169 6×10)=0.077%

通道3对输入信号增益为20倍的采样精度为

(3.613 1-0.180 6×20)/(0.180 6×20)=0.030%

各通道精度均达到了0.1%的设计精度需求。

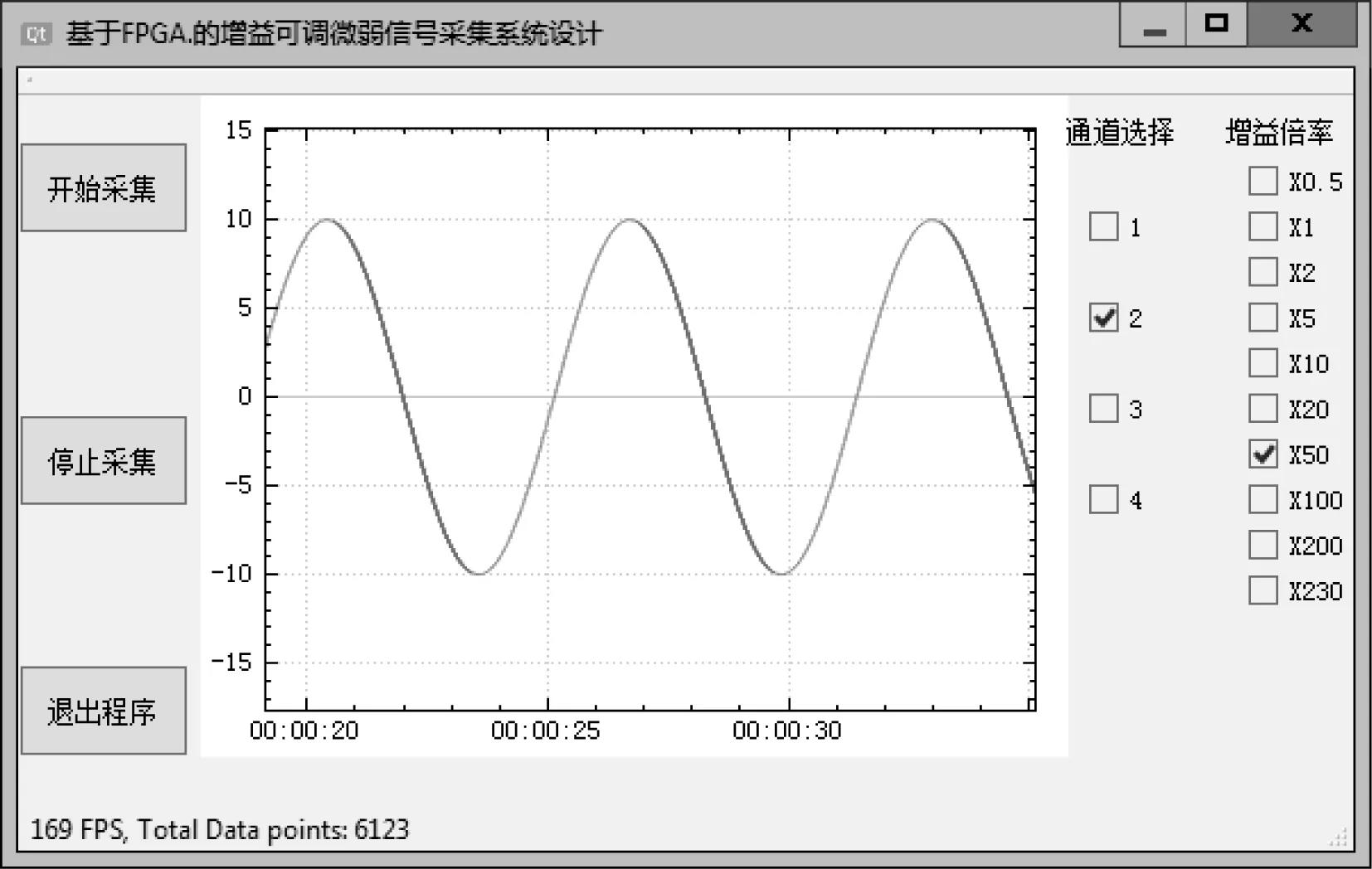

4.3 采集信号复原

储存在Flash中的数据通过W5300网线与PC机连接,使用幅值范围为±0.2V的正弦波去测试本系统的整体性能,通过上位机读取采集到的数据并且显示出波形。点击开始采集按钮,显示结果如图9所示。图9为通道2微弱振动信号在增益50倍情况下采集并恢复得到的结果。由结果看出通道2波形没有出现畸形与杂波,说明本系统的增益、采集与存储工作平稳有效,满足多通道模拟信号的采集要求。

图9 增益放大后微弱信号单通道采集效果图

5 结束语

本系统利用FPGA为控制芯片,AD7865作为模数转换芯片设计了增益可调的采集系统,通过上位机发送控制命令,可以精准的控制增益倍率,完成3路微弱振动信号及1路噪声信号的采集,经测试精度均在0.1%以内。适用于多种微弱信号的调理、放大、采集,简化了前段调理电路设计的复杂性。