用于脉冲叠加器的LLC谐振充电源的研究

2019-06-06黄超林饶俊峰

黄超林,姜 松,饶俊峰,李 孜

(上海理工大学 光电与计算机工程学院,上海 200093)

脉冲功率技术被广泛应用于军事、医疗、环保等领域,如雷达发射机[1]、脉冲激光焊[2]、污水处理[3]、食品杀菌[4]等。为适应不同领域对脉冲电源的要求,脉冲电源技术发展出多种结构来产生脉冲,如磁压缩脉冲[5]、脉冲形成网络[6]、脉冲变压器[7]、Marx发生器[8-9]等。脉冲叠加器[10]就是其中的一种用来产生脉冲的结构,相比于传统Marx发生器它具有以下优点:充电源与放电回路有电气隔离,充电与放电回路互不干扰,可同时进行;更易实现调制双极性脉冲波形等。这些优点与脉冲叠加器的串联磁芯充电结构密切相关。设计充电源时,通过提高变换器的开关频率减小充电结构中磁芯的体积,可使整个系统结构紧凑。

文献[11]设计的脉冲叠加器的充电源采用串联谐振充电源,主要优点是其结构较为简单,具有恒流、恒谐振频率,且变换器选择工作于谐振电流断续模式时,可实现开关管的零电流关断。但当变换器工作于谐振电流连续模式时,在相同的特征阻抗情况下,平均充电电流小,相对的充电时间较长。针对以上充电问题,从串联谐振变换器发展起来的LLC变换器既有抗负载短路也有一定抗负载开路的性能,且相较于串联谐振充电方式,LLC变换器工作于谐振电流连续模式,通过调频控制[12]可实现恒流充电,实现开关管的零电压开通。本文首先讨论了脉冲叠加器充电结构特点的影响及解决方法,通过对简化后的脉冲叠加器LLC谐振充电电源用基波近似法进行建模,合理设计变换器参数,实现变换器工作频率100 kHz时且有软开关性能,根据放电负载选取合适大小的储能电容。通过实验验证,用于脉冲叠加器的LLC充电电源能可靠稳定地工作,输出脉冲电压幅值8 kV,重复频率10 kHz。

1 脉冲叠加器充电结构

传统Marx发生器有两种工作模式。充电模式:开关管关断,充电电源给储能电容充电,负载电阻上电压为零;放电模式:开关管闭合,储能电容串联对负载放电,在电阻负载上得到脉冲电压。但脉冲叠加器由于变压器的隔离作用,在放电时充电源也可以一直工作。充电源与放电源相对独立,当输出短脉冲时由于放电短,在放电模式时充电对储能电容上电压幅值影响可以忽略。输出长脉冲,相较Marx发生器脉冲的顶降幅值更小。

脉冲叠加器结构给储能电容充电的特点是每一级都有一个磁环变压器,串联多级磁芯同时充电。这种充电方式由于每级磁环变压器的漏感、储能电容的差异等因素[13]的影响,导致充电后每级储能电容的电压差异。

串联磁芯充电结构:由一条母线串联穿过磁环,每个变压器一次侧是一匝线圈。变压器励磁电感由下列公式决定

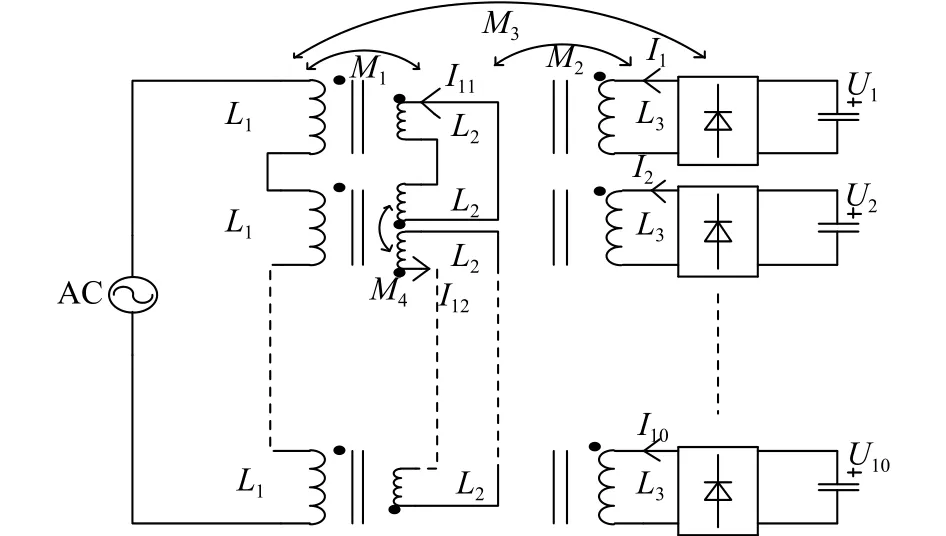

式中:ui为磁芯的初始磁导率;S为磁芯的截面积;N为绕线线圈的匝数;l为磁芯的平均磁路长度。由于每个磁环是独立的,磁芯相对磁导率存在差异,由式(1)可知,变压器原边感抗的不同,也会导致串联的变压器原边分压不同,使储能电容的电压有差异。为避免电容上电压差异过大,采取以下简便方法挑选磁环:测量每一个磁环绕相同圈数后的电感量,选取电感量相差不大的磁环用于实验。为使充电电压更加一致,可采取如图1所示的磁平衡结构,解决由每个变压器漏感与每级储能电容的差异导致的变压器二次侧充电电压幅值的不同。图中:AC为谐振充电源;L1为每级变压器的原边电感;L2为增加在每级变压器上的平衡绕组,需与另一变压器上的平衡绕组并联才能发挥作用;L3为副边电感;U1~U10为每级充电电容上的电压;I1~I10为变压器的副边充电电流;I11~I12为平衡绕组中的电流;M1~M4为变压器对应两绕组间的互感。

图1 简化磁平衡原理图Fig.1 Schematic diagram of magnetic balance theory

磁平衡结构原理的验证以三级叠加器充电为例。其电容电压可用下式表示

式中:U1~U3为每级充电电容上的电压;I0为原边充电电流。

以一组平衡线圈为例,其反并联线圈两端的电压相等,同时为简化算式,假设变压器的耦合系数为1,上述关系可表示为以下等式

因此,电容上电压差异可以表述为下式

另一组平衡线圈类似,可见通过一组反并联的平衡绕组消除了电容上的电压差异。

2 LLC谐振充电电路

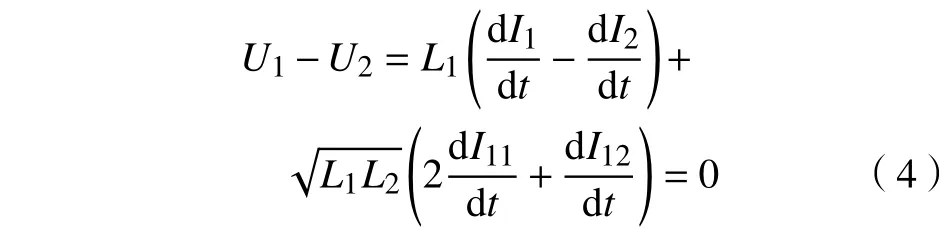

整体的系统结构如图2所示,直流源DC由220 V输入交流调压器后整流滤波得到;S1~S4为开关管;RB1~RB10为全桥整流器;C1~C10为脉冲叠加器上的储能电容;R1,R2为采样电阻;R3为脉冲叠加器的负载电阻;Lr为谐振电感,Cr为谐振电容,Lm为励磁电感。直流源输入LLC谐振变换器,通过高变比磁环变压器后整流滤波输出到脉冲叠加器。

图2 全桥LLC谐振充电脉冲叠加器系统结构图Fig.2 Structure of the full bridge LLC resonant charging pulse adder system

前级采用工作频率在谐振频率附近的LLC谐振电路,谐振电流连续,实现变换器开关管(MOS管)的零电压开通。虽然会有关断损耗,但可以通过在开关管两端并联缓冲电容实现软关断,提高充电效率。现场可编辑门电路(FPGA)输出时序信号,控制变换器与脉冲叠加器的放电开关管(IGBT)的控制信号。集成芯片IR2110驱动变换器MOS管,同步隔离驱动电路用于驱动脉冲叠加器中的IGBT,输出采样电阻反馈信号到控制电路实现电路的过压保护。

2.1 LLC充电电路建模

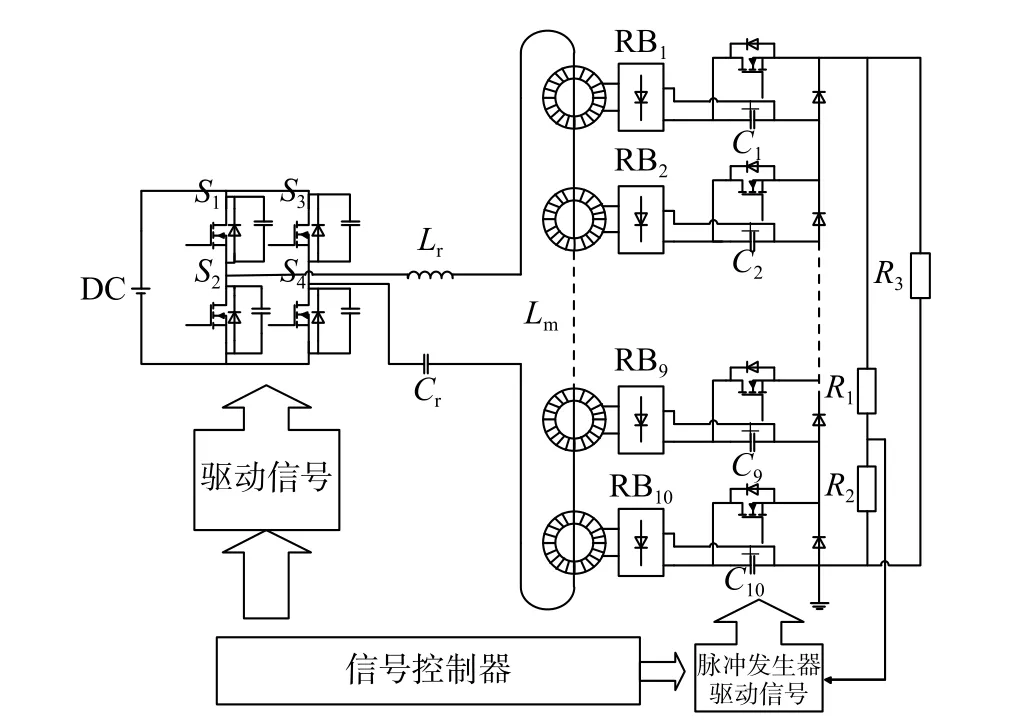

为便于建模分析,假设每级磁环都是理想变压器,那么每级电容上充电过程、充电电压幅值都相同。充电时变压器二次侧储能电容是串联的形式,等效成一个储能电容,将串联多级磁环变压器看作一个变压器进行建模分析。LLC谐振充电电路的负载是储能电容,电容在充电的过程中可以等效为一个可变电阻。分析变换器特性时,在一个开关周期内,电容上电压变化非常小,可以近似地认为其保持不变。由此,在每一个开关周期内,将可变电阻看作固定电阻。电路图中可将单个的储能电容等效为滤波电容与电阻并联的情形,将每一个开关周期都看成相对的稳态,滤波电容在图中仅表示将整流桥输出的电压幅值维持稳定,其等效电路图如图3所示。图中:n为变压器变比;Ro为储能电容的等效负载;Uin为输入电压;UN1为输入电压的基波分量;ir为谐振电流基波分量;iLm为励磁电流;ip为变压器原边电流;Up为原边电压;Uo为负载电压;Re为原边等效交流阻抗;Ro为负载阻抗;Zin为输入阻抗。

图3 全桥LLC串联谐振基波等效电路图Fig.3 Equivalent circuit for the LLC full bridge series resonant fundamental

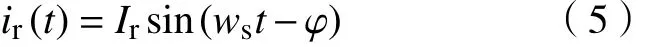

假设整个变换器的开关为无损耗器件,无源元件为线性元件。假定电感电流是正弦信号,只含基波分量,则谐振电流的基波分量为

逆变侧电压基波分量为

等效交流负载为

式中:Ir为谐振电流最大值;ir(t)是谐振电流基波分量;uN(t)是逆变侧电压基波分量;ws为开关管开关的角频率;φ为初始相位角。

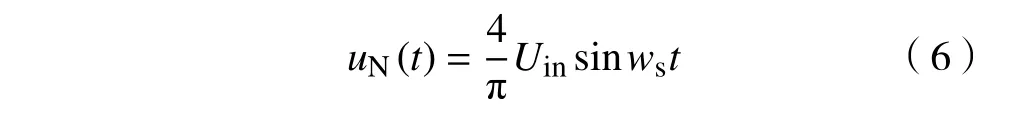

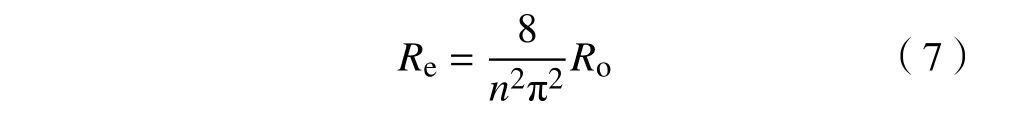

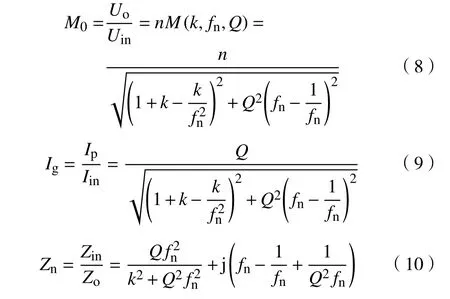

式(5)~(7)结合LLC谐振充电电路的基波等效图3得出电压增益M0与电流增益Ig及关于特征阻抗的归一化阻抗Zn,将谐振变量对其影响归结为k和Q对增益曲线的影响。

式中: 为电感系数比;fr为谐振频率;为归一化频率,fs为开关频率;Zo为特征阻抗; 为品质因素;Iin为输入电流;Ip为变压器原边电流;M0为电压增益;Ig为电流增益;Zn为归一化阻抗。

结合变换器的归一化输入阻抗表达式,当Zn的虚部为零时,即可得出变换器工作于容性感性状态临界品质因素

k=Lr/Lmfn=fs/fr

Q=Zo/Ro

联立式(8)和式(11)可得到阻抗呈感性情况下,谐振变换器输出电压增益表达式为

式中:Qg为临界品质因数;Mg为临界输出电压增益。

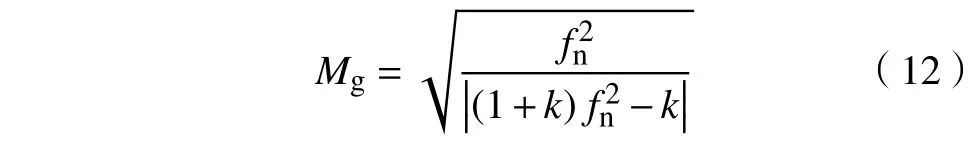

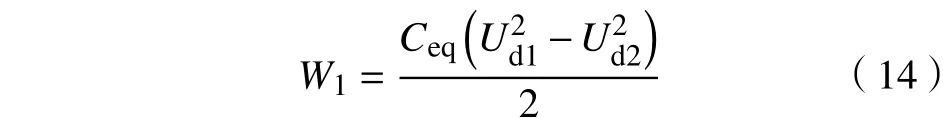

图4纵坐标表示电压增益M,横坐标表示归一化频率fn。其中,图4(a)中的k为0.2时显示黑色粗实线Mg为容性与感性的分界线。Mg上方区间Ⅰ为工作频率大于谐振频率的感性区,可实现开关管的零电压开通(ZVS),但整流二极管零电流关断(ZCS)丢失;工作频率小于谐振频率为区间Ⅱ感性区,能同时实现开关管的ZVS与整流管的ZCS;区间Ⅲ为容性区,可实现开关管的ZCS,但在开关管两端易形成很大的电压尖峰,易造成器件的过压击穿。图4(b)显示当Q为0.2,小于谐振频率时,k值越大增益曲线增益越高,且越靠近谐振频率点,高于谐振频率点后直流电压增益不超过1且缓慢降低。当频率趋近无限大时最小的电压增益为1/(1+k),这表明输入电压一定的情况下,空载输出电压的极限情况。变换器工作在低于谐振频率点时,只有在Q值满足一定条件的情况下,变换器工作状态处于区间Ⅱ。在给电容的充电过程中Q变化很大,无法满足区间Ⅱ的工作条件。相反,在大于谐振频率点区间,变换器都工作于区间Ⅰ。综上考虑选择感性区域的区间Ⅰ。

图4 不同的Q与k值对变换器直流增益曲线变化Fig.4 DC gain curves with different Q or k values of the converter

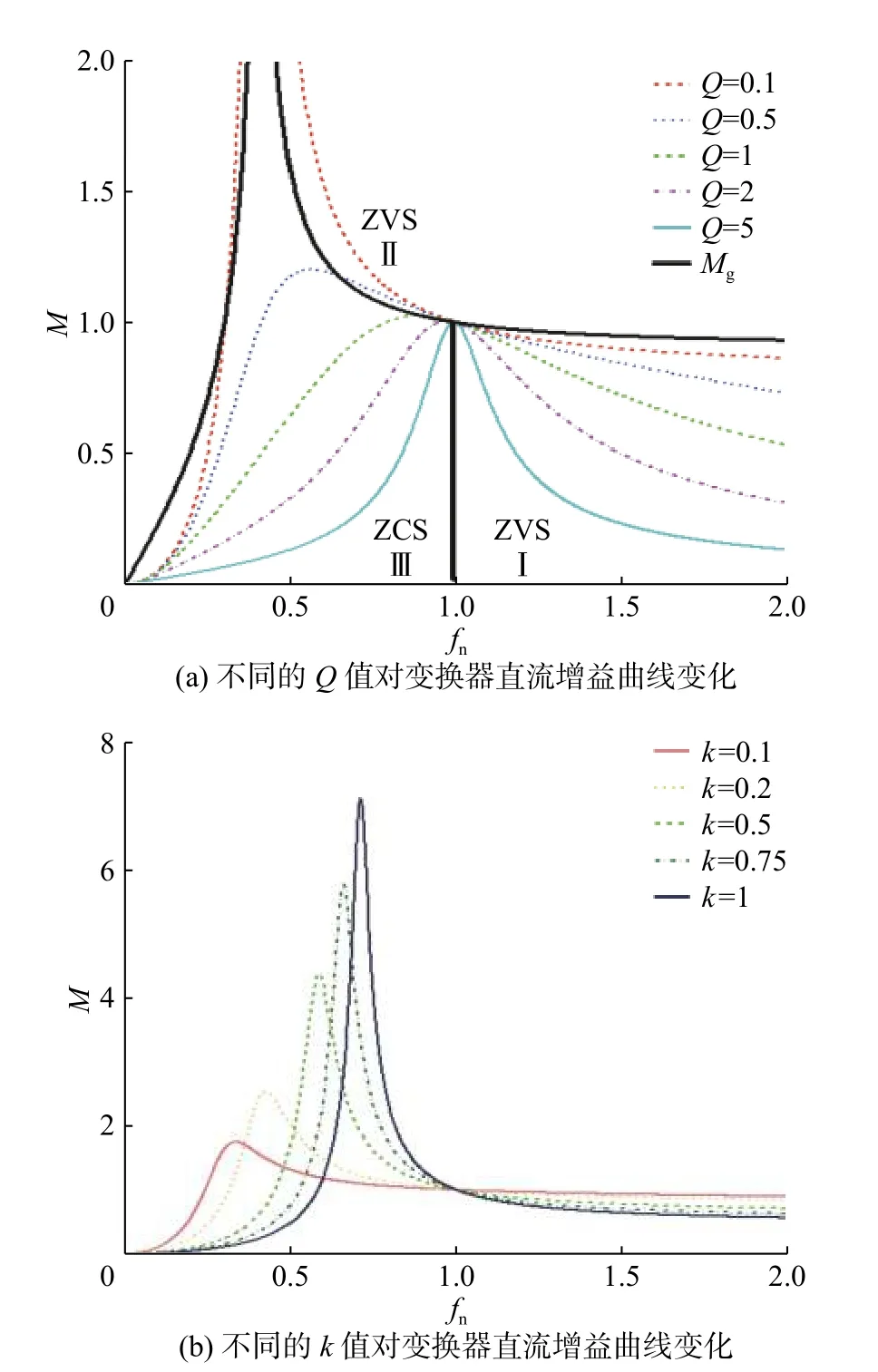

充电电流影响着电容的充电时间及器件的选择。图5纵坐标为电流增益Ig,横坐标为归一化频率fn。k=0.2时由式(9)得到电流增益Ig与归一化频率fn在不同Q值下的关系。由图5知,当谐振参数确定后,负载的改变引起Q从大到小的变化。Q越大,电流最大增益值越大,且最大增益处开关频率越接近于谐振频率点处。当fs大于fr时,fs越大,充电电流越低,因此提出了通过调节频率实现调节充电电流的方法:以较高的开关频率充电,限制电容的充电电流,随后逐渐减小fs,实现以较为稳定的电流给电容充电。根据电流增益的变化选取合适的开关管工作频率区间,最小开关频率为谐振频率。Q=500,fn>1.2时,电流增益Ig变大的幅度明显减小,且几乎不变,故不需要选择过大的开关频率以限制充电电流。

图5 不同Q值下的电流增益Fig.5 Current gain with different Q values

2.2 LLC充电电路实现ZVS

为保证在整个充电过程中谐振电路呈感性,以实现开关管的ZVS,应使变换器开关管频率处于区间Ⅰ。但变换器工作在感性区仅是充电开关管ZVS的必要条件,而非充要条件。实现开关管ZVS的另一个条件是励磁电流在开关死区时间内完成对上下4个开关管并联电容分别进行充放电,之后开关管的体二极管起到续流的作用,使MOS管两端电压为零。如果励磁电流太小,在死区时间内,不能完成对电容的完全充放电,这会导致ZVS不彻底,故对励磁电感的大小也有限制。由文献[14]可知,励磁电感应满足如下公式

式中:tdead是信号死区时间;Ts是开关周期;Cds是MOS管的并联电容。

由式(13)可知,适当加大死区时间可以提高允许的励磁电感值的上限。但死区时间过长,Lr过小,在MOS管开通前体二极管就断流了,无法继续实现钳位MOS管的功能,而使ZVS不完全[15],此时可通过加大Lr的值来解决。

3 参数设计与实验结果分析

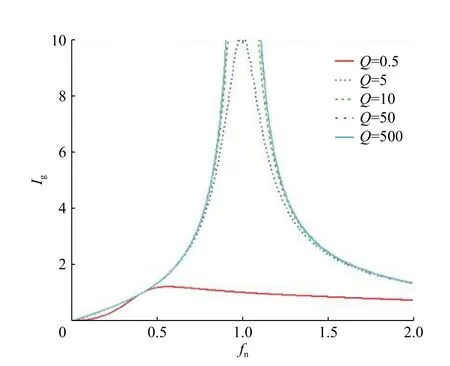

由于脉冲叠加器每级开关管在断开状态与开关管闭合时其二极管两端都将承受其储能电容上的电压,而选取的放电开关管IRG4PF50WDPBF的额定电压为900 V。考虑一定的安全裕量,令每级储能电容的最大充电电压在800 V左右,所以选取10级放电单元合适。为使系统可靠高效地运行,应根据实验中脉冲叠加器负载每次脉冲放电消耗的能量,选择储能电容的大小。储能电容选取过大会使充电时间变长,但太小会满足不了放电功率的要求。设计脉冲叠加器在对负载电阻10 kΩ放电,脉冲电压的顶降不超过初始值的5%。设等效储能电容上的电压为8 000 V,5%的顶降即脉冲结束后电容上的电压为7 600 V,放电脉宽取2 μs,对等效储能电容,其储存能量为

负载消耗的能量为

式中:W1为储存能量;W2为负载消耗能量;Ceq是放电时等效串联储能电容;Ud1是负载放电前电容上的电压;Ud2是负载放电后电容上的电压;td是放电脉冲时间;Ud是脉冲叠加器放电时负载上的电压。根据能量平衡,10级脉冲叠加器每级储能电容不得小于63.3 nF。为实现较高重复频率的放电,选取100 nF储能电容。

设计流程如下:考虑变换器及磁环变压器会产生的损耗,变换器输入电压为90 V,输出脉冲幅值为8 kV,磁环变压器为高频环型铁氧体磁芯绕制,变比为1:100,即变换器的电压增益为0.9;确定谐振频率为80 kHz,以开关频率100 kHz充电,此时在Q=500时对应的电流增益为2.22,变换器开关管选用意法半导体公司生产的STW15NA50,500 V/14 A MOS管,在满足小于MOS管的最大电流情况下,选择合适的特征阻抗值,然后确定谐振电感与谐振电容的值。

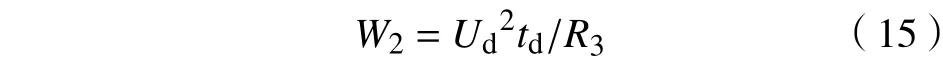

综上选择谐振电感为80 μH,谐振电容为40 nF(由两个高频无感金属化薄膜电容80 nF串联)。控制系统核心为ALTERA公司的Cyclone Ⅱ,产生频率为100 kHz、死区时间为400 ns的充电MOS管信号。在较高开关频率下,考虑输出全桥整流桥中二极管在满足耐压与通流条件时还应满足其中的反向恢复时间小于150 ns。因此选择的超快速整流桥型号为UMB10F,整流桥耐压为1 000 V,反向恢复时间为75 ns,以满足设计要求。选取变压器磁芯材质铁氧体,其饱和磁通密度达0.5 T,保证变压器不饱和情况下,根据式(16)选取合适的磁芯尺寸外径、内径、高度分别为40,20,15 mm。

式中:U为绕组两端的电压;t1为开关管开通时间;S为磁芯的横截面积;ΔB为饱和磁通密度;N为变压器绕组的匝数。

同时,变压器二次侧绕组采用单层绕法,以减小在高频下分布电容的影响。

测量10级放电单元,串联变压器的原边电感为120 μH,并联在MOS管两端电容为300 pF,代入式(13)得Lm为1.5 mH,故充电全过程能实现变换器MOS管的ZVS软开关性能。脉冲叠加器在电阻负载下放电波形为幅值8 kV、频率10 kHz的脉冲。

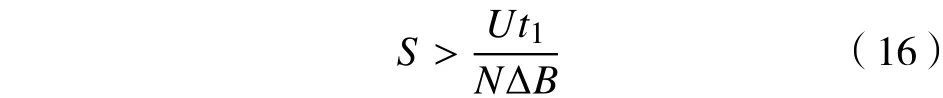

图6为实验平台,图下方为脉冲叠加器,图上右侧为信号控制源与变换器的驱动电路,图上左侧为全桥LLC谐振变换器。变换器的控制信号光耦隔离输入驱动电路,IR2110用作变换器的4个开关管驱动芯片。叠加器的每级放电管信号通过串联磁环的方式进行同步隔离驱动。

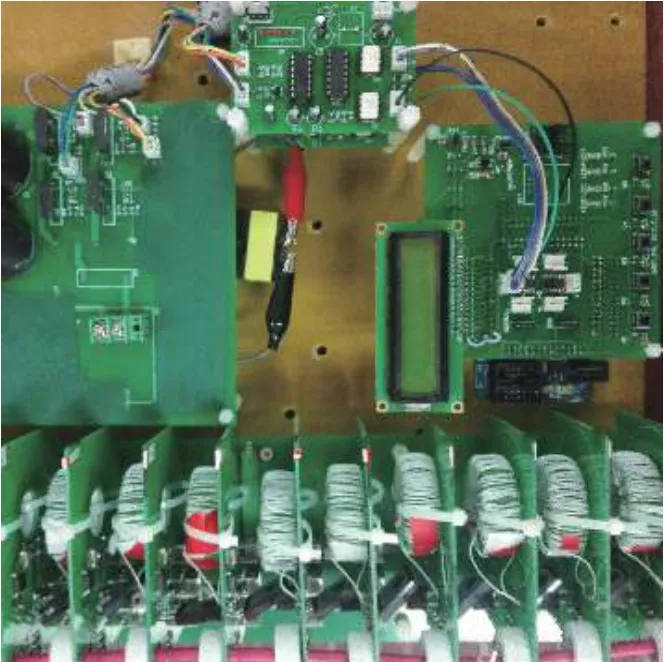

图7 为开关管实现ZVS软开关功能的波形图,其中,S1为下桥臂的MOS管两端电压,即输入电压为90 V,S2为MOS开关管的控制信号,且信号电压为12 V。在开关管信号来临之前,开关管两端的电压被反并联的体二极管钳位,从而实现ZVS,此时开关管的开关频率为100 kHz。

图7 ZVS特性Fig. 7 ZVS character

图8 有无平衡绕组的电压波形Fig. 8 Voltage waveform with & without balance windings

图8 (a)与(b)分别为未加与加了平衡绕组后的三级叠加器放电时电容上电压幅值与负载上电压波形。图中:V1为负载上的脉冲放电波形,其幅值约为2.1 kV;V2,V3为其中两级电容上的电压幅值。比较两图中电容电压的差异可得到,加了平衡线圈的电容电压幅值差异更小,在放电前后幅值都有一定的下降且保持一致。实验结果很好地验证了平衡线圈的作用。

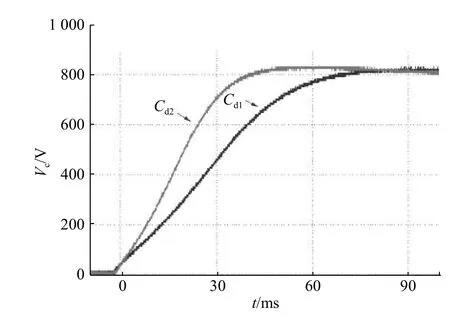

图9为储能电容上的充电电压(Vc)波形图。Cd1与Cd2分别为串联一级、二级变压器时储能电容上的电压波形,充电前期电压上升的速率均匀,可以看出充电电流近似恒定。充电后期,由于高频变压器与输出整流桥中存在的杂散电容、电感,导致了充电电流下降及电压上升速率的减小。同时值得注意的是,串联叠加器放电单元越多,等效储能电容越小,充电的时间也会变短。图10为电阻负载10 kΩ、幅值8 kV、放电频率10 kHz的放电脉冲波形图,图中,V0为负载电压。

图9 储能电容充电电压Fig.9 Storage capacitor charging voltage

图10 负载上的脉冲波形Fig.10 Pulse waveform on load

4 结 论

本文设计的全桥LLC谐振变换器充电源,满足了串联磁芯结构的脉冲叠加器充电需求。本文分析了变换器的工作过程,计算了合适的变换器谐振参数,提出了脉冲叠加器每级电容均压充电的方法,最后搭建了硬件实验平台进行验证。结果表明:变换器的开关管在较高的开关频率下能实现零电压导通;附加平衡绕组的方法使每级电容充电幅值一致;脉冲叠加器能稳定输出高压脉冲。