基于FPGA和EMIFA的SPI控制器系统设计

2019-05-27

(1.中国科学院 光电研究院, 北京 100094; 2.中国科学院大学, 北京 100049)

0 引言

SPI(Serial Peripheral Interface)是由摩托罗拉公司在20世纪80年代中期针对短距离通信提出的一种同步串行通讯接口,被广泛地应用于嵌入式系统中。嵌入式处理器可以通过SPI接口与许多外设芯片如FLASH、气压传感器、EEPROM、高速ADC等[1-4]进行通信。

目前,大部分嵌入式处理器片内都自带了SPI控制器。在有些情况下,SPI控制器的一些片选引脚可能会被其它片内外设所使用,此时如果系统需要控制多路SPI接口外设芯片,可以采用FPGA来扩展多路SPI控制器,通过FPGA扩展出来的SPI控制器与SPI接口外设芯片进行通信[5]。

本文设计了一个具有多路SPI控制器的系统,该系统采用TMS320C6748作为主控制器,采用FPGA作为协处理器。在FPGA上实现了接口模块、寄存器读写模块以及多路SPI模块。DSP芯片通过其异步存储器访问接口EMIFA(External Memory Interface A)可以访问FPGA内的寄存器,与FPGA进行通信[6],从而实现与多路SPI接口外设芯片的通信。采用DSP的EMIFA接口,结合硬件可重置的FPGA,极大地增强了系统的接口扩展能力,系统不仅能扩展多路SPI接口,还能扩展其它通信接口,如UART、CAN[7-8]等。

针对所设计的系统,在ModelSim环境下进行了仿真实验,对SPI控制器进行了简单的收发测试,验证了其逻辑正确。最后,在DSP-FPGA集成计算机上展开实物测试,利用所设计SPI控制器对SPI接口CAN控制器芯片进行控制,实现了CAN通信,验证了该系统的可行性。

1 系统设计

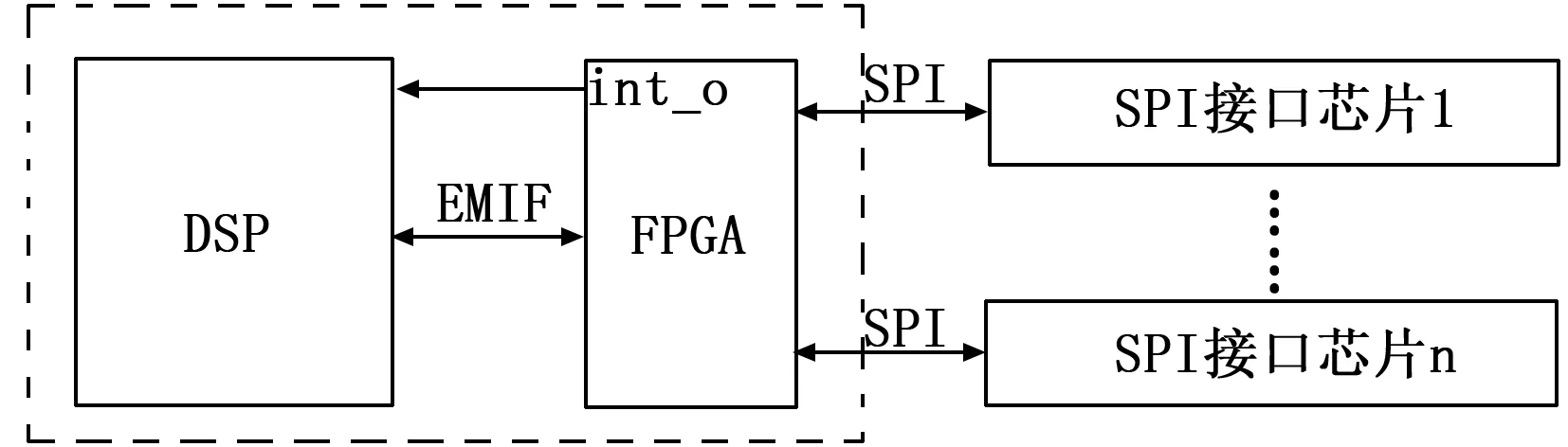

系统的硬件拓扑如图1所示,DSP与FP-GA通过EMIFA接口通信,FPGA的一个引脚作为中断信号引脚连接到DSP的一个GPIO引脚上,FPGA外接多路SPI接口芯片。

当FPGA接收到任意一路SPI接口芯片的数据时,会在其中断信号引脚int_o上产生中断信号,通知DSP读取FPGA接收到的数据。int_o引脚此时由低电平变为高电平,产生了上升沿跳变。若在软件中已经使能了DSP的GPIO BANK中断,且GPIO中断触发类型被设置为上升沿触发,则DSP将产生GPIO BANK中断。DSP在中断子程序中读取了FPGA所接收到的数据后,FPGA将把中断信号引脚int_o的电平清零,此时DSP的GPIO引脚又将恢复为低电平。

图1 系统硬件拓扑图

FPGA实现了接口模块、寄存器读写模块、SPI模块以及中断管理组合逻辑,各模块连接关系如图2所示。

图2 FPGA片内模块连接图

接口模块与DSP的EMIFA接口相连,对EMIFA接口时序解析,产生读控制信号re_o和写控制信号we_o给寄存器读写模块。读控制信号re_o同时还控制三态门的开闭,re_o有效时,三态门将会打开,FPGA输出数据到DSP,否则,三态门关闭,DSP输出数据到FPGA。寄存器读写模块包括各个SPI模块的寄存器,配置SPI模块的工作模式,保存SPI模块接收的数据。SPI模块与外设芯片相连,将接收到的数据存到寄存器读写模块的寄存器中,同时将寄存器读写模块内要发送的数据发送出去。中断管理组合逻辑对各个SPI模块进行中断管理,并产生中断信号输出至DSP。各个SPI模块功能一致,但是相互独立,使SPI接口扩展更为灵活。

为了让模块连接图更为简洁,图2中省略寄存器读写模块与SPI模块间的连接关系,文中后续再给出细节。

2 主要模块设计

2.1 接口模块设计

接口模块的作用是对EMIFA接口时序解析,产生地址信号addr、读控制信号re_o、写控制信号we_o。

对EMIFA接口而言,只要按照EMIFA接口的读写时序定义好接口模块,将FPGA片内寄存器的地址统一映射到EMIFA的访问空间,访问FPGA的片内寄存器和访问其它异步存储器并无二致。

TMS32C6748的EMIFA接口一共有4个片选引脚,标号为EMA_CS[5:2],系统使用片选引脚EMA_CS[2]作为FPGA的片选,则FPGA片上寄存器在TMS32C6748地址空间里的基址为0x60000000。FPGA对外数据总线接口D[15:0]为16位,根据数据手册,TMS320C6748访问16位异步存储器时,其地址线连接关系如图3所示。

图3 EMIFA至16位异步存储器连接图

由图可见接口模块输入端EMIFA地址信号EMA_A[15:0]应连接至输出端地址信号的高16位,接口模块输入端EMIFA的BANK地址信号EMA_BA[1]应连接至输出端地址信号的最低位。接口模块地址转换Verilog代码如下:

assign addr[16:1] = emifa_addr[15:0];

assign addr[0] = emifa_ba1;

EMIFA的读写时序如图4、图5所示[10]。

图4 EMIFA读时序图

图5 EMIFA写时序图

当DSP访问0x6000 0000~0x61FF FFFF地址空间时,EMA_CS[2]信号将会有效[9]。读数据时,OE信号有效,输出低电平;写数据时,WE信号有效,输出低电平。据此,FPGA接口模块可以结合EMA_CS[2]、OE、WE3个信号的电平高低来判断DSP进行的是读操作还是写操作,分别在读信号引脚re_o和写信号引脚we_o上产生有效电平,并输出至寄存器读写模块。由以上分析可得,接口模块输出的读写信号与输入的EMIFA接口读写信号逻辑关系为:

assign we_o = ~cs_n&(we_n == 1’b0);

assign re_o = ~cs_n&(oe_n == 1’b0);

2.2 寄存器读写模块设计

寄存器读写模块保存各个SPI模块的寄存器数据,每一路SPI模块对应寄存器读写模块中3个32位寄存器和1个16位寄存器,各寄存器名称如表1所示,表中n表示该寄存器对应第n路SPI模块。

表1 寄存器读写模块SPI寄存器表

SPI格式寄存器存储SPI模块数据传输的格式信息,其字段描述如表2所示。

表2 SPIFMT寄存器字段描述表

SPI接收数据寄存器存储SPI模块接收到的数据,SPI发送数据寄存器存储SPI模块要发送的数据,SPI延时寄存器存储SPI数据传输的延时信息。

EMIFA数据总线只有16位,因此,每次读写32位寄存器只能读写高16位或低16位。

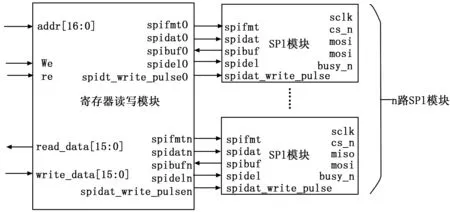

寄存器读写模块与SPI模块的接口关系如图6所示。

图6 寄存器读写模块接口图

在时钟的上升沿,寄存器读写模块分别判断写控制信号we或读控制信号re是否有效。若读写控制信号有效,寄存器读写模块根据输入的偏移地址信号addr确定所要读写的SPI寄存器的地址,对该偏移地址处的SPI寄存器进行读写。

当SPIDAT寄存器低16位数据更新时,寄存器读写模块的spidat_write_pulse信号有效,并保持1个时钟周期。SPI模块检测到spidat_write_pulse信号有效后,将启动数据传输。

寄存器读写模块不仅能保存多路SPI模块的寄存器,还能保存其它通信模块的寄存器。当系统需要扩展其它通信接口,如串口、CAN时,在寄存器读写模块中对每一路通信接口定义一组该接口专用的寄存器即可。通过寄存器读写模块对各个通信接口的寄存器统一管理,简化了通信接口模块的实现。通信接口模块只需关注通信协议的实现,而无需考虑DSP对其相关寄存器的读写操作。

2.3 SPI模块设计

SPI模块对外提供SPI接口,与外设芯片相连。SPI模块实现SPI通信协议,具有以下功能:

1)支持8位、16位、24位、32位4种字长数据传输;

2)支持4种时钟传输模式;

图7为SPI模块的原理框图。MOSI、MISO、CS、SCLK为标准SPI协议引脚,连接外设芯片。BUSY引脚接DSP的GPIO,DSP可以查询该引脚,判断SPI模块是否正在发送数据。SPIDAT、SPIBUF、SPIDAT、SPIDEL端口与寄存器读写模块相连。

SPI模块读取寄存器读写模块SPIDAT寄存器的值输出到外设芯片,从外设芯片接收到的数据则保存到SPIBUF寄存器中。SPIDEL寄存器表示SPI数据连续传输时相邻数据传输时间间隔大小。SPIFMT寄存器控制SPI模块数据传输的格式,包括字长、分频系数、相位极性、移位方向、传输延时。

图7 SPI模块框图

SPI模块分为三部分实现:数据发送、数据接收、模式与时钟发生。txbuf_8b、txbuf_16b、txbuf_24b、txbuf_32b为用于发送数据的缓冲寄存器,对应4种字长的数据发送。SPI模块将SPIDAT寄存器读取到其中一个数据发送缓冲寄存器中,再将其移位输出至MOSI引脚。

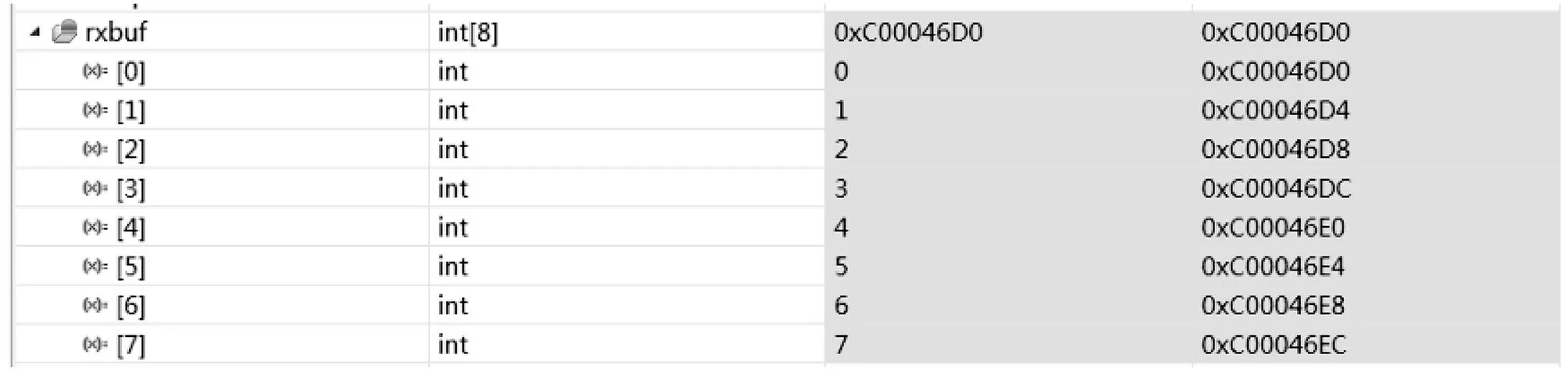

在SPI传输的每个时钟周期内,SPI模块同时会读取MISO引脚接收的数据。根据字长,将MISO引脚接收的数据移位输入到4个接收缓冲数据寄存器中的一个。rxbuf_8b、rxbuf_16b、rxbuf_24b、rxbuf_32b4个接收缓冲数据寄存器分别用于8位、16位、24位、32位4种字长数据传输的数据接收。移位接收完成后,SPI模块再把接收缓冲寄存器的值输出到SPIBUF寄存器。

模式与时钟发生部分从SPIFMT寄存器读取出控制SPI传输的格式信息,包括字长、分频系数、极性、相位、数据移位方向、传输延时等,同时对SPI模块输入时钟分频,输出SPI时钟SCLK。其中,字长表示每次SPI数据收发的位数;分频系数用于调整SCLK大小;SCLK与SPI模块输入时钟的频率关系如式(1)所示:

(1)

极性与相位共同决定SPI传输的时钟模式,根据其不同组合,SPI模块可工作在4种时钟模式下;数据移位方向确定SPI传输是从最高位至最低位还是从最低位至最高位;传输延时表示SPI连续传输时相邻两次传输的最小时间间隔。

SPI模块工作在有限状态机,其状态可分为空闲态、延时态和传输态3种。图8为4种SPI时钟模式下各延时态示意图。

图8 SPI模块传输延时图

其中,延时态C2TDELAY、T2CDELAY、WDELAY分别表示片选有效到第一个SCLK之间的延时阶段、最后一个SCLK到片选无效之间的延时阶段、片选无效到空闲态延时阶段。

传输态有4种模态,每种模态对应一种时钟模式。状态机状态转移图如图9所示。

SPI模块初始时处于空闲状态,当DSP往寄存器读写模块的SPIDAT寄存器低16位写入新的数据后,spidat_write_pulse为1, SPI模块将进入C2TDELAY延时态,片选信号EMA_CS[2]被拉低,延时时间由式(2)计算可得:

TC2T=Tclk*(c2tdelay+1)

(2)

延时结束后,SPI状态机根据极性和相位的组合,切换至4种传输模态之一。在传输模态,SPI模块发送数据到MOSI引脚,同时从MISO引脚读取数据。发送完成后,状态机依次切换至T2CDELAY延时态和WDELAY延时态,两个延时态的延时时间由式(3)和式(4)可计算得到:

TC2T=Tclk*(t2cdelay+1)

(3)

TW=Tclk*(wdelay+1)

(4)

最后,状态机回到空闲状态,等待DSP启动下一轮的数据传输。

图9 SPI模块状态转移图

2.4 中断管理

FPGA接收到SPI外设芯片的数据后,通过中断方式通知DSP读取所接收到的数据。一种简单的中断管理方式是FPGA为每一路SPI外设芯片都配置一个中断信号引脚,每一个中断信号引脚分别连接到DSP的不同GPIO引脚上。当FPGA接收到来自不同的SPI外设芯片发送过来的数据时,就在其所对应的中断信号引脚上产生中断信号。在SPI外设芯片较少的时候,这种方法简单实用,但是在SPI外设芯片较多时,该方法将占用较多GPIO。

系统采用了一种常用的中断管理方法,所有SPI外设芯片共用一个中断信号引脚,通过中断标志寄存器来判断中断源是谁。每一路SPI外设芯片都是一个中断源,对应中断标志寄存器中的一个标志位,当FPGA接收到SPI外设芯片数据时,会将中断标志寄存器中相应的标志位置1,并在中断信号引脚上产生中断。DSP在GPIO BANK中断处理子程序中读取FPGA的中断标志寄存器即可判断中断源是哪一路SPI外设芯片,在读取中断标志寄存器后,所有中断标志位将自动清除。

3 系统仿真与测试

在ModelSim环境下对系统进行仿真,在激励模块中,先对寄存器读写模块中的相关寄存器进行设置。为了便于观察,在仿真程序中设置分频系数为7,SCLK频率为输入时钟的8分频。c2tdelay和t2cdelay均设为7,则C2TDELAY和T2CDELAY延时态均为延时8个SPI模块输入时钟周期。字长设置为8位,移位输出方向设为从最高位到最低位,相位和极性均设置为0,主机在SCLK上升沿输出数据到MOSI引脚,在SCLK下降沿锁存MISO引脚输入的数据。

测试过程如下,激励模块通过EMIFA接口往SPIDAT寄存器低16位写入0x00AA,启动SPI数据发送。因为字长为8,每次SPI模块只发送SPIDAT的低8位,所以SPI模块应发送0xAA到激励模块。为了观测SPI模块是否能进行全双工通信,在SPI模块发送0xAA到激励模块的同时,激励模块也发送0x55至SPI模块。然后读取寄存器读写模块的SPIBUF寄存器的低16位,如果SPIBUF寄存器低8位为0x55,说明接收逻辑正确。仿真波形如图10所示。

图10 仿真波形图

由图10可见,FPGA输出到MOSI上的数据为10101010,故发送给激励模块的数据为0xAA,与激励模块写入SPIDAT寄存器低8位的数据一致;MISO上接收的数据为01010101,故FPGA读取到的数据为0x55,与激励模块发送给SPI模块的数据一致。可见收发逻辑均无误,所设计的系统在仿真实验中可以进行正常的全双工通信。

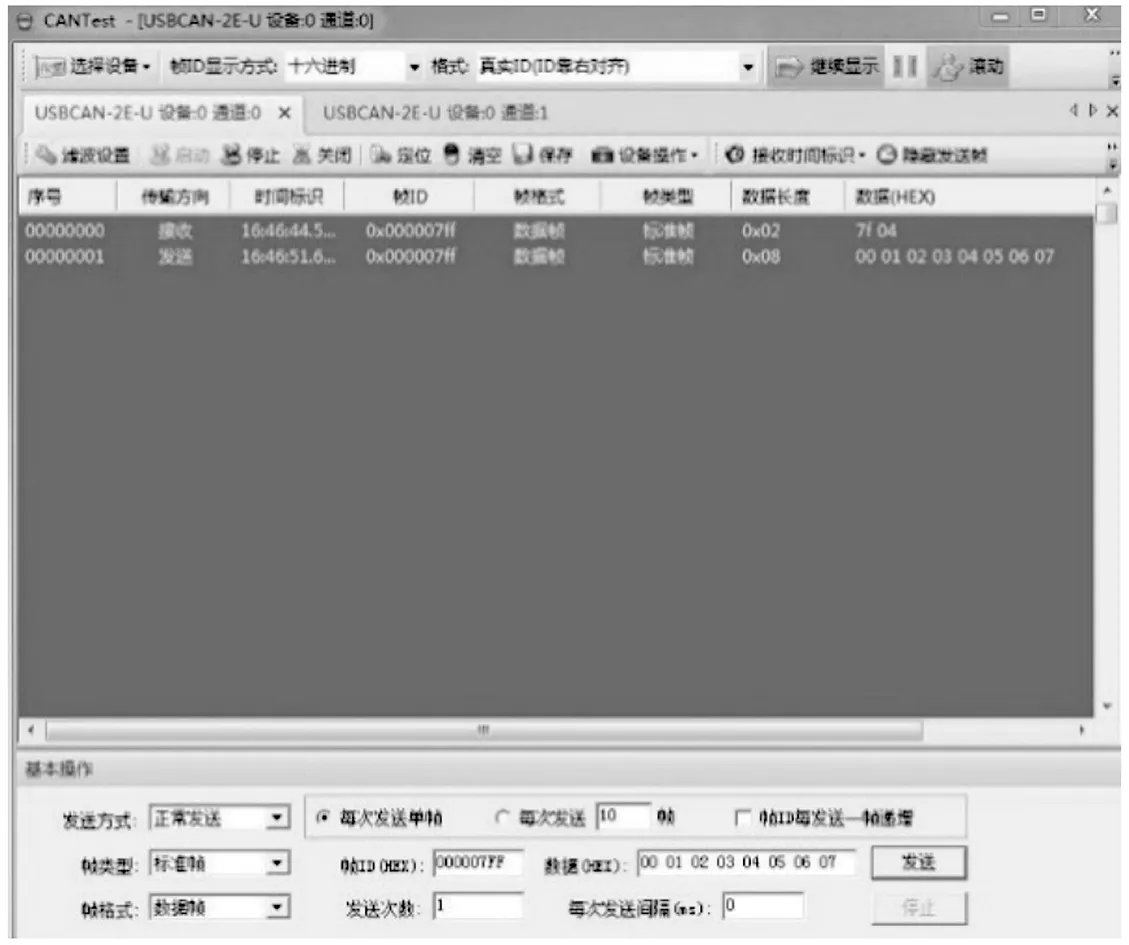

为了验证设计的SPI控制器能否正常工作,将具有SPI接口的CAN控制器芯片MCP2515连接到FPGA扩展出的SPI控制器引脚上进行测试。

DSP先发送一帧数据到上位机,帧ID为0x7ff,数据为0x7f、0x04。然后上位机再发送一帧数据到DSP,帧ID为0x7ff,数据为0x00、0x01、0x02、0x03、0x04、0x05、0x06、0x07。测试结果如图11和图12所示。由图11可以看出,上位机接收到一帧数据,帧ID为0x07ff,数据为0x7f、0x04,与DSP发送的数据一致。然后上位机返回一帧数据给DSP,帧ID为0x7ff,数据为0x00、0x01、0x02、0x03、0x04、0x05、0x06、0x07,DSP接收到的数据如图12所示。可以看到,与上位机发送的数据一致,说明MCP2515可以实现正常的CAN数据收发,所设计的SPI控制器系统可以正常地与SPI外设芯片通信。

图11 上位机收发图

图12 DSP接收数据图

4 结语

本文实现了基于FPGA和EMIFA的SPI控制器。在FPGA上扩展了多路SPI控制器,TMS320C6748通过EMIFA接口访问通过FPGA扩展的SPI控制器,实现了与多路SPI接口外设同时通信的需求。采用模块化设计的方法,系统具有良好的可扩展性。经过仿真测试与实际硬件测试,证明了该系统工作正常。