多处理器系统程序自动更新和监测方法研究

2019-05-17王昊,王维

王 昊,王 维

(中铁工程设计咨询集团有限公司,北京 100055)

1 概述

列车超速防护系统(Automatic Train Protection,ATP)是既有高铁、地铁运行控制系统和处于研发阶段的C1 列控系统、下一代列控系统的重要组成部分之一。其主要作用是保持列车间的安全间隔,使列车在符合限制速度的标准下安全、高效运行。目前我国高速铁路设备的研发已经取得了世界领先的成绩,尤其是具有完全自主知识产权的列控系统[1]。

由于ATP 主机与外围设备通信内容和接口的多样化,导致其硬件构成比较复杂。一套完整的ATP 主机往往由多块板卡构成,比如主控板卡、无线通信板卡、采集板卡等;部分安全板卡上有多块处理器。目前主流的200C、300T 等ATP 主机在软件调试和测试过程中,需要采用串口或JTAG 等方式对不同的处理器进行编程,以JTAG 接口对FLASH 存储器编程为例,需要PC 机发送指令或数据到JTAG 兼容芯片的边界扫描寄存器,然后将寄存器中的指令或数据通过JTAG 专用指令传送给FLASH,整个过程需要有PC 机上的软件进行控制[2]。列车在运营阶段,如果需要升级车载设备代码,通常由电务人员进行人工烧录操作,而且由于各处理器需要烧录的程序不一样,繁重的工作量会导致人为原因出现差错的可能性,并且没有一种有效的手段去监测烧录过程中人为因素或通信故障出现的错误,会造成安全隐患;同时因为需要电源、仿真器等外围设备,并且JTAG 口往往都未引出到设备面板外,经常性的拔插操作对板卡硬件的寿命有不良影响。为解决这一问题,提出一种基于嵌入式的多处理器系统程序自动更新和监测方法。

2 多级处理器自动识别、更新程序文件

2.1 多处理器系统结构划分

一套完整的ATP 主机比较复杂,一般由多块板卡构成,包括主控板卡和多块用于接收和解析BTM、TCR、无线信息模块等数据的通信板卡。基于ATP 主机的可靠性和复杂度,在研发阶段,大部分板卡间的通信方式都设计为串行通信。因此,这些通信板卡围绕主控板卡构成多层次串行通信关系。本文旨在通过向主控板卡插入存储有目标程序的U 盘、TF 卡或移动硬盘等便携式存储设备,达到ATP 主机自动并有选择地更新有软件升级需求的板卡。

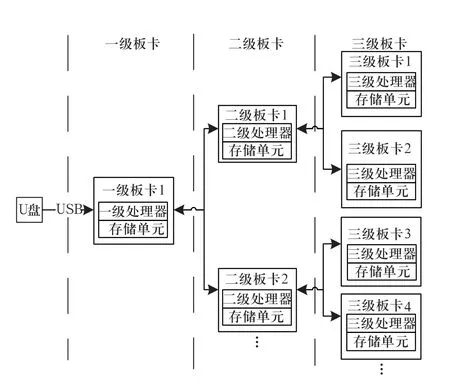

ATP 主机包含多块板卡和可编程芯片,将主控板卡上的处理器定义为一级处理器,与一级处理器直接通信的通信板卡上的处理器定义为二级处理器,后续与二级处理器通信并且与一级处理器无通信接口的处理器定义为三级处理器,依次类推,结构如图1 所示。受篇幅所限,本文内容仅涉及三级通信结构。

2.2 程序自识别流程

图1 多级处理器结构Fig.1 Multiprocessor architecture

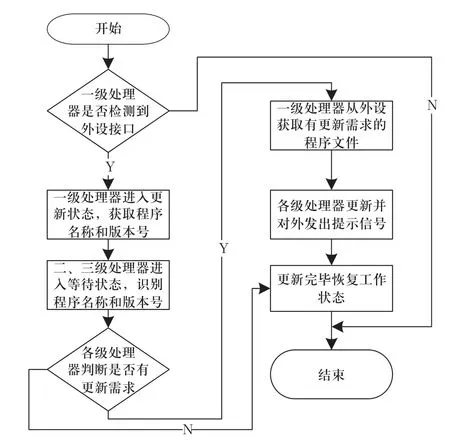

ATP 系统启动时,检查外设接口状态,若未检测到外设,则进行软件自检,自检完成后进入工作模式;若有外设接入,则进入更新模式。为防止列车在运行过程中进入更新状态而出现运营事故,主控板卡在进入工作模式后,关闭USB 中断或跳过检测相应外设接口任务。

一级处理器在更新状态下,向其后级处理器发送等待指令使其后级处理器处于等待状态,同时发送从外设中获取目标程序的名称和版本号。二、三级处理器接收相关信息后,与当前程序进行对比,判断是否需要更新。若无需更新,则向一级处理器发送相关指令,并对外发出表示无需更新的信号;若需要更新,则向一级处理器发送需求指令并进入更新状态。一级处理器接收到后级需求指令后,有选择地获取外设中的目标程序。二、三级处理器接收和替换相应程序,更新完毕后,向一级处理器发送相关指令,并对外发出更新完毕的信号。一级处理器收到所有后级指令后,各级处理器恢复工作状态,如图2 所示。

通过各板卡对外发出提示信号,工作人员可以清楚地知道系统当前的更新情况,防止出现因外设中更新程序名称或版本号错误导致的应更新而未更新的情况。

2.3 程序自动更新方式

图2 程序文件识别流程Fig.2 Program files identification process

处理器上电后将FLASH 中的程序调入到RAM 中运行,由于FLASH 上已经没有程序运行,因此可以安全地对其进行烧写,而不会影响系统的程序运行[3]。为保证目标程序的正确性,在程序烧录过程中,将RAM 作为接收目标程序的缓冲区。在接收符合版本号的程序完毕后,对其进行校验,校验无误后就可以把RAM 缓冲区里的目标程序烧写到FLAH 中了。FLASH 烧写完毕后,对其内容进行校验,以确保FLASH 中的程序无误。

设备更新过程中不可避免会遇到意外断电、通信中断或是人为停止更新等情况[4]。在上述情况发生的前提下,必然会导致FLASH 中的代码不全,从而导致设备上电重启后无法正常更新或工作。为防止此类情况发生,可以在FLASH 中开辟一块空间,存储库函数和用于外设接口检测、执行烧录的程序等,在每次自动更新的过程中,该区域的代码不能被修改。以TMS320F2833X 系列DSP 为例,程序是从DSP2833x_CodeStartBranch.asm 文件中定义的codestart 处开始,其指定位置在CMD 文件内定义,如下:

MEMORY

{

PAGE 0 :

BEGIN :origin=0x33FFF6,length=0x000002

...}

SECTIONS

{...

codestart : > BEGIN PAGE = 0

...}

3 数据传输安全性

3.1 目标文件安全获取措施

ATP 系统对安全性和可靠性有很高的要求,目前国内外铁路信号产品的安全计算机主要采用二乘二取二或三取二2 种结构[5]。“二取二”即为在1 套系统上集成两套CPU 系统,两套系统严格同步,实时比较,只有比较一致时才对外输出运算结果;“二乘”即为两套软硬件完全一致的“二取二”系统工作,分别构成系统的A、B 系,两系互为热备[6]。三取二系统中,3 个处理单元独立运行,两两进行数据比较,当某一个单元故障或数据与其他处理单元不一致时,去除该单元,系统降级为二取二模式[7]。

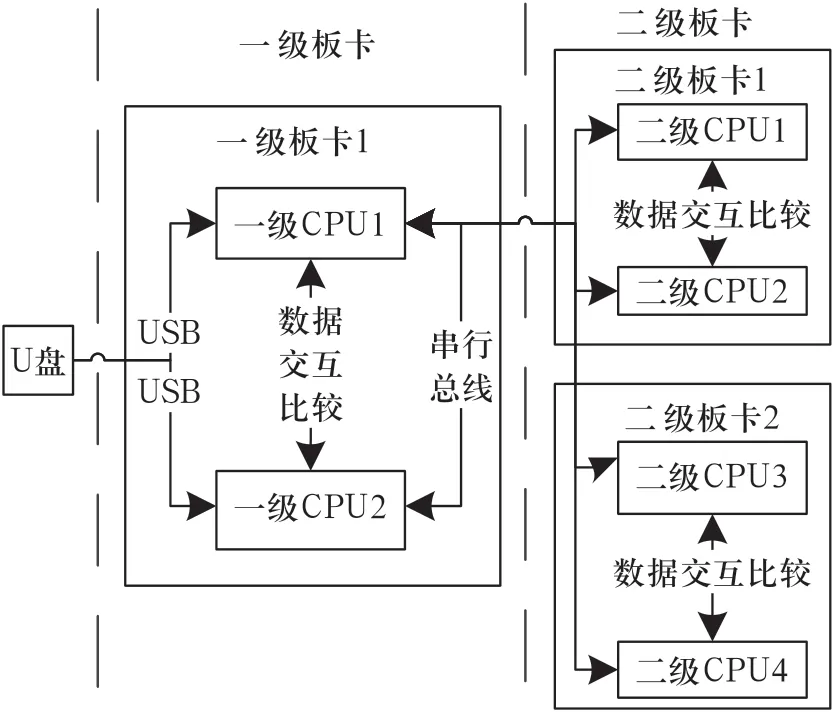

本文以一系二取二为例,一级板卡上的两个相同一级处理器分别描述为CPU1、CPU2。两个一级CPU 采集到外设的目标程序文件后,存储到RAM 中,并进行校验,此过程仅能确保两个CPU获取到的目标程序文件在内容上的正确性,并不能确定一致性。因此,CPU2 以一定的协议向CPU1发送目标数据,CPU1 将从外设采集并通过校验的数据与CPU2 发送的输入数据进行比较;如果数据比较后一致,则由CPU1 向后级处理器发送相应的目标程序;若数据交互比较有误或至少一块CPU中的更新程序未通过校验,则一级处理器重新采集外设存储的文件。

为防止因外设中程序内容的错误或交互通道的故障导致重复采集外设数据,可对采集过程进行计数,并根据重复采集原因对外发出相应提示信号,以便工作人员定位故障。更新系统通过多个相同的一级处理器之间的数据交互比较,确保在一级板卡内的目标文件数据是正确的,从而提高目标文件在传输过程中的安全性。

3.2 后级传输过程

上述数据比较方法仅能确保一级处理器接收到目标程序的正确性,而且在二取二或三取二等安全控制系统中,串行通信多采用一对一方式。一般由1 个CPU 进行集中处理,其他CPU 基本无法对输出的串行信号进行仲裁和监测,信息的接收和发送没有真正实现N 取N。当1 个CPU 出现故障导致数据输出异常时,从数据上很难定位异常的CPU,导致很难判断异常原因,给系统的查错带来很大的困难;同时由于缺少其他CPU 的监测,在极端情况下会给系统带来安全隐患[8]。

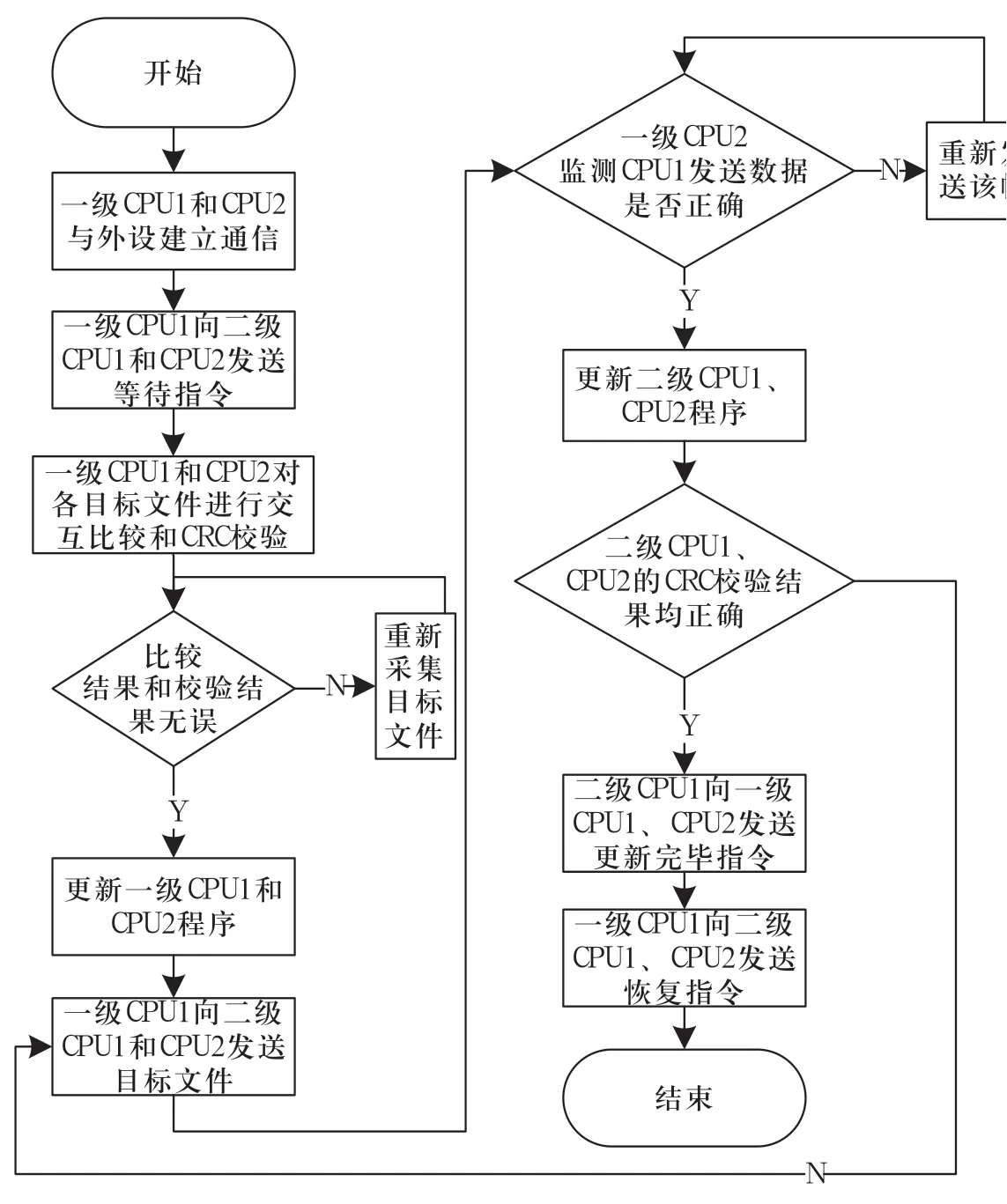

为确保向后级传输过程的无误,本文采用双通道比较方法。在数据后传的过程中,一级CPU1通过通道1(串行总线)向后级处理器发送目标程序的同时,通过通道2 向CPU2 发送目标文件,如图3 所示。CPU2 对两个通道接收到的数据同自身数据进行比较,若数据比较结果不同,则向CPU1 发出数据有误的信号;CPU1重新向后级处理器和CPU2 发送该数据,若重新发送数据步骤多次重复出现,则对外发出提示信号,此时可定位到通信通道发生故障,如图4 所示。二级处理器向三级处理器发送更新程序时,也可采用上述方法。

CPU2 在比较双通道和自身数据时,要严格遵循时间戳顺序,即保证两个通道和CPU2的时间戳保持一致,避免出现交互比较不同时间戳的数据而产生对更新效率和程序正确性不利的影响。为保证程序更新的效率和安全性,在更新过程中关闭所有与更新无关的中断,以防止在程序更新过程中被其他任务打断或接收到非更新程序的数据。本方法的有益效果在于,通过双通道的数据比较,确保数据的安全性和同时性,避免目标文件在板卡内进行处理及传输时发生的错误,保障了从板卡输出的目标文件是准确的,从而提高目标文件在系统内传输过程中的安全性和可靠性。

4 结语

图3 安全通信结构Fig.3 Secure communication structure

图4 程序自动更新和监测流程Fig.4 Automatic program update and monitoring process

本文为解决车载ATP 主机在研发调试、测试、后期维护过程中频繁或大批量更新程序遇到的人工失误、数据传输故障等问题,提出上述程序自识别、更新、监测方法。该方法能够自动识别复杂系统中有软件更新需求的处理器,同时在自动升级过程中,对通信数据和存储内容进行检测,从而达到减少软件升级过程中的人工操作和风险隐患的目的。本文内容不仅局限于铁路信号设备和串口通信方式的应用,在其他领域的多处理器复杂系统的程序更新均可以此为参考。