基于Zynq的皮下指纹OCT数据采集系统设计

2019-05-13

(浙江工业大学 信息工程学院,浙江 杭州 310023)

光学相干断层扫描技术(Optical coherence tomography,OCT)由美国麻省理工学院的研究小组于1991年首次提出,OCT是基于低相干干涉原理,通过测量从样品反射回来的后向散射光的强度对样品进行断层成像的技术[1]。OCT技术具有非侵入、高分辨和活体检测等优势,能够对生物组织在毫米深度范围内提供微米级分辨率的图像,在生物组织活体检测和成像方面具有广泛前景[2]。传统指纹识别会遭遇指纹破损、手指潮湿和人工指膜伪造等问题[3-4]。人体皮肤由表皮、真皮和皮下组织3 部分构成,并含有附属器官(汗腺、皮脂腺等)以及血管、淋巴管、神经和肌肉等[5]。手指表皮层与真皮层间的分界处叫做乳头层,表皮指纹来源于乳头层,因此可以用乳头层结构来替代表皮指纹,且真皮层指纹不会因为手指表面皮肤的破损而损坏[6-7]。同时通过OCT采集到的指部生物信息还包括皮下汗腺信息,能更好地进行生物识别和区分虚假指纹。在二十多年的发展过程中,OCT信号的探测方式从时域OCT(Time domain OCT, TD-OCT)成像过渡到了频域OCT(Fourier domain OCT, FD-OCT)快速成像的阶段[8-10]。频域OCT的原理基于迈克尔逊干涉仪,通过参考臂和样品臂反光镜的反射回来的光会在耦合器相遇,并发生叠加和干涉,干涉的信号会被感光元器件接收,之后进行快速傅里叶变换后,就能够得到所测样品的深度信息[11-12]。

OCT系统中一般会使用CCD(Charge coupled devices)作为感光元器件接受干涉光谱信号[13]。但使用CCD作为感光元器件,需要对CCD提供外部驱动,一般使用FPGA(Field programmable gate array)驱动。FPGA是可编程逻辑器件,针对CCD图像传感器不同的应用场景,可以修改FPGA的内部逻辑完成环境适配,具有很高的灵活性,与一般DSP(Digital signal process)处理器相比,FPGA具有更强的复杂时序输出能力[14]。笔者 提出的系统是在频域OCT的基础上,使用Xilinx公司的Zynq芯片来进行信号采集、传输及预处理。芯片由PS(Process system)与PL (Programmable logic)两部分组成,PS部分以ARM Cortex-A9处理器为核心,内部集成DDR存储器控制器和大量的I/O口外设[15]。PL层具有FPGA的功能,是在Xilinx 7系列的FPGA基础上嵌入了Block-RAM、DSP Slice和MMCM等功能单元[16]。利用FPGA的高并行性,可以进行高速的数据采集及数据处理[17]。本系统通过在PL部分进行硬件驱动、数据缓存以及预处理算法的设计,完成皮下指纹信息数据的获取和预处理,在PS部分完成数据与PL端间交互和运行移植的Linux操作系统,最终将处理后的数据通过千兆网口传输给上位机进行显示。

1 系统总体架构

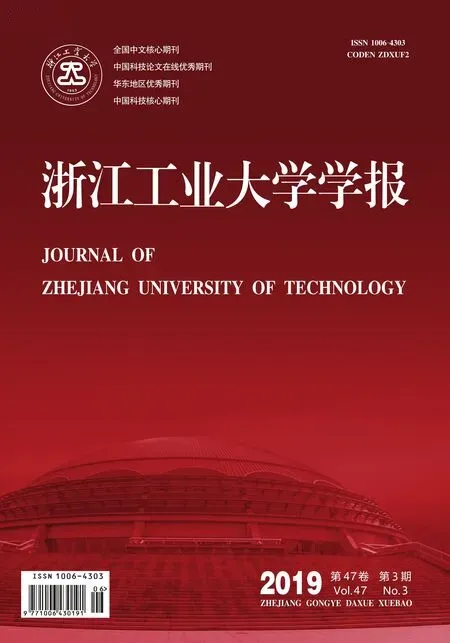

OCT数据采集系统由一个自主设计的线阵CCD相机、光学设备以及PC机3 部分组成。系统的结构图如图1所示,功能框图如图2所示,光源发出的光经过耦合器分光后,以50︰50的比例均匀分成两束光分别射入参考臂和样品臂。被参考臂中平面镜反射回来的光,与样品臂中通过扫描振镜系统对样品进行扫描后反射的光在光纤耦合器中发生叠加和干涉,包含样品深度信息的干涉信号经过光谱仪解调,被线阵CCD采集。线阵CCD可以将接收到的像,也就是光信号,转换为模拟电信号后通过放大器输出[18]。模数转换模块(Analog digital converter, ADC)将经过放大的模拟电信号按照一定的频率进行采集和转换,输出一系列离散的数字电信号。Zynq芯片负责给线阵CCD和ADC提供相应的时序驱动,保证上述两个模块的正常运行。PS-PL模块和数据预处理模块负责对经AD采集后的数据的存储、传输及图像预处理。经过处理的数据通过千兆网口,上传给上位机进行显示。

图1 基于光谱仪的频域OCT结构图Fig.1 Structure of the frequency domain OCT spectral-based

图2 OCT数据采集系统功能框图Fig.2 The functional block diagram of the system

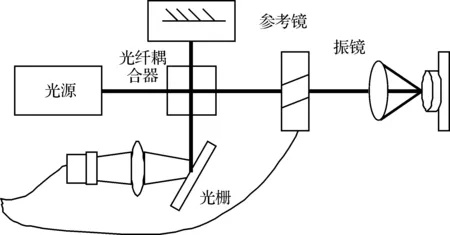

系统硬件架构如图3所示,系统主要由线阵CCD传感器模块、放大模块、A/D转换模块、Zynq处理器控制模块、DDR3数据缓存模块、千兆网口模块、同步触发模块以及电源模块组成。本系统中,处理器控制芯片是Xilinx公司Zynq系列下的XC7Z020,芯片内部具有丰富的逻辑资源。CCD传感器模块采用IDT49FCT805,ISL5510,EL7156型芯片作为CCD驱动电路,驱动Teledyne DALSA公司的IL-P3-B型线阵CCD采集图像。A/D转换模块采用的是ADI公司的一款具用40 MSPS处理速度,12 bits精度以及CDS相关双采样功能的前端模拟采集芯片AD9945。放大模块采用MAX4224电流反馈型运放,具有超高速性能、低失真及低功耗的优点,特别在视频应用中有突出表现。DDR3数据缓存模块使用两片MT41K256M16HA型号DDR3,存储容量为8 Gb。千兆网口模块选用Marvell公司的一款能够自适应10 MB/100 MB/1 000 MB工作方式的PHY芯片88e1518型号,与Zynq处理器控制模块连接,将数据从DDR3数据缓存模块通过千兆网口模块搬至与PC机。同步触发模块使用了具有多通道的隔离输入与输出功能的ISO7240C型号芯片。电源模块采用直流12 V输入,通过DC/DC产生5,3.3 V电压,再由电源芯片产生各模块需要的12.5,14,2,1.2,1,1.8,-5,-2 V电压。

图3 系统硬件架构Fig.3 Structure of the system hardware

2 系统硬件驱动模块设计

2.1 CCD模块驱动设计

本系统采用IL-P3-2048B作为感光元器件,它是一款高灵敏度、高信噪比以及光积分时间可调的线阵CCD器件。IL-P3-2048B的像元尺寸为14 μm×14 μm,它的像元输出频率最高能达到40 MHz,在有效像素为2 048 个像素的情况下其最高扫描行频为19 kHz[19]。

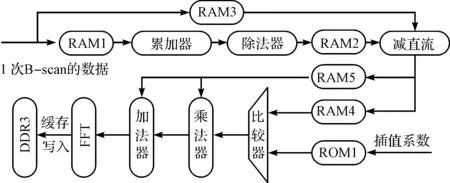

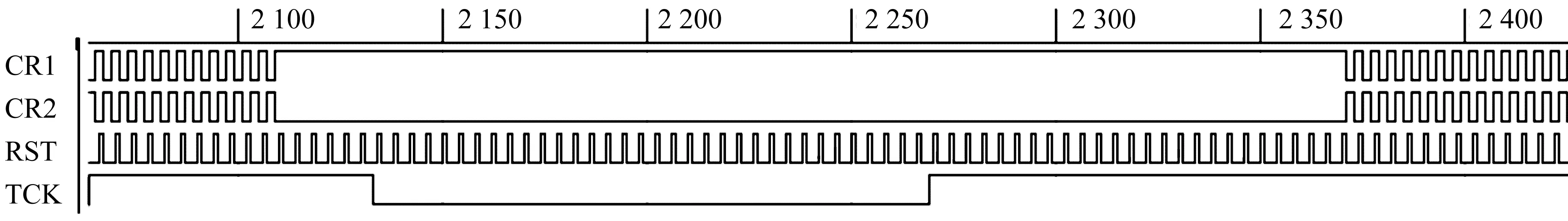

笔者设计的系统中,一次线扫描的像元数为2 205 个,其中有效像元数为2 048 个,在输出有效像元前有18 个虚像元和6 个暗像元,在第2 048 个有效像元后还有2 个虚像元和131 个过渡时钟像元。在2 048 个有效像元结束后产生一个转移脉冲TCK,脉冲宽度为500 ns。FPGA需要输出5 路驱动信号,线阵CCD才能正常工作。驱动信号分别是两相时钟信号CR1和CR2,寄存器末端读出钳位信号CRLAST、复位信号RST以及转移信号TCK。驱动信号的时序相位关系如图4所示。为了最大化采集速度,系统工作时钟为40 MHz。本系统外部晶振频率为80 MHz,通过MMCM核倍频能够得到320 MHz的全局时钟,对该全局时钟进行计数,以计数器的值作为参考,通过对计数器值的判定来决定信号脉冲的时刻与宽度。其中,CR1是占空比50%的40 MHz时钟信号,CR2与CR1同频反相,CRLAST通过硬件芯片分出,RST是占空比25%的40 MHz的时钟,TCK是在有效像元结束后拉高。

图4 IL-P3驱动时序图Fig.4 Timing design of the IL-P3 driving

2.2 AD模数转换模块

本设计中CCD工作时钟为40 MHz,由于AD采样时钟应与CCD的工作时钟相同,因此需要选用一款工作频率能达到40 MHz的AD采样芯片。ADI公司推出了一款专门针对CCD信号采样的AD9945型号芯片,最大采样频率能达到40 MHz,支持快速12 位40 MSPS模数转换,拥有低噪声的暗电平钳位电路,消除CCD暗电流影响,同时其内部还集成了6~40 dB的可变增益放大器[20]。

正确配置AD的内部寄存器及提供匹配的外部驱动时序,AD9945才能正常工作。Zynq芯片提供SCK,SDATA,SL信号驱动时序来进行寄存器配置。在SL信号为0时,持续写入寄存器值,当连续写入寄存器值时,只需要给出第1 个寄存器的地址位,如果寄存器数据位小于12 位时,需要将其补足。SCK信号频率需要小于10 MHz,本设计中全局时钟分频产生频率为1 MHz占空比为50%的 SCK信号,根据SCK信号设计一个52 位计数器,在计数器计数时SL信号拉低为0,其余时间拉高为1,在SCK每个上升沿对SDATA进行数据写入。

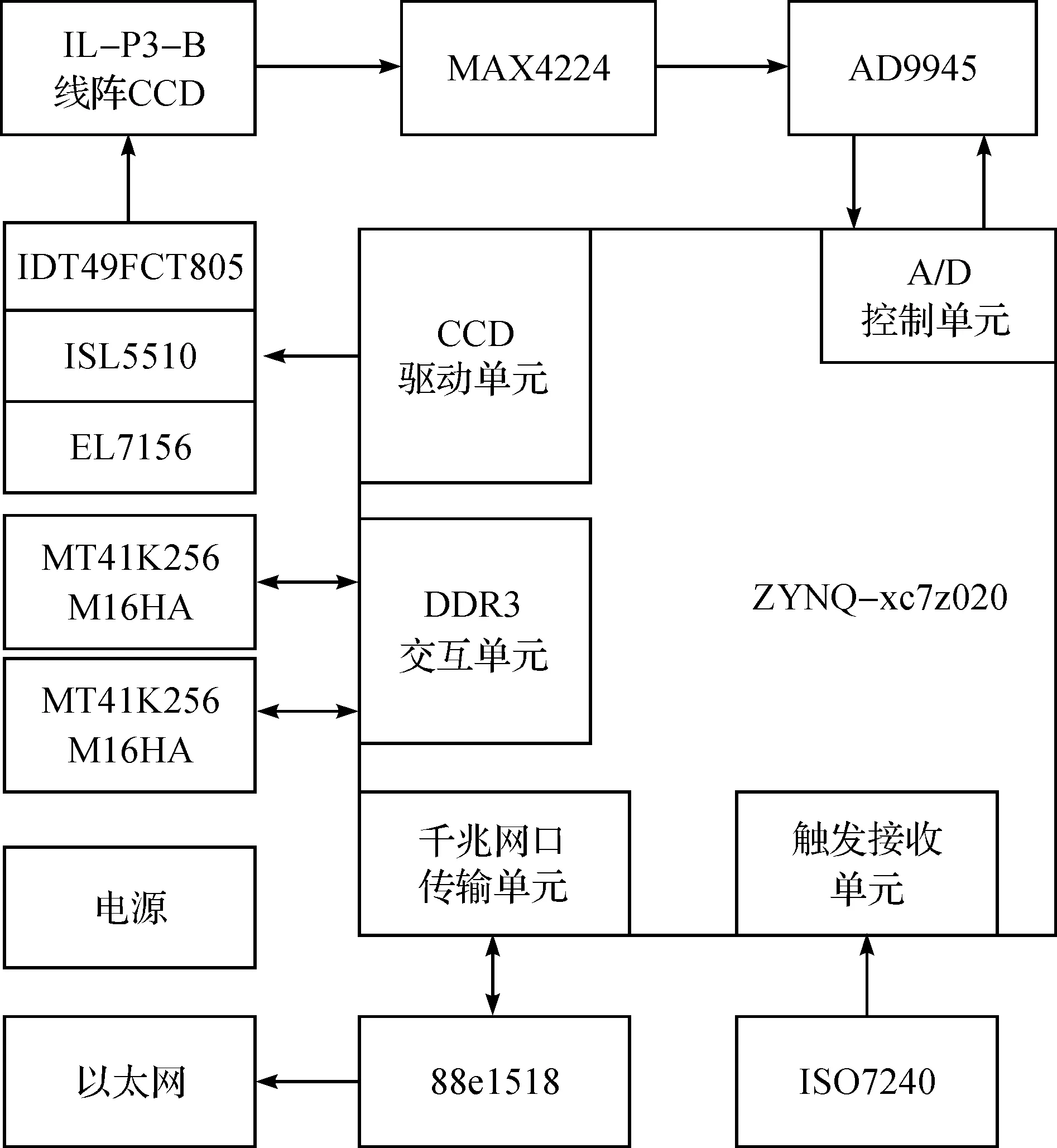

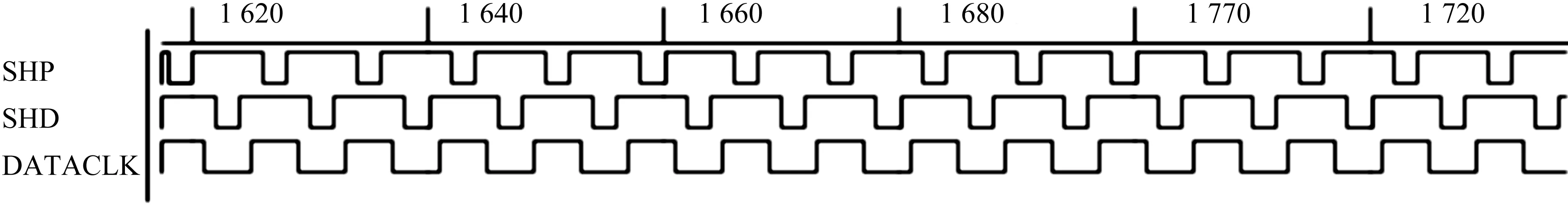

串行控制线连续写入数据完成AD9945内部寄存器配置后,还需要产生三路采样时序完成AD9945的相关双采样功能。采样时序由数据同步时钟DATACLK、高电平采样时钟SHP和参考电平采样时钟SHD组成。设计时序如图4所示,分别在SHP和SHD上升沿对CCD信号进行采样,10 个时钟后,输出两次采样差值得到的数字信号。DATACLK是一个占空比50%的40 MHz时钟,SHP和SHD为占空比75%的40 MHz时钟,且SHP和SHD相位差180°。根据320 MHz的全局时钟信号设计1 个8 位计数器,以计数器的值作为参考,通过对计数器值的判定来决定信号脉冲的时刻和脉冲宽度,产生芯片要求的DATACLK,SHP,SHD信号,如图5所示。

图5 AD9945相关双采样时序图Fig.5 Correlated double sampling timing of the AD9945

3 基于DDR的数据搬运模块设计

3.1 PS-PL交互模块

Zynq平台内部PS与PL之间互联都是基于AMBA (Advanced microcontroller bus architecture)总线完成的。AMBA4.0总线包括3 种总线标准,分别是AXI4协议标准、AXI4-Stream协议标准和AXI4-Lite[21]。其中,AXI接口共有AXI_ACP接口(加速器一致端口)、AXI_GP接口(AXI通用接口)和AXI_HP接口(AXI高性能接口)等3 种类型[21]AXI_HP接口是64 位的数据接口,可以为Zynq平台提供最大的总带宽,更适用于高性能或者高带宽的任务。设计需要完成从PL端将数据写入DDR的功能,所以自主设计了PS-PL交互模块。为了最大化系统的采集性能和传输效率,本模块采用的是AXI4总线协议与AXI-HP接口。

为了最大化系统间的传输效率,本系统使用数据位宽64 位的AXI_HP接口,突发长度256,一次突发传输可以传送2 kB的数据。

PS-PL交互模块由读突发传输模块和写突发传输模块组成。在写突发传输模块中,设计了一个数据位宽64位,深度4 096的DDR前级FIFO,其功能是将待写入AXI4总线的数据缓存进FIFO中,同时完成写入时钟到Zynq工作时钟的时钟域变换。为了保证写入AXI4总线数据不为空,对进入FIFO中的数据进行计数,当进入FIFO的数据个数大于2 048时,将DDR写使能信号拉高。在接收到DDR写使能有效信号后,拉高写突发使能信号W_FLAG及写数据有效信号WVALID。根据写突发使能信号与写地址准备信号AWREADY,生成写地址有效信号AWVALID。当AWVALID信号与AWREADY信号同时为高时,生成写地址信号AWADDR。检测写数据准备信号WREADY,当WVALID信号与WREADY信号同时为高时,进行写数据操作。通过对写数据进行计数,当一次突发传输完成最后一个数据的传输时,拉高WLAST信号。检测WLAST信号,当WLAST信号为高时拉低写突发使能信号W_FLAG及写数据有效信号WVALID。写响应准备信号BREADY一直拉高。当完成一次写突发传输后,拉高DDR读使能信号。当DDR读使能信号有效时,拉高读突发使能信号R_FLAG及读地址有效信号ARVALID。检测读地址准备信号ARREADY,当ARREADY与ARVALID都为高时生成读地址信号ARADDR。通过检测读数据准备信号RREADY与读数据有效信号RVALID,当RREADY信号与RVALID都拉高时,进行读突发传输。检测RLAST信号,当RLAST信号拉高时,RREADY信号拉低。当数据从DDR读出后,写入深度为4 096的异步FIFO中,完成AXI4总线读突发传输。

3.2 数据预处理模块

(1)

式中:k为波数;s(k)为电场强度的振幅;Rr为参考臂的功率反射率;Ri为i点的背向功率散射率;hi为距离样品表面di位置的对应光程差,hi=2(l+nidi),其中l是参考镜的虚像和样品表面之间的距离,ni是i点的折射率,di是样品散射点i的深度。第1 项、第2 项为直流项,第3 项为色散噪声。通过对手指表皮的1 次B-scan(横向扫描),共有500 组B-scan(轴向扫描)的数据,对一个B-scan中所有光谱进行求平均,并将每个B-scan信号都减去光谱平均值,就可以去除直流项。通过对光学平台的硬件补偿来去除色散噪声,那么

(2)

对其进行傅里叶变换,那么FD-OCT的图像函数i(h)为

(3)

忽略第一项镜像噪声

(4)

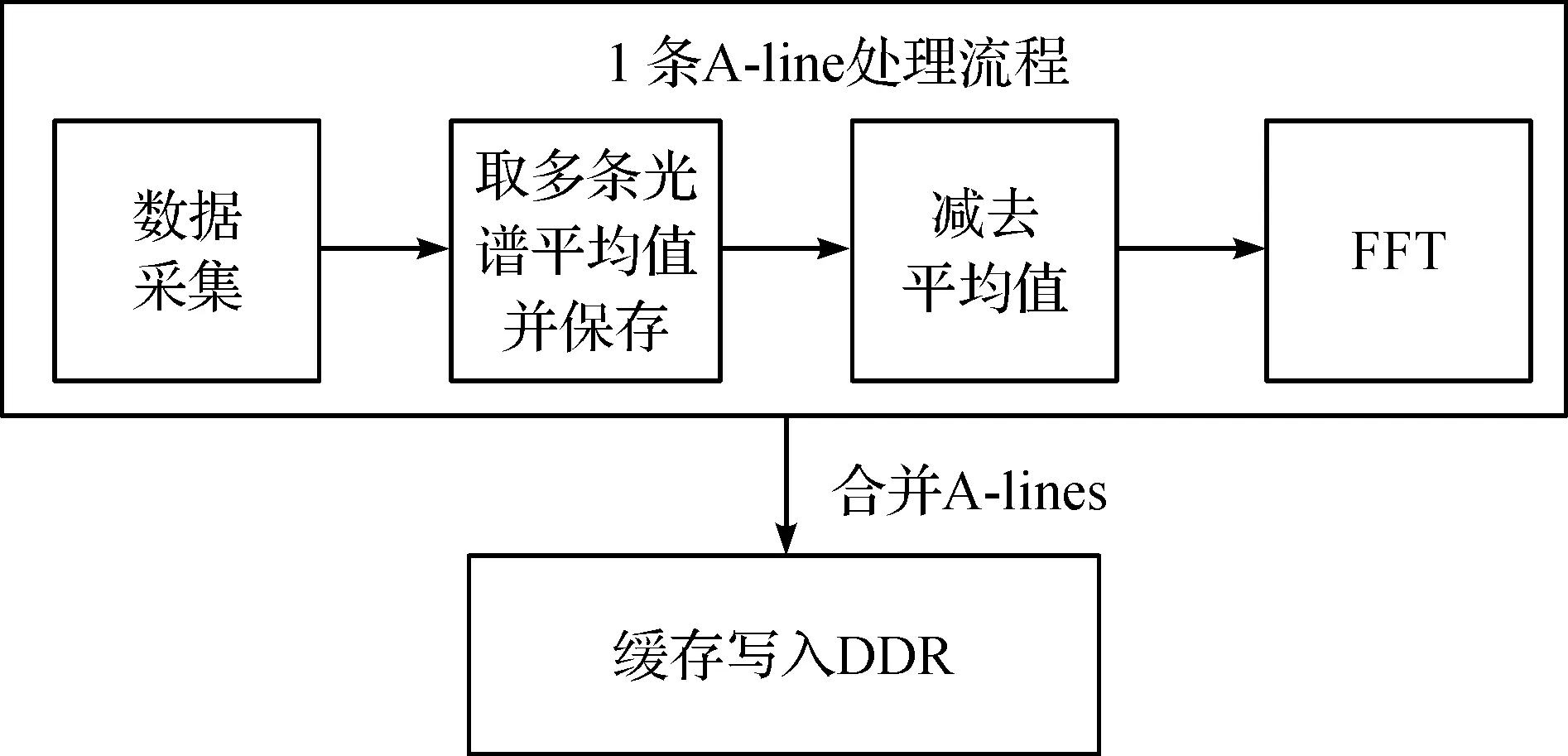

CCD采样数据是以波长为变量的,将其转为以波数为变量的数据,就需要对CCD数据进行插值操作。本模块中通过求平均的方式去除数据的直流噪声,对减直流后的数据进行插值操作,最后通过傅里叶变换获得样品深度信息。算法流程如图6所示。

图6 算法流程图Fig.6 Flow chart of the algorithm

1 条A-line中共含2 048 个像素点,单个像素点占用12 位的内存空间,在实际使用中用16 位的内存空间的数据类型来对每个像素点信息进行存储。算法在FPGA中的实现流程如图7所示,OCT数据缓存写入DDR中,以1 次B-scan数据作为数据处理单位。将500 组A-line数据累加依次存入深度为2 048的RAM1中,调用除法器获得光谱平均值,并依次存入深度为2 048的RAM2中,之后再次从DDR中读取此次B-scan数据,将每次A-line的数据存入深度为2 048的RAM3中,与RAM2中的光谱平均值作减直流。将减直流后的数据存入深度为2 048的RAM4和RAM5中,将插值系数存入深度为4 096的ROM1中,其中写入RAM4和RAM5的信号相差1 个地址。当ROM1中插值系数大于RAM4的读地址时,RAM4与RAM5的读地址增加。调用FPGA中DSP资源完成乘法操作,加上RAM5中的数据完成插值操作。插值后的数据通过调用FFT IP核完成最终的傅里叶变换操作。

图7 算法在FPGA实现流程图Fig.7 The process of achieving algorithm in FPGA

3.3 网络通信模块

网络通信模块主要利用内存映射机制及TCP/IP协议搬运已经预处理的数据到上位机中。数据拷贝到内核缓冲区之后,接着拷贝到socket缓冲区,之后从socket缓冲区拷贝到协议引擎,最后通过千兆网线将数据上传到上位机进行存储与处理。应用程序主要分为两部分:一是运行在下位机的客户端程序,作用为搬运PL端DDR中体数据到socket套接字;二是运行在上位机Linux系统下的服务器程序,作用为接收下位机发送的数据,两者进行通讯利用TCP/IP协议建立连接。

网络通信模块如图8所示,Linux应用程序访问PL端DDR时,会先利用系统调用mmap()进行内存映射,映射成功之后,Linux系统便可访问PL端内存。系统应用程序通过不断检测触发信号变化的方法判断PL端DDR缓冲区的状态,若检测到触发信号便进入缓冲区搬运数据。

映射之后应用程序利用系统调用write()搬运PL端缓冲区体数据到Linux下socket套接字中,过程中会先将数据拷贝到Linux内核缓冲区,用户空间应用程序会和操作系统共享这个缓冲区,这样系统内核和用户空间就不需要进行任何的数据拷贝操作。

图8 网络通信模块程序示意图Fig.8 Schematic diagram of network communication module

4 实验结果

系统的扫描工作流程如下所述:装置上电之后,初始化Zynq处理器控制模块,然后判断装置是否与PC机连接,如未连接则装置空闲(休眠),否则进一步判断同步触发模块是否有触发信号输入,如没有触发信号则装置空闲(休眠),否则Zynq处理器控制模块执行驱动时序,其他各模块比如CCD传感器模块、A/D转换模块、PS-PL交互模块和数据预处理模块等互相配合完成数据快速采集及预处理,之后对装置的传输进行确认,将缓存在DDR3的数据通过千兆网口模块,将数据传输至上位机。数据传输结束之后,装置返回判断是否有触发信号,为下一次采集做准备。系统最终采集手指数据线速率能到18 kHz,轴线分辨率为7 μm,横向分别率11 μm,探测深度达到1 mm。

系统实际工作中,由于TCK驱动电路带反向功能,所以FPGA端TCK原始输出信号反向输出。图9为使用逻辑分析仪抓取FPGA输出的CCD信号。在确保线阵CCD的信号时序与偏置电压都正确后,将线阵CCD连在电路板上,上电测试输出信号OS是否正常。测试使用较强的500~900 nm波长的光线照射线阵CCD的感光面,使其不断积累电荷信号,通过示波器观察输出波形。图10为示波器测出的CCD输出的OS信号。

图9 FPGA输出的CCD信号时序图Fig.9 The timing of CCD from FPGA

图10 输出信号OS实测波形Fig.10 The measured waveform of output signal OS

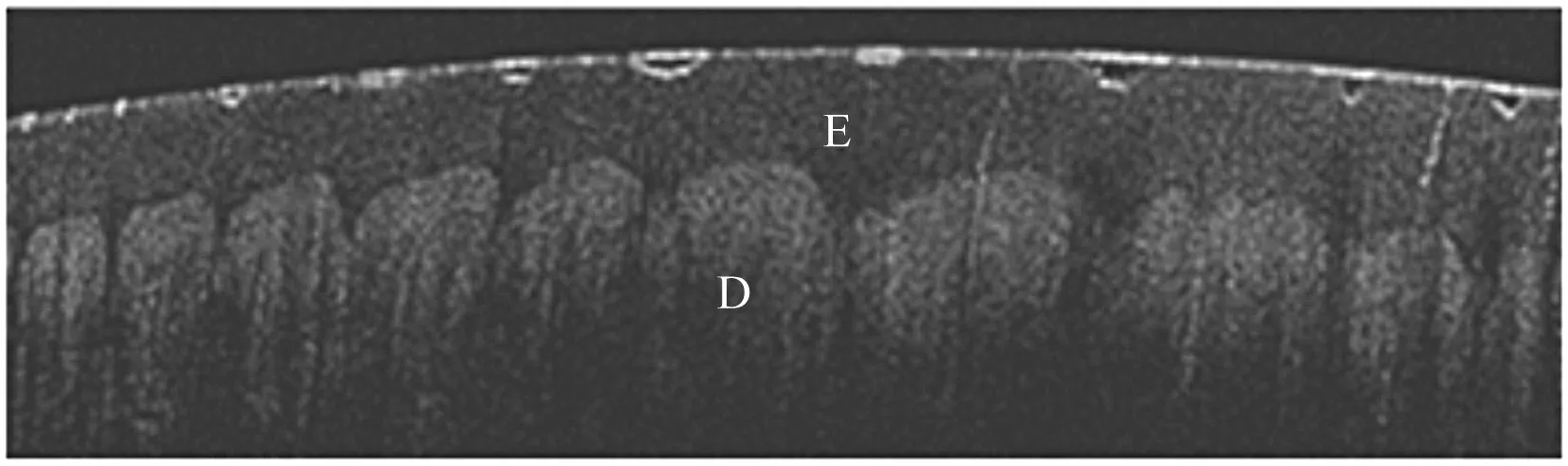

在完成AD9945的寄存器配置后,为AD9945提供相应的驱动信号,AD9945开始正常工作。图11为使用逻辑分析仪抓取FPGA输出的AD9945驱动信号,其中DATACLK信号上升沿需要在SHP上升沿和SHD下降沿之间,满足芯片正常工作要求。最终处理过后的数据通过千兆网口传给上位机,处理后的数据是一幅幅2D剖面图像数据的集合,可以获取手指皮下指纹。图12为手指OCT二维剖面图,其中E代表表皮,D代表真皮层。

图11 AD9945的相关双采样时序图Fig.11 The simulation of correlated double sampling timing

图12 手指OCT二维剖面图Fig.12 Two-dimensional cross-section of the finger OCT

5 结 论

在分析频域OCT原理的基础上,设计了基于Zynq芯片的手指OCT数据采集系统,以解决传统识别系统体积大、功耗大和扩展性差的问题。在分析Zynq芯片优势的基础上,提出了OCT数据采集系统的总体架构。在分析CCD及模数转换器驱动时序的基础上,提出了IL-P3和AD9945的驱动电路设计。逻辑分析仪抓取FPGA输出信号和信号OS的测量结果表明,笔者设计的时序发生器满足硬件驱动信号的要求。在分析Zynq芯片中PS与PL间内部交互的基础上,设计了基于AXI4总线的数据交互模块。基于对系统干涉光谱信号的分析,设计了基于FPGA的算法预处理模块。最后,实现了基于内存映射机制及TCP/IP协议网络的通信模块。笔者提出的设计方案减少了采集系统的电子器件数目,提高集成度的同时,简化了设计复杂度。