基于FPGA控制的按键模块的设计与实现

2019-05-09李莉

李 莉

(山西工程技术学院 信息工程与自动化系,山西 阳泉 045000)

0 引言

随着EDA技术的发展,大规模可编程逻辑器件FPGA[1]越来越广泛地应用到电子设计中,涉及电子、通信、航天、自动化等领域。FPGA以其具有体积小、功耗低、设计灵活、可靠性高的特点,已经成为电子设计的重要元件之一。键盘作为人机交互界面的重要组成部分一直是设计者关注的焦点。一旦对按键进行误判会影响整个系统的稳定性。 根据设计中按键数量的多少,按键电路分为单独按键、独立键盘和矩阵键盘。 本文就这三种不同按键形式给出了不同设计方案。

1 单独按键的设计

1.1 单独按键的去抖动原理

如图1(a)所示,当按键稳定按下去时,检测Z点为低电平,当按键抬起时,检测Z点为高电平。但是在按键实际按下到抬起的过程中,检测Z点电位会出现前沿和后沿的抖动。抖动时间一般为5 ms~10 ms。抖动的原因是按键是机械触点的开关,存在弹性作用。因为有抖动的存在,会导致控制器多次误读,认为按键多次按下,进而多次进入相应的子程序去执行,所以对于弹簧触点的机械开关,必须进行消抖处理。

图1 单个按键示意图

1.2 单独按键的去抖设计

常用的消抖的方法有RS触发器消抖[2]、软件消抖和基于有限状态机消抖[3,4]。本文单独按键的消抖采用基于有限状态机的方法。采用有限状态机设计的系统具有高速、高稳定性的特点。有限状态机分为Mealy型状态机和Moore型状态机。Mealy型状态机属于同步输出状态机,Moore型状态机属于异步输出状态机,Moore型状态机的输出只和当前状态有关系。本设计采用单进程Moore型状态机,组合逻辑和时序逻辑在同一个进程中,可以避免输出时毛刺的产生。

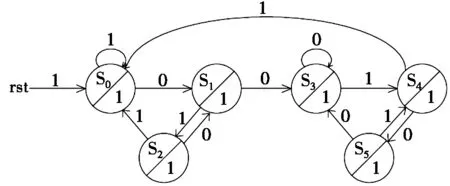

根据按键从按下到抬起的实际情况,如图1(b)所示,存在5个状态。S0:按键没有按下时的稳定的状态;S1:按键被按下的一瞬间的状态;S2:按键被按下抖动时的状态;S3:按键稳定按下时的状态;S4:按键松开一瞬间的状态;S5:按键松开抖动时的状态。图2为单独按键的状态转换图。rst为复位信号,高电平复位,clk为时钟信号,data为输入信号也就是图1(a)Z点的信号,q为输出信号,键稳定按下为低电平。

图2 单独按键状态转换图

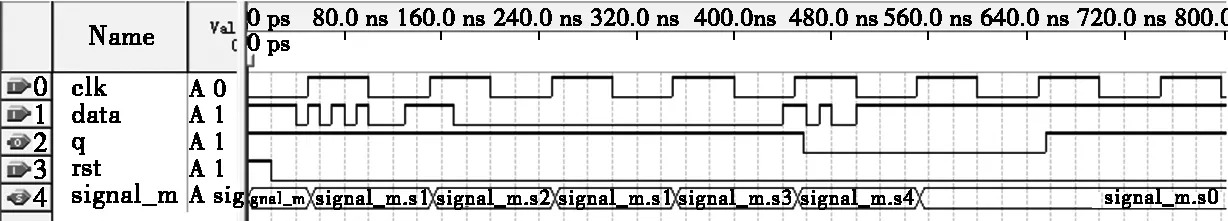

图3是模拟仿真单个按键从按下到抬起的过程。当rst为高电平时,FPGA复位,这时的状态为S0,在第一个clk时钟脉冲的上升沿输入为低电平,输出q为高电平,并且状态为S1;在第2个clk时钟脉冲的上升沿输入为高电平,输出q为高电平,并且状态为S2,表明在抖动过程中;在第3个clk时钟脉冲的上升沿输入为低电平,输出q为高电平,并且状态为S1;在第4个clk时钟脉冲的上升沿输入为低电平,状态为S3,表明按键稳定按下,但是输出q为高电平,这是由于是Moore型状态机,输出滞后一个clk脉冲,输出q在下一个clk时钟脉冲的上升沿才会变成低电平;在第5个clk时钟脉冲处是模拟仿真按键抬起时的抖动。采用单进程Moore型状态机可以有效避免毛刺出现。从图3看出单个按键的仿真波形结果良好。

图3 单个按键仿真波形

2 独立键盘的设计

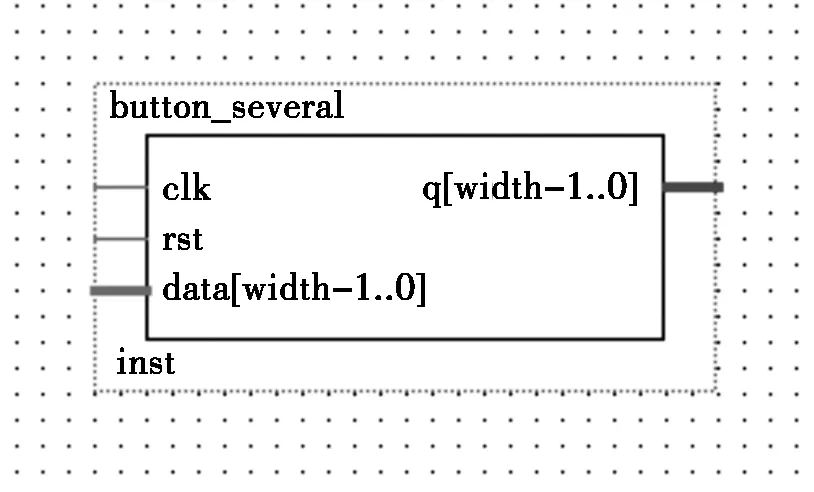

对于独立键盘的设计可以利用单独按键的设计结果,把单个按键当成一个组件在独立按键中使用。利用元件例化语句设计顶层设计实体。 witdth表示独立按键的个数,根据实际使用中键的个数,在程序中给witdth赋相应的初值,元件例化语句[5]如下。图4为独立键盘的设计实体。

aa: for i in 0 to width-1 generate

bb: button3 port map(clk=>clk,rst=>rst,data=>data(i),q=>q(i));

图4 独立键盘实体

3 矩阵键盘[6]的设计

对于按键数量较多的电子系统,键盘的设计多采用矩阵键盘,可以节省I/O口数量。4*4键盘往往作为标准矩阵键盘,所以本文以4*4键盘为例介绍矩阵键盘的设计。对于矩阵键盘的设计重点在于消抖动和得到键值。

3.1 矩阵键盘的消抖动

人在1s内最多可以按下按键10次,每次按键的时间最短为100 ms。在这100 ms里按键的抖动时间通常在5ms~10ms之间(不同种类按键的抖动时间略有不同),按键稳定按下的最短时间大约为50 ms。所以可以把键盘扫描周期设为40 ms,这样只要有键稳定按下(按下为低电平),低电平必然出现在时钟脉冲的上升沿,通过检测在时钟脉冲的上升沿上是否有低电平就知道有没有键按下。如果出现低电平,表明有键按下,如果出现高电平表明没有键按下。但是如果按键的抖动正好出现在时钟信号的上升沿处,虽然是小概率事件, FPGA也会认为按键已稳定按下一次,造成系统误操作一次。可以通过延时检测[7]的方法解决这一问题。在时钟脉冲的上升沿处检测到输入为低电平,有可能是抖动过程,所以延时10 ms后再检测一次,如果还是低电平表明有键按下,如果是高电平表明是抖动过程。具体实现方法为:如果所用FPGA的频率为50 MHz,经过分频[8]后,可降至1 KHz记为clk,周期为1 ms, 在clk的上升沿处检测是否有低电平出现,如果有,开始计数 ,若低电平持续的时间小于10个clkz周期,认为是按键的抖动,输出高电平。否则认为是有键按下,输出低电平。

图5 矩阵键盘消抖波形图

从图5可以看出,当输入高电平时,输出为高电平,当输入为低电平,并且持续10个clk周期时才输出低电平;这里可以根据不同按键抖动时间长短的不同更改程序中计数初值;如果输入的低电平持续时间小于10 ms,输出为高电平,认为是抖动状态。从图5看出,输出有毛刺,但是毛刺出现在时钟脉冲的上升沿后,并结束于下降沿之前,不影响后续对输出结果output的使用。在矩阵键盘的去抖动设计中通过元件例化语句把以上结果放入4*4矩阵电路设计中。

3.2 矩阵键盘扫描的设计

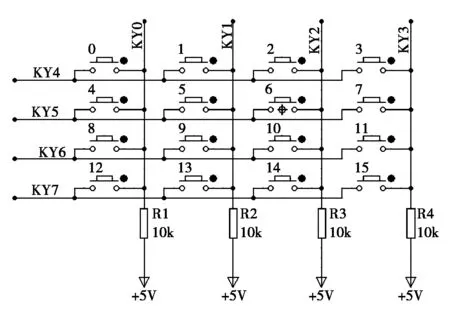

以4*4键盘为例,如图6所示,键盘的4条列线(输入)连FPGA的4根I/O线并接上拉电阻后接正电源,4条行线(输出)直接连FPGA的I/O线。FPGA逐行扫描[9],扫描码(KY4、KY5、KY6、KY7)依次为0111,1011,1101,1110。如果当前扫描码为0111,表示正在扫描第一行,如果列线KY3、KY2、KY1、KY0为1011,表示键值是2的键按下。如果列线KY3、KY2、KY1、KY0为1111,表示没有键按下。

图6 4*4键盘电路

图7 矩阵键盘仿真波形图

clk_1khz为频率为1 kHz的时钟信号,是消抖时使用的时钟信号。 clk_saomiao为频率25 Hz的时钟信号,是扫描时钟周期信号。这两个频率的信号都可以通过分频得到。keyout为行线输出, keyout 在每个扫描周期依次输出7(0111)、B(1011)、D(1101)、E(1110)。keyin为列线输入,keyin为F时表示无键按下,为7(0111)时,表示第一列有键按下。当扫描码为D,同时输入信号为7时,这个时候的键值为11,根据程序,扫描码在扫描时钟周期的上升沿出现,键值在扫描时钟周期的下降沿出现。仿真结果正确。

4 结语

电子系统中采用FPGA控制键盘实时性高并可以有效节省CPU的资源,优化电路设计。本文重点对于不同键盘采用不同设计方法,针对性强,对于单个按键和独立键盘采用有限状态机的方法消抖,采用单进程Moore型有限状态机可避免输出产生毛刺;对于矩阵键盘采用延时消抖的方法,对于不同的按键抖动时间不同,可以通过修改程序中的计数次数改变延时时间。这两种方法在实际使用中误差最小。两种设计结果均可作为子模块的形式,供上一级程序使用,可移植性好。