嵌入式图形处理器Alpha混合单元设计与实现

2019-05-05杜慧敏黄世远

杜慧敏, 黄世远, 郝 武

(西安邮电大学 电子工程学院, 陕西 西安 710121)

Alpha混合单元[1]是GPU完成图像混合功能的关键模块,处于图形渲染管线的末端,承担着前景像素与背景像素混合的作用。单一的Alpha混合方式会带来生硬的视觉体验。针对不同的绘制场景,GPU采用多样的混合方式以还原现实世界的视见关系[1],从而提高绘制场景的真实性。随着半导体工艺的进步和计算机图形学的发展,计算机合成图像的质量有所提高,图像的混合方式对场景真实性的影响更加突出。

在图像混合技术实现领域,国内研究多采用硬件实现单一混合方式、单一混合因子的混合设计或软件算法设计,没有硬件层面实现多种混合方式、多种混合因子的混合设计[2-5]。如在FPGA上实现了单一混合方式的Alpha半透明图像叠加算法[2];采用硬件实现了单一混合因子的三种混合方式[3]。国外学者则在混合结构方面进行了多种探索,如在图像混合前对多层图像进行随机分层的策略,但未详细介绍分层完成后混合的具体实现方式[6];通过使用选择器逻辑实现了图像合成电路,并在FPGA上进行了验证,但采用的混合方式单一[7];采用软件建模的方式实现了多层Alpha混合,改善了图像的质量同时降低了内存的需求[8];基于k-buffer的帧缓存架构,实现了多通道同时着色与混合的功能,但缓存架构占用太多存储资源,代价昂贵[9]。

针对嵌入式GPU[10]对Alpha混合功能的设计需求,本文通过分析混合单元支持的各种混合方式以及混合所需要的各类运算,确定数据格式,采用七级流水线结构,将多种混合操作均衡的分布到各流水级中,拟设计并实现一种支持6种混合方式的Alpha混合单元。

1 混合算法

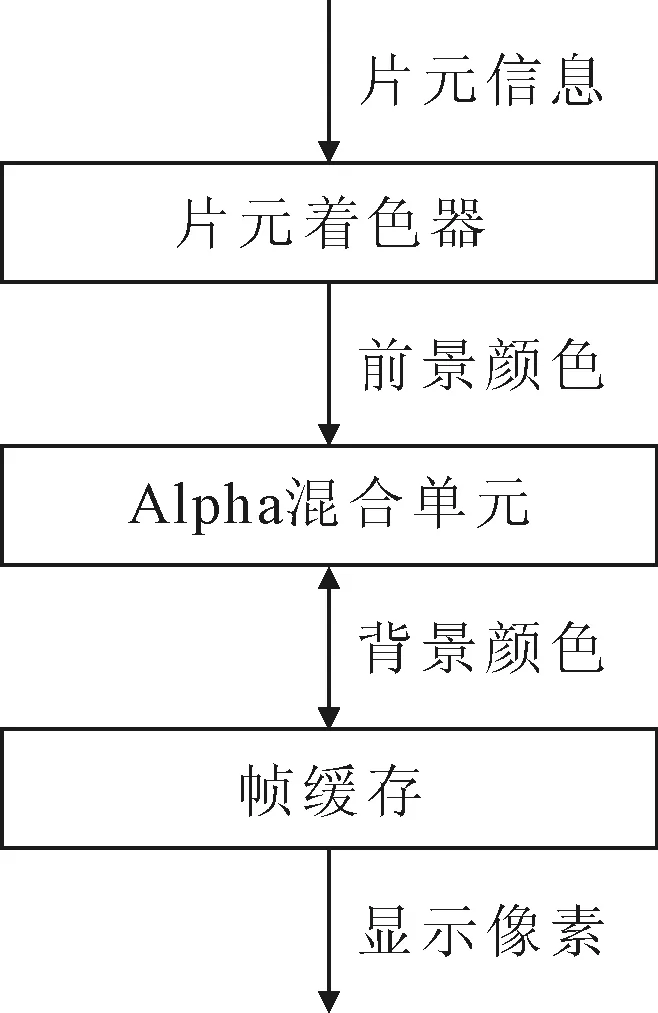

在图形渲染管线中,前景图像的像素信息由片元着色器产生,背景图像的像素信息存放在帧缓存中。在图像混合阶段,前景图像像素与背景图像像素在Alpha混合单元进行Alpha混合,产生新的背景图像信息,并被重新写回到帧缓存当中,用于显示。数据处理原理如图1所示。

图1 数据处理原理

Alpha混合实现了前景颜色与背景颜色的混合。在片元着色之前,需要根据片元的深度信息将片元从前到后或者从后到前进行排序,因此Alpha混合的目的就是将片元像素的颜色按照深度信息的前后顺序进行混合。

1.1 Alpha混合

根据深度信息的前后顺序可以将图形分为前景图形和背景图形,前景图形的像素颜色称为前景颜色或源颜色,背景图形的像素颜色称为背景颜色或目标颜色。为了使每个图形的颜色按照物理规律进行显示,每个图形像素都需要一个混合因子控制源颜色和目标颜色的比例,该混合因子称为Alpha通道或者不透明度。为了更加精确的量化颜色混合的线性比例,Alpha的分辨率要与颜色的分辨率相同。像素数据可表示为(R,G,B,A)。当Alpha值为0时,表示该像素完全透明;当Alpha值为1时,表示该像素不透明,该像素会完全覆盖其后的所有像素[11];当Alpha值介于0与1之间时,源颜色值和目标颜色值都会部分传递。

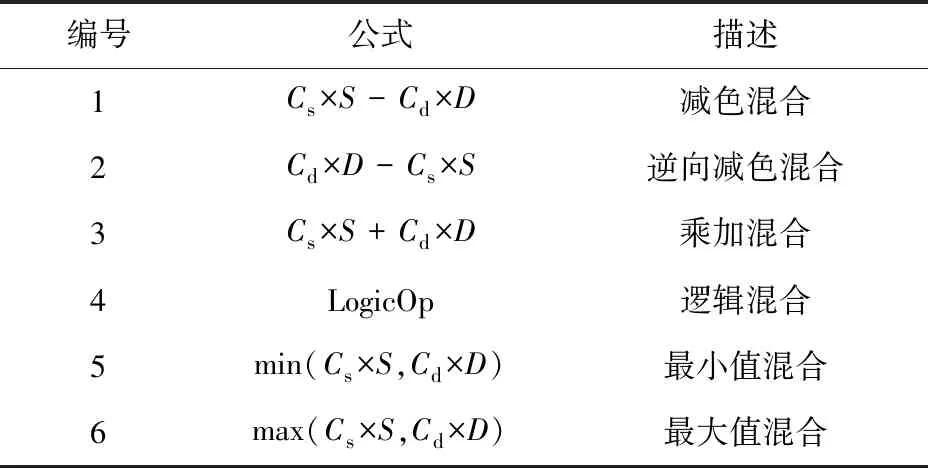

Alpha混合单元支持6种像素颜色混合模式,能够满足openGL和OpenGL ES常见的混合混合操作。其中,OpenGL常见的混合方式为表1 中的1~6项[12],OpenGL ES常见的混合方式为表1中的1~3项[13]。像素颜色混合模式类型如表1所示。

表1 像素颜色混合模式类型表

表1中,Cs和Cd分别表示源颜色和目标颜色,S和D表示源因子和目标因子,As和Ad分别是Cs和Cd的不透明度,Sa和Da分别为S和D的不透明度系数。LogicOp可以实现源颜色与目标颜色的逻辑混合,逻辑混合操作如表2[12]所示。

OpenGL ES等图形渲染软件支持多种混合因子的动态配置,因此GPU中Alpha混合单元也需要混合因子可以动态配置,配置信息如表3[14]所示。其中,[Rs,Gs,Bs,As]是从片段着色器中获取的源颜色,[Rd,Gd,Bd,Ad]是从帧缓存中获取的目标颜色,[Rc,Gc,Bc,Ac]是颜色常量[13]。

表2 逻辑操作组合类型表

表3 混合因子配置表

1.2 像素格式

Alpha混合单元支持多种像素格式输出,具体的像素格式如表4所示。

混合因子需要支持多种配置(混合因子配置信息详见表3),所以混合因子需要支持多种数据选择,混合因子支持的数据类型如表5所示。

表4 像素格式

表5 混合因子支持的数据类型

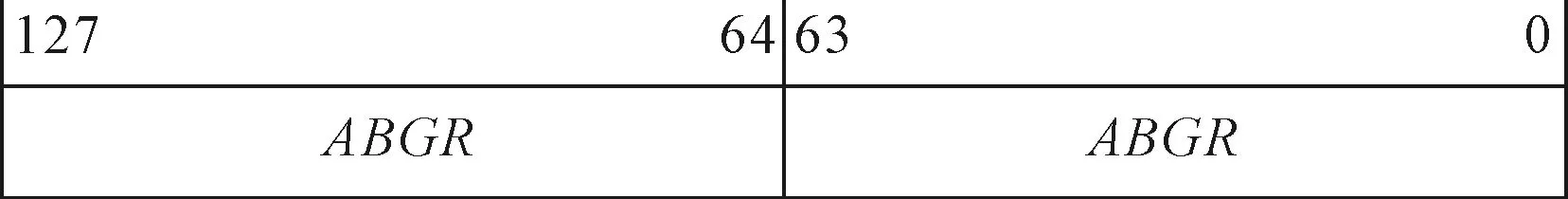

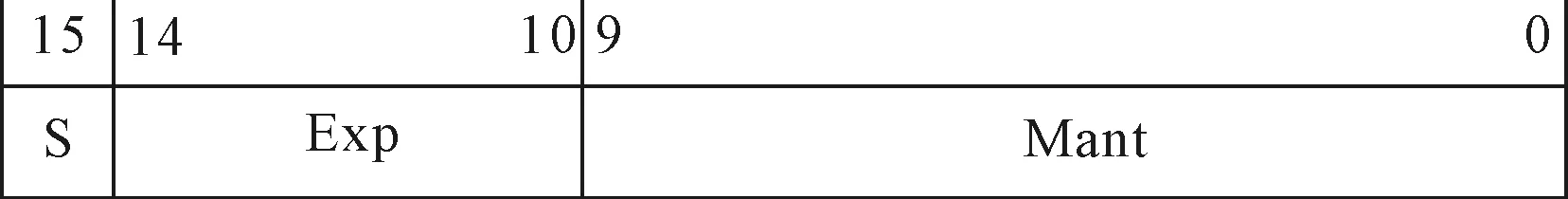

1.3 数据格式

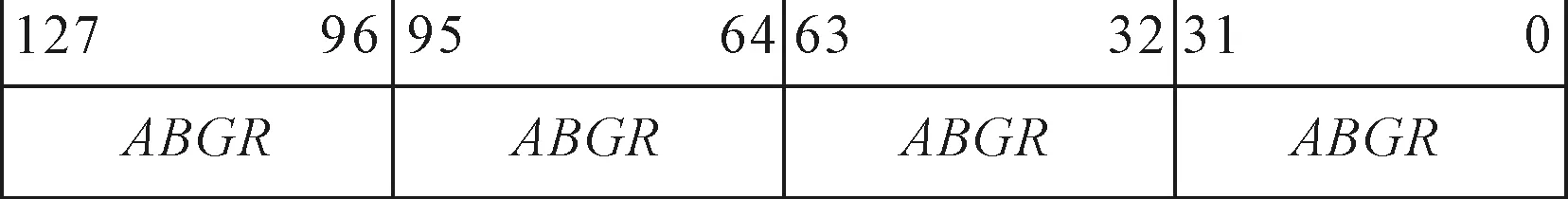

嵌入式GPU需要支持半精度浮点数据和8位定点数据。为了提升Alpha混合单元的吞吐率,采用128位数据格式,即单次处理2个半精度浮点格式像素数据或单次处理4个定点格式像素数据。128位半精度浮点数格式如图2所示。半精度浮点数格式如图3所示。128位输入数据包含两组半精度浮点像素数据,每个像素数据位宽为64位,每个颜色通道的位宽为16位。当像素数据为定点数格式时,数据格式如图4所示。

图2 128位半精度浮点数像素数据格式

图3 半精度浮点数格式

图4 128位定点数像素像素数据格式

当输入数据为定点数类型时,128位输入数据包含4组定点像素数据,每个像素数据的位宽为32位,每个颜色通道的位宽为8位。

2 Alpha混合单元的设计与实现

为了提高设计的工作频率,Alpha混合单元采用流水线结构。流水线中延迟最大的一级流水线的路径(即关键路径)长度决定了流水线的时钟频率和吞吐率[14]。增加流水线级数可以提高电路的工作频率,但也会增加时序单元,增大设计面积,并且增大流水线级数也会增大Alpha混合单元的时钟开销,降低混合吞吐率。因此设计合理的流水线级数和关键路径长度以达到工作频率与面积之间的平衡,成为设计的关键。

GPU支持的显示分辨率最高需要1 600×1 200×60 Hz。由此推算,当完成单次混合时,Alpha混合单元的像素吞吐率需要达到1 600×1 200×60 (pixel)/s,约为115.2 M(pixel)/s。

复杂场景下需要进行多层次的前景图像与背景图像的混合。以复杂场景平均需进行3次混合为设计标准,则3次混合像素吞吐率为单次混合时吞吐率的3倍,需要达到345.6 M(pixel)/s。

若同时处理2个半精度浮点像素数据,当流水线处理像素数据足够多时,每个时钟周期都可处理完成2个像素数据。因此电路的工作频率需达到164.79 MHz才可支持设计所需吞吐率。

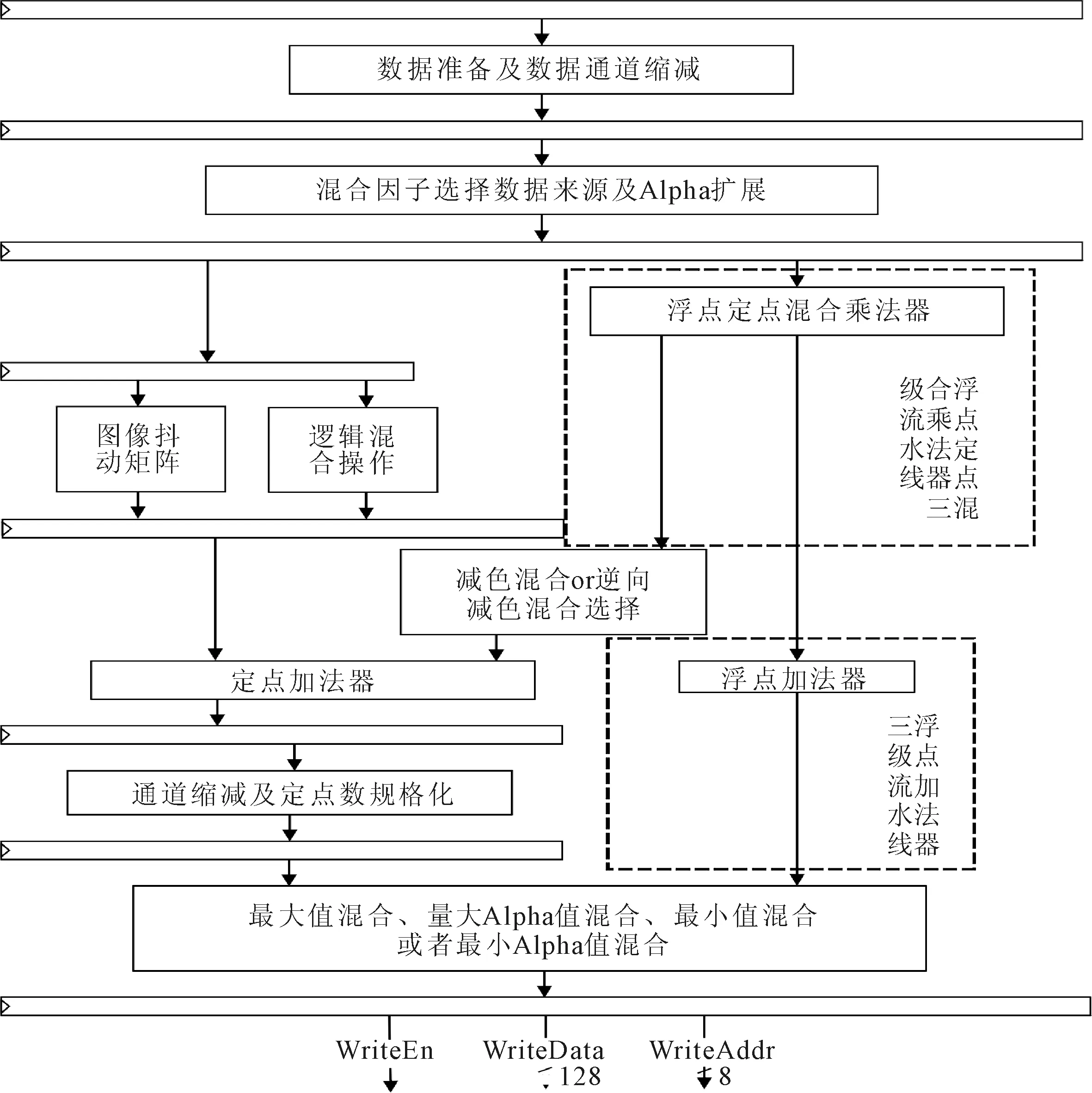

基于上述设计指标,Alpha混合单元采用了7级流水线设计,流水线结构如图5所示。

第1级数据准备。根据需要输出的像素格式(详见表4)对数据进行通道缩减,减少中间过程的运算量。

第2级混合因子选择数据类型(详见表5),并根据使能选择是否进行Alpha扩展,当进行Alpha扩展时,电路实现表3中第7~10项以及第14、第15项中的某一项,否则,则实现剩余项功能。

第3级~第5级通过浮点定点混合乘法器完成源颜色与源因子相乘以及目标颜色与目标因子相乘的功能,在第5级时产生乘法结果。

第4级逻辑混合操作(详见表2),并根据像素位置选择抖动矩阵元素,以备第5级所用。

第5级源颜色与源因子相乘的结果、目标颜色与目标因子相乘的结果以及抖动矩阵元素相加,定点加法操作本级产生结果,浮点加法操作第7级产生结果。

第6级对定点混合结果进行通道缩减及规格化以保证定点数精度。

第7级浮点加法计算完成后,对浮点、定点混合结果分别进行最大值混合或者最小值混合,根据混合方式选择相应的混合结果并将结果输出。

图5 七级流水线结构

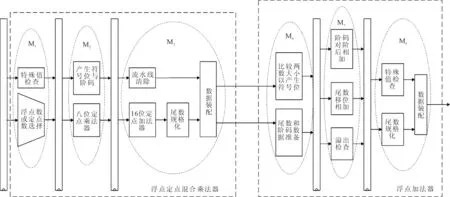

由图5可以看出,从第3级开始流水线结构可以分成两部分,左侧部分为顶层流水线结构;浮点运算的复杂性导致右侧部分需要将浮点定点混合乘法器和浮点加法器各分3级流水线完成,如图6所示。其中组合逻辑块M1、M2和M5分别构成一个路径组,M3和M4共同组成一个路径组,M6与第7级后续组合逻辑块构成一个路径组。每一个路径组将产生一个关键路径。通过对浮点定点混合乘法单元与浮点加法器的优化,电路中所有关键路径的长度都小于预期时钟周期的长度。

图6 浮定点混合乘法器和浮点加法器流水线结构

若分别实现除逻辑混合方式外的其余5种混合方式,则单一颜色通道混合需要10个乘法器和5个加法器。本设计采用流水线结构,将6种混合方式嵌入到各流水级中,复用了乘法器和加法器,单一颜色通道混合仅需2个乘法器和1个加法器就可完成除逻辑混合方式外的其余5种混合方式,减少了资源的使用情况。

3 电路功能验证

Alpha混合单元在FPGA开发板上进行系统级验证,采用OpenGL ES开发的场景在Xilinx的ZC706开发板SOPC(System-on-a-Programmable-Chip)对Alpha混合单元进行测试。测试图像为标准测试图形犹他壶与光照环的图像混合,效果如图7 所示。

可以看出,图7(a)没有进行混合,前景图形犹他壶的Alpha为1即不透明,犹他壶已将光照环全部遮挡;图7(b)为乘加混合方式,前景图形犹他壶Alpha为0.7,背景图形光照环Alpha为0.7;图7(c)为减色混合方式,前景图形犹他壶Alpha为0.7,背景图形光照环Alpha为0.3;图7(d)为减色混合方式,前景图形犹他壶Alpha为0.3,背景图形光照环Alpha为0.7。

与乘加混合方式相比,减色混合方式和逆向检核混合方式混合后的Alpha值均有所降低,导致图像亮度有所降低。整体上,本设计面向嵌入式设备的Alpha混合单元的混合效果与OpenGL ES实现的效果主观相同。

图7 测试效果

4 综合性能分析

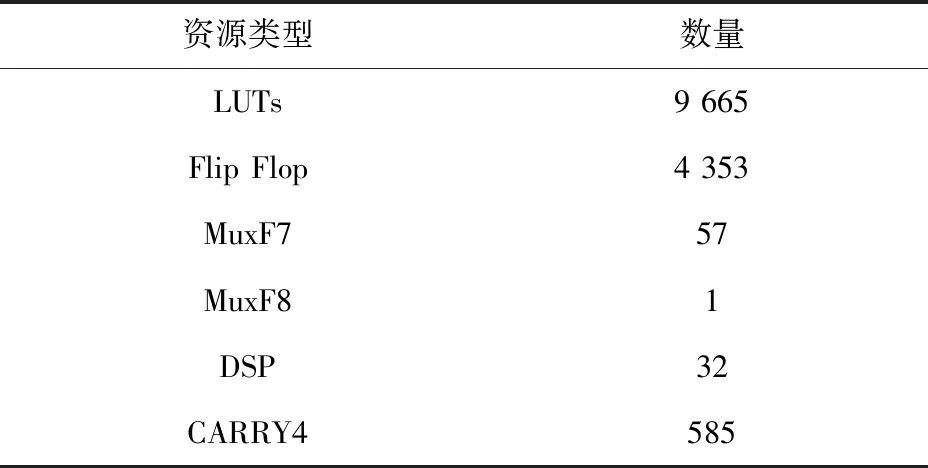

采用vivado工具,在ZC706开发板Zynq-7000系列FPGA芯片上进行综合,资源使用情况如表6所示。

单一颜色通道混合时,电路需要2个乘法器,设计采用RGBA四通道数据格式,并且同时处理4路定点数据或者2路半精度浮点数据,因此需要32个乘法器,占用32个DSP资源。然而,每个DSP中只使用了8×8的定点乘法器,其他资源并未使用。

表6 资源使用情况统计表

通过vivado工具综合,电路的工作频率f达到178 MHz。当Alpha混合单元进行单次前景图像与背景图像混合时,流水线最大吞吐率[14]为

(1)

实际吞吐率表明,对于m段数据流水线,若各段时间均为T,连续处理n个数据,除第一个数据需要m·T外,其余(n-1)个数据需要(n-1)T,故实际吞吐率Rp[15]为

(2)

当n≫m时,Rp≈Rpmax。

设计同时处理2个半精度浮点像素或同时处理4个定点像素,因此,当进行半精度浮点数混合时,半精度浮点数像素数据的吞吐率为2倍的Rp,约为356 M(pixel)/s;定点像素数据的吞吐率为4倍的Rp,约为712 M(pixel)/s。以复杂场景需要3次Alpha混合为例,则分辨率为1 600×1 200×60 Hz的数据吞吐量需求为345.6 M(pixel)/s,完全满足图形处理器的显示需求。

5 结语

设计并实现了一种应用于嵌入式GPU的Alpha混合单元,有别于其他实现单一混合方式的Alpha混合单元,该设计实现了6种混合方式的Alpha混合单元,可以支持OpenGl ES 软件下所有的混合操作。采用七级流水线结构,使用vivado工具综合,结果表明,电路的工作频率为178 MHz;以复杂场景平均需进行3次混合为设计标准,该 Alpha混合单元的半精度像素吞吐率达到356 M(pixel)/s,定点像素数据吞吐率达到712 M(pixel)/s,可以满足显示分辨率最高达到1 600×1 200×60 Hz的显示要求。