一种异构处理架构的PLC集成安全控制系统结构设计

2019-05-05李明时尹震宇廉梦佳王春晓

李明时,马 跃,尹震宇 ,廉梦佳,王春晓

1(中国科学院大学,北京 100049)2(中国科学院 沈阳计算技术研究所,沈阳 110168)

1 引 言

随着科技快速发展,在现代机器设备控制系统的功能安全技术中,PLC控制系统的功能安全正在向着集成化的方向发展.一些特种机械设备在运行过程中要求较高的安全性,对于PLC控制系统的要求也随之提高.传统的PLC控制系统因为自身没有建立更加全面和先进的集成化安全机制,在工序相对复杂的生产过程中发生运行故障的概率会增大,造成财产损失以及操作人员受伤的风险会增加[1],所以传统的PLC控制系统在当前已经不能满足更高要求生产设备的运转以及生产安全性和控制可靠性的要求,PLC集成安全控制系统应运而生.

在硬件结构上,传统的PLC控制系统以单处理器结构为主,由于处理器等大规模集成电路芯片在受到电磁干扰时容易发生复位、死机等处理器执行异常情况[2],在应用于工业控制和工业自动化等具有强电磁或其它外力干扰特点的领域中时,可能会发生控制设备和控制系统出现执行故障、结构损坏或操作人员受伤等其它危险[3],引起巨大损失.

针对上述可靠性及安全性问题,目前主要采用基于对称双处理器结构的安全PLC结构,或采用双PLC系统建立冗余控制系统进行解决,方案价格昂贵并且构建复杂,实现复杂度较高.

本文提出的异构处理架构的PLC集成安全控制结构具有实用性强、结构复杂度低以及良好的抗干扰性等特点,可以有效保证PLC控制系统安全有效运行.

2 集成安全要求下的安全架构

非安全架构的PLC控制系统在出现执行故障时缺少完善先进的集成安全机制对运行错误进行处理.

传统的PLC控制系统处理芯片的数量为一个或多个,但是多个处理芯片是协同的工作方式,对事先编写的逻辑程序往往只进行一次处理[4],两个或多个处理器之间并没有进行交叉检测.而使用异构处理架构对PLC控制系统进行设计,可以实现对PLC程序的冗余执行并且降低系统执行错误对工业生产造成的影响.

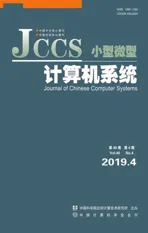

根据实际控制需要以及安全架构的实现复杂度,本文设计的异构处理架构的PLC集成安全控制结构选择了基于具有监控功能的“二选一”安全架构进行实现.“二选一”安全架构如图1所示.

图1 “二选一”安全架构图Fig.1 Diagram of 1oo2D safety architecture

具有监控功能的“二选一”安全架构内部设计有两条可以独立执行逻辑指令且具有监控功能的“一选一”处理通道,两条“一选一”处理通道之间是通过并联的方式连接在一起的[5],只要两条通道的其中一条功能正常,就可以保证整个控制系统正常运转.当控制设备在运行过程中发生一次故障时,系统可以降级为具有监控功能的“一选一”安全架构继续执行逻辑指令[6].两条独立的“一选一”处理通道相互之间可以进行通信,从而判断另一条处理通道的执行状态.

3 PLC控制系统结构设计

针对传统PLC系统在实际应用中的缺点与不足,本文通过设计一种异构处理架构的PLC集成安全控制结构,在使用单一ARM处理器的传统PLC控制系统中,增加了一个设计在FPGA芯片上的RISC辅助处理器,构成异构处理架构,对PLC控制系统的整体安全性进行了提升[7],实现了安全逻辑控制.

3.1 PLC控制系统总体架构

本文中PLC集成安全控制系统总体架构是基于具有监控功能的“二选一”安全架构进行设计的,两条处理通道是非对称的.PLC控制系统正常状态下执行所有PLC逻辑指令的处理器为ARM主处理器,设计在FPGA芯片上的RISC辅助处理器负责与主处理器同步独立执行PLC实时逻辑指令,执行完成的指令结果存储在缓存器中,输出信号通过安全诊断单元进行检验.PLC控制系统结构如图2所示.

当主处理器在执行逻辑指令的过程中出现故障,RISC辅助处理器将接替主处理器继续执行实时逻辑,同时主处理器的自身运行状态将被看门狗电路1中的复位电路重置.主处理器恢复正常执行状态后,可以在接下来的周期内读取缓存器中的指令结果并继续执行逻辑指令.

图2 PLC控制系统总体架构图Fig.2 Diagram of PLC control system architecture

如果对应的复位电路连续五次对主处理器进行重置,但是依然无法使得主处理器恢复正常执行状态,PLC系统将报错,同时执行安全保护输出数据.

PLC控制系统总体架构具有如下特征:

1)采用双重独立通道.设计有两条独立执行逻辑指令的并联通道,两条通道并行执行同一个指令程序.

2)使用安全输入输出.每一个外部输入信号同时传入两条执行通道中,对PLC逻辑指令进行同步执行.PLC控制系统输出通道采用冗余架构,可以精确控制每一个节点的输出信号[8],从而确保输出的可靠性.

3)设计有安全监控单元.主处理器和辅助处理器之间设计有安全监控单元[9].安全监控单元在控制系统运行的过程中接收主处理器和辅助处理器的心跳信号.如果其中一个处理器在本周期内发生执行错误,则安全监控单元将控制问题处理器对应的复位电路对其进行重置.

3.2 PLC控制系统执行流程

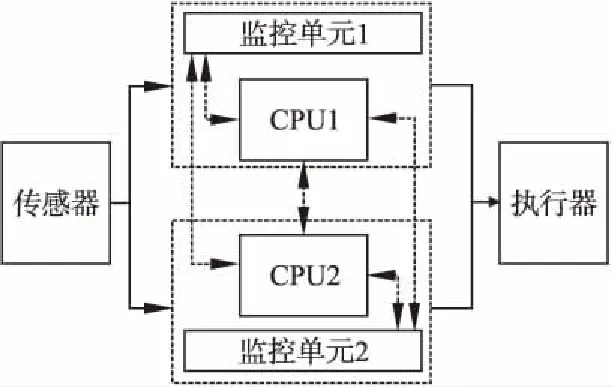

在PLC控制系统工作正常的情况下,ARM主处理器会执行全部的PLC逻辑指令,RISC辅助处理器只冗余执行PLC实时逻辑,主处理器和辅助处理器执行完成的实时逻辑执行结果存储在缓存器中.RISC辅助处理通道工作流程如图3所示.

在PLC控制系统运行过程中,安全监控单元会对ARM主处理器运行状态进行监测.在每一个执行周期内主处理器会向安全监控单元发送自身心跳数据,也就是向对应的倒计时器1发送归零信号.如果安全监控单元可以正常接收心跳数据,说明本周期主处理器工作正常.

如果安全监控单元不能正常接收ARM主处理器的心跳数据,说明主处理器在本周期执行PLC逻辑时出现故障,安全监控单元会控制对应的看门狗电路1向主处理器发送复位信号1进行重置.

当主处理器出现故障时,RISC辅助处理器会继续执行PLC实时逻辑,可以维持PLC控制系统的正常运行.如果看门狗电路1对ARM主处理器连续进行五次复位后,依然无法恢复其正常的运行状态,那么系统将执行安全保护输出数据.

当RISC辅助处理器出现故障时,主处理器可以继续正常执行全部PLC逻辑,保持控制系统的正常运行.如果看门狗电路2对RISC辅助处理器连续进行五次复位后,依然无法恢复其正常的运行状态,那么系统将执行安全保护输出数据.

图3 RISC处理通道执行流程图Fig.3 Workflow diagram of RISC processing channel

如果在ARM主处理器出现故障的同时,RISC辅助处理器也出现故障,那么系统将发出报错指示信息,并直接执行安全保护输出数据.

3.3 FPGA芯片设计

FPGA芯片的功能是对ARM主处理器和RISC辅助处理器进行监测,存储PLC实时逻辑的执行结果以及对输出选择进行控制.FPGA芯片包含以下部分:

高中化学教学并非是盲目开展的,每个课时都是有对应的教学目标的,但是过去在明确教学目标时,目标的构建十分混乱和零散,这便致使了化学教学工作无法有序开展.该种状况在运用系统思维理论得到了有效改善.基于系统思维理论下,教师在构建教学目标时,会从教学整体着手,通过细致分析教学内容与任务,找出课时间的联系,随后依据该联系构建教学目标,这样一来,每个课时的教学目标间存在内在关联,全部教学目标都能融合到一起汇聚成一个整体,如此教师在具体教学中便能够保证教学效果达到最佳.

1)RISC辅助处理器的作用是执行PLC实时逻辑.

2)安全监控单元的作用是接收ARM主处理器和RISC辅助处理器的心跳数据.如果出现一个执行周期内没有收到任意一个或两个处理器心跳数据的情况,则控制故障处理器对应的看门狗电路对其进行复位操作[10],同时向输出选择控制器发送输出选择信号.

3)缓存器的作用是存储ARM主处理器和RISC辅助处理器对于PLC实时逻辑的执行结果.在处理器发生故障进行重置后,可以利用缓存器对已经存储的PLC实时逻辑执行结果进行同步.

4)看门狗电路的作用是当接收到安全监控单元发出的控制信号时,向自身对应的主处理器或辅助处理器发送复位信号将其进行重置.

5)锁存器的作用是存储安全保护输出数据,并根据安全监控单元的要求将其输出至输出选择控制器.

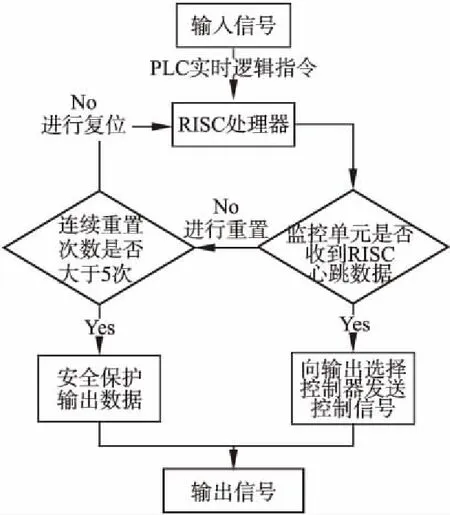

安全监控单元内部包含了两个倒计时器、两个看门狗电路以及三个逻辑.倒计时器用于接收ARM主处理器和RISC辅助处理器的计时归零信号,之后进行判断是否需要向看门狗电路发送控制信号.安全监控单元内部的三个逻辑分别是“或非”、 “与”和“非”逻辑.

安全监控单元通过接收来自ARM主处理器或RISC辅助处理器的计时归零信号,执行倒计时器的归零操作.通过安全监控单元的内部逻辑进行输出判断,并发送输出选择信号至输出选择控制器.安全监控单元结构如图4所示.

图4 安全监控单元结构图Fig.4 Structure diagram of safety monitoring unit

当倒计时器1可以按执行周期正常接收计时归零信号1时,输出选择控制器将选择ARM主处理通道进行输出[11].如果倒计时器1无法正常接收计时归零信号,而倒计时器2可以正常接收,则输出选择控制器将选择RISC辅助处理通道进行输出.否则将选择输出安全保护输出数据.

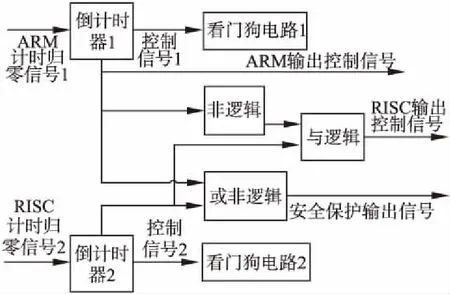

3.4 输出选择控制器的设计

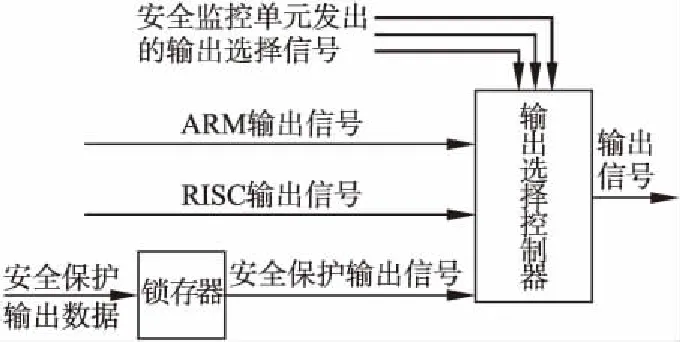

输出选择控制器通过安全监控单元发送的输出选择信号,完成对ARM主处理器输出信号、RISC辅助处理器输出信号以及安全保护输出信号的输出选择.输出选择控制器工作原理如图5所示.

图5 输出选择控制器工作原理图Fig.5 Operational principle diagram of output selection controller

首先,输出选择控制器接收三组输出信号,分别来自ARM主处理器、RISC辅助处理器以及锁存器.

同时,输出选择控制器接收安全监控单元发送的输出选择信号.

最后,根据安全监控单元发送的输出选择信号,将被选择的对应输出信号发送到PLC控制系统输出端.

4 测试验证

PLC集成安全控制系统测试包括实时逻辑执行时间测试、任务管理周期测试以及任务管理抖动测试三部分.

4.1 测试环境

异构处理架构的PLC集成安全控制系统测试平台为滚齿机专用的LT-H10数控系统.测试所使用的处理器为ARM Cortex-A8高性能处理器,FPGA使用的测试芯片为Xilinx SPARTAN-3E XC3S500E芯片.

4.2 实时逻辑执行时间测试

4.2.1 测试方案

在PLC逻辑扫描与I/O管理模块执行之前,首先获取当前的系统时间tmp_time1,在逻辑扫描与I/O管理模块执行之后,获取系统当前时间tmp_time2,通过tmp_time1和tmp_time2的差计算出本周期实时逻辑的执行时间是多少.用于测试的PLC逻辑指令长度为600行左右,设定每1000个执行周期获取一次PLC控制系统实时逻辑的执行时间.

4.2.2 测试数据

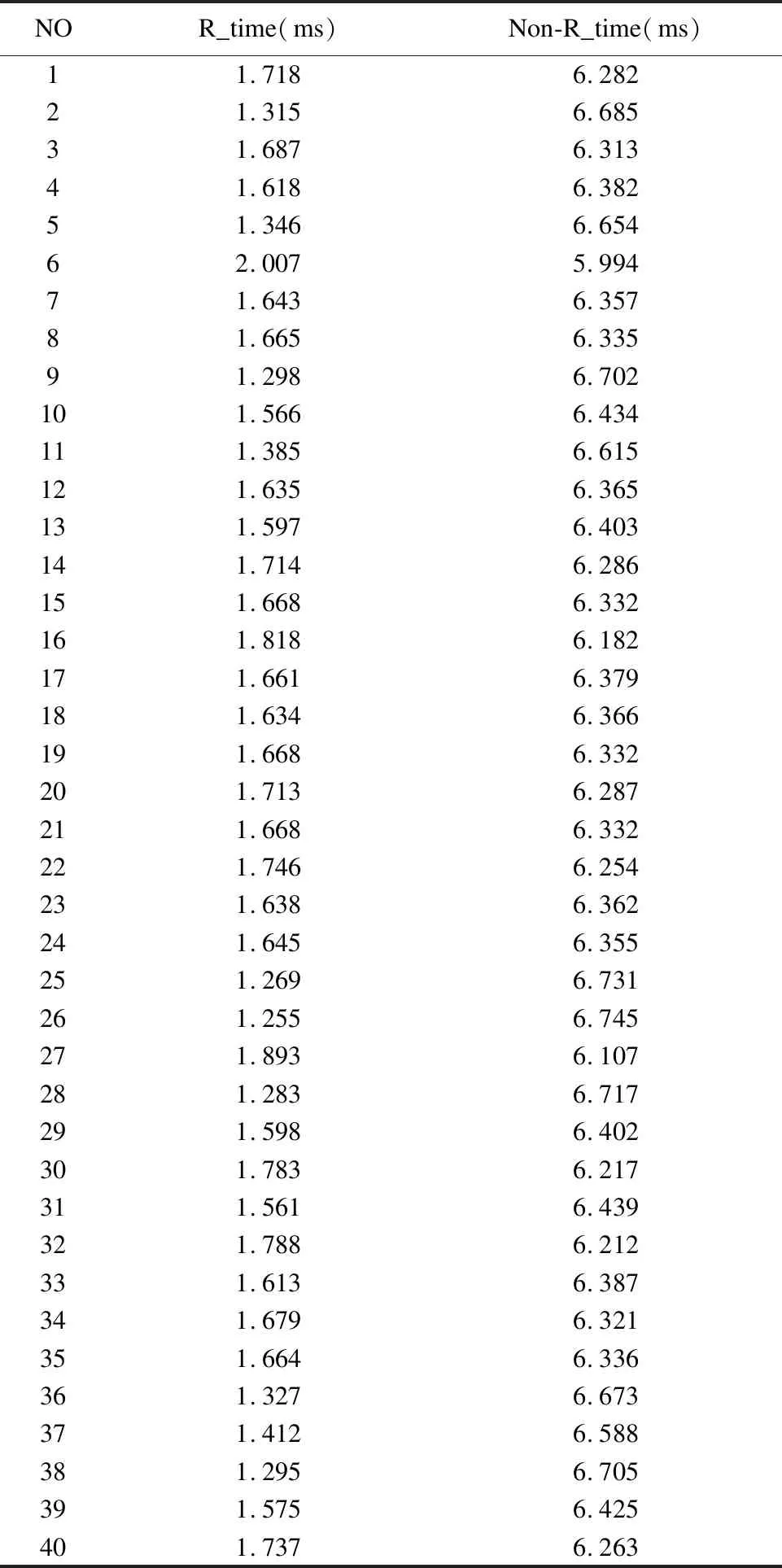

R_time为实时逻辑执行时间,Non-R_time为一个周期内留给非实时逻辑的执行时间,系统内设定的执行周期为8毫秒.40组逻辑执行时间数据如表1所示.

表1 PLC逻辑执行时间数据表

Table 1 Data of PLC logical execution time

NOR_time(ms)Non-R_time(ms)11.7186.28221.3156.68531.6876.31341.6186.38251.3466.65462.0075.99471.6436.35781.6656.33591.2986.702101.5666.434111.3856.615121.6356.365131.5976.403141.7146.286151.6686.332161.8186.182171.6616.379181.6346.366191.6686.332201.7136.287211.6686.332221.7466.254231.6386.362241.6456.355251.2696.731261.2556.745271.8936.107281.2836.717291.5986.402301.7836.217311.5616.439321.7886.212331.6136.387341.6796.321351.6646.336361.3276.673371.4126.588381.2956.705391.5756.425401.7376.263

4.2.3 测试结果分析

通过PLC实时周期逻辑执行时间的曲线图可以看出,在抓取的40次实时周期逻辑执行时间中,执行时间在1.255ms至2.007ms范围内,波动幅度为0.752ms.实时逻辑执行时间如图6所示.

图6 实时逻辑执行时间图Fig.6 Diagram of real-time logic execution time

4.3 任务管理周期及抖动测试

4.3.1 测试方案

PLC控制系统默认的任务管理周期为8毫秒,所以将输出的本周期PLC任务管理时间与8毫秒作比较,两组时间的差值为当前周期PLC任务管理的时间抖动值.

在执行PLC逻辑扫描函数之后,对执行周期数进行条件判断并输出符合判断条件周期的PLC任务管理时间.抓取PLC控制系统100个执行周期的时间数据,通过分析一定范围的时间数据可以判断出PLC控制系统当前运行是否稳定,能否达到可靠控制以及安全生产的标准.

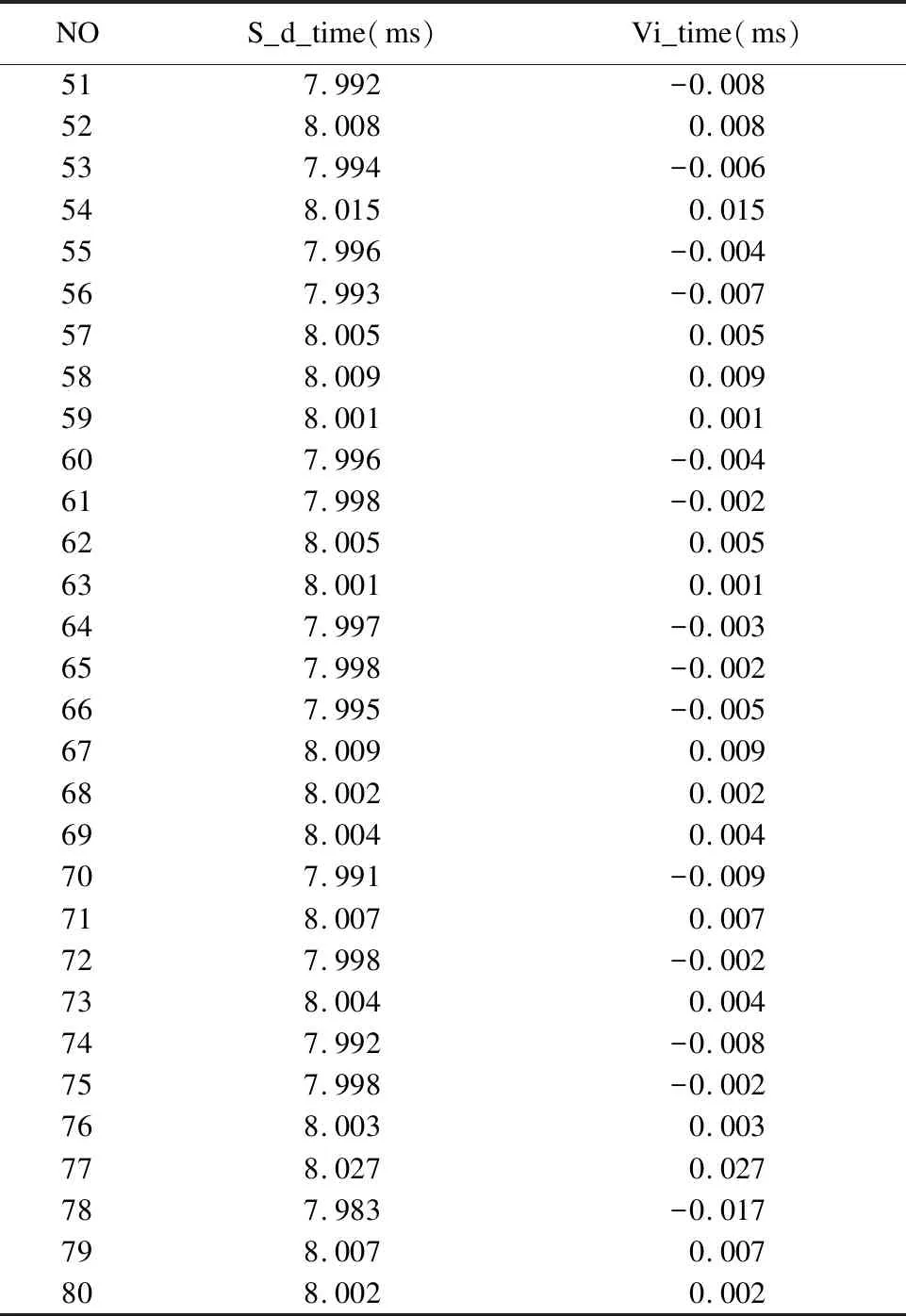

4.3.2 测试数据

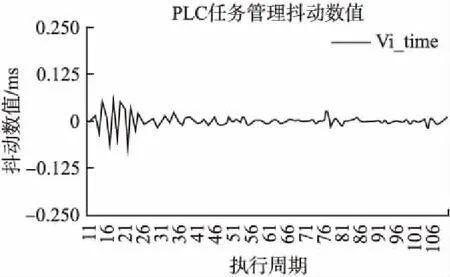

S_d_time为任务管理时间,Vi_time为当前周期任务管理的抖动数值.51-80周期的PLC控制系统任务管理周期及抖动值如表2所示.

4.3.3 测试结果分析

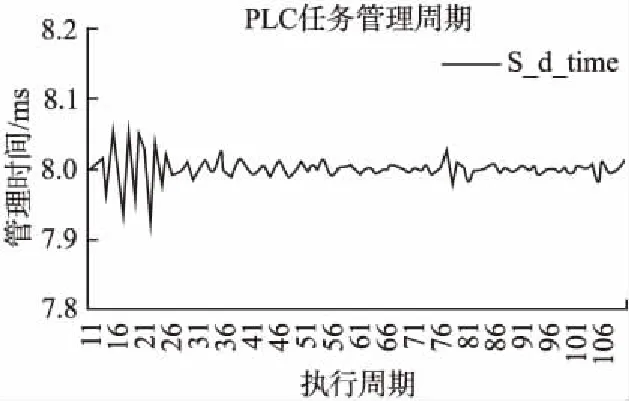

1)任务管理周期

通过PLC任务管理周期曲线可以看出,自PLC系统的第11个执行周期开始抓取PLC任务管理周期及抖动值,PLC控制系统100个执行周期的任务管理时间的范围是7.924ms至8.059ms.任务管理周期曲线如图7所示.

图7 任务管理周期曲线图Fig.7 Diagram of task management cycle

2)抖动数值

通过抖动数值曲线可以看出,自PLC系统的第11个执行周期开始抓取PLC任务管理抖动数值,PLC控制系统100个执行周期的任务管理抖动数值的范围是-0.076m至0.059ms.抖动数值曲线如图8所示.

4.4 测试结论

测试结果表明,PLC集成安全控制系统任务管理周期的时间范围在7.924ms至8.059ms,与默认的PLC控制系统任务管理周期8毫秒比较正负误差很小.任务管理周期抖动数值的时间范围在-0.076ms至0.059ms,时间的波动幅度在合理区间内.实时逻辑执行时间的范围在1.255ms至2.007ms,PLC集成安全控制系统对于实时逻辑的执行较快,不会对系统的运行造成不利影响[12],保证了生产的安全性.

表2 PLC任务管理周期数据表

Table 2 Test data of PLC task management cycle

NOS_d_time(ms)Vi_time(ms)517.992-0.008528.0080.008537.994-0.006548.0150.015557.996-0.004567.993-0.007578.0050.005588.0090.009598.0010.001607.996-0.004617.998-0.002628.0050.005638.0010.001647.997-0.003657.998-0.002667.995-0.005678.0090.009688.0020.002698.0040.004707.991-0.009718.0070.007727.998-0.002738.0040.004747.992-0.008757.998-0.002768.0030.003778.0270.027787.983-0.017798.0070.007808.0020.002

图8 抖动数值曲线图Fig.8 Diagram of jitter value

5 总 结

本文提出了一种异构处理架构的PLC集成安全控制系统结构设计,详细说明了PLC控制系统总体架构、PLC控制系统的工作流程以及FPGA芯片的内部设计等.

经过实际的性能测试,证明了异构处理架构的PLC集成安全控制系统可以正确执行PLC逻辑指令,准确安全控制外部仪器设备,在逻辑执行速度以及运行稳定性方面可以满足控制系统对于安全可靠控制的要求,适合实际应用于可靠控制及安全生产中.