Linux下PowerPC与FPGA通信接口的设计与实现

2019-04-28刘旸

文/刘旸

1 引言

现代社会对嵌入式双核系统的需求越来越大,同时Linux的巨大优势使得它在嵌入式领域的应用备受关注。本文中的硬件平台采用国产CCFC9000PA(一下简称C9000)嵌入式微处理器和JXCSX95T(以下简称95T)FPGA芯片,在嵌入式Linux系统下设计并实现了CPU与FPGA之间的硬件接口以及相应的驱动程序、测试程序,完整地实现并验证了该双核通信接口的设计。

2 硬件接口设计

C9000处理器有一个外部总线控制模块即External Bus Controlloer(EBC控制器)。CPU通过此存储控制器与外部设备进行数据的传输。目前能支持的外部设备包括ROM、EPROM、SRAM、Flash等。因此CPU可以经过EBC总线控制器与95T内部的RAM进行数据传输。C9000与95T的硬件电路如图1所示。

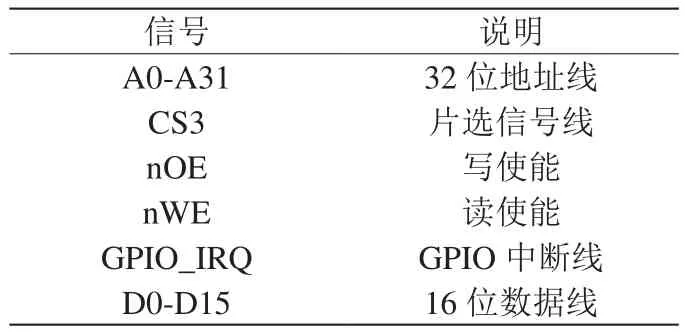

C9000通过外部总线与95T进行数据通信,即CPU发出相应的使能信号、读写信号以及地址信号,然后通过16位数据总线实现与FPGA内部SRAM的读写交互。另外,当95T有数据需要上报到C9000时,95T将产生中断通知C9000,C9000收到此中断后,发起对95T的读操作。控制信号说明如表1所示。

表1:控制信号说明

图1:C9000与95T的硬件连接

3 软件接口的设计与实现

3.1 驱动模块的设计

图2:驱动主要流程

图4:测试结果

在本系统中的软件设计主要是Linux下的FPGA设备驱动程序。在 Linux下,设备驱动程序位于应用程序和硬件之间,为二者传递数据、消息等。Linux应用程序可以通过设备驱动,把硬件设备当成一个普通文件进行操作。本驱动的主要功能有:

(1)注册FPGA设备、申请中断等;

(2)接收并处理来自FPGA的中断信号,然后接收FPGA发送来的数据;

(3)将CPU侧的数据写入FPGA内部RAM,即发送数据到FPGA设备。

驱动主要流程如图2所示。

3.2 驱动模块的实现

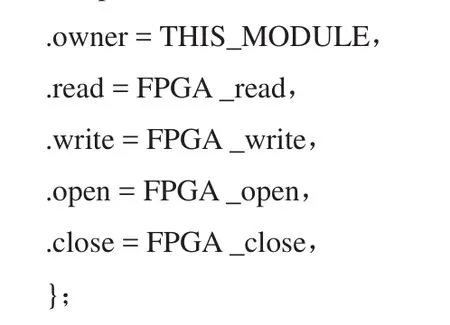

在Linux内核中,file_operations结构体是字符设备驱动的操作接口。本系统中的文件操作结构体定义如下:struct fi le_operations FPGA_fops = {

open主要用于提供驱动初始化,首先调用ioremap(addr,size)把95T的内部RAM映射到一个驱动程序可以访问的虚拟地址上 去:fpga_base=ioremap (FPGA_PHY_START,FPGA_PHY_SIZE)。其次,在打开设备时通过request_irq(GPIO_IRQ,FPGA_ISR,0,DEV_NAME,NULL)申请95T发送来的中断。close执行与open相反的操作。

在通过ioremap将95T内部RAM的物理地址映射成Linux虚拟地址后,驱动模块就可以通过标准的读写函数访问95T内部RAM了。读写函数原型如下:

unsinged int readw(void *address);

void writew(unsinged int data,void*address);

当应用程序通过read函数调用驱动中的FPGA_read时,如果FPGA设备暂无数据可供CPU读取时,进程进入休眠。如果95T有数据需要上报C9000,95T将通过下降沿中断通知C9000可以进行读操作了,open函数中注册的中断程序FPGA_ISR会接收此中断,完成读操作。读操作主要通过调用readw和copy_to_user将读取到的数据从内核空间传入用户空间,完成应用层的读操作。写操作与读操作类似,不再重复。

3.4 测试

测试方案如图3所示:测试程序使用pthread_create系统函数创建读写子线程,读线程负责接收来自95T的数据;同时,写线程向95T发送数据。如果接受和发送的数据一致,则测试通过。测试结果如图4所示。

4 结束语

随着现代半导体产业的发展,嵌入式双核系统必将迎来广阔的发展。本文系统地介绍了一种CPU和 FPGA双核通信接口的设计方案,实现并验证了数据的双向传输。