基于AHDL语言的篮球赛24秒倒计时器设计

2019-04-26钟鹏程

文/钟鹏程

1 引言

随着篮球运动的普及和NBA比赛在世界的风靡,篮球比赛的24秒倒计时器已被广泛采用。AHDL语言是一种支持Altera公司器件的硬件描述语言,是一种模块化的高级语言。AHDL语言易学、易用且功能强大,对于复杂组合逻辑电路设计与时序逻辑电路设计都完全胜任。Quartus Ⅱ是Altera公司的综合性CPLD/FPGA开发软件,拥有AHDL、VHDL、VerilogHDL以及原理图等多种设计输入形式,功能强大,界面友好,内嵌自带的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。本文基于AHDL语言在Quartus Ⅱ软件中设计了篮球赛24秒倒计时器。

2 总体方案设计

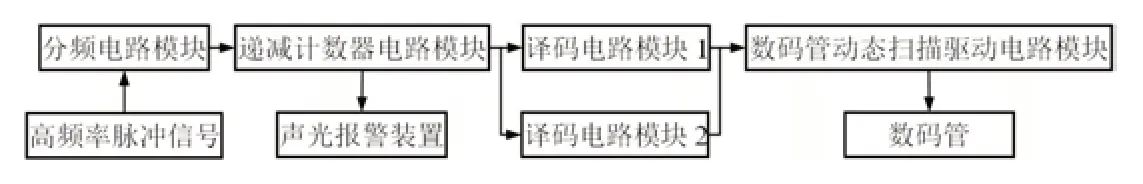

篮球赛24秒倒计时器的总体方案结构如图1所示,包括高频率脉冲信号、分频电路模块、递减计数器电路模块、声光报警装置、2个译码电路模块、数码管动态扫描驱动电路模块和数码管等。高频率的脉冲信号通过分频电路模块进行分频,输出频率为1Hz的脉冲信号(周期为1s),作为递减计数器电路模块的脉冲信号。递减计数器电路模块的输出端与译码电路模块的输入端相连,进行BCD译码,最终由动态数码管显示倒计时的时间。当显示的数字为00时,发出声光报警信号。使用AHDL语言在Quartus Ⅱ软件中设计分频电路模块、递减计数器电路模块、译码电路模块和数码管动态扫描驱动电路模块,并实现以下功能:

图1:倒计时器总体方案结构

(1)24秒倒计时显示功能,采用动态数码管显示;

(2)设置外部控制开关,控制计数器的重置24秒功能;

(3)计数器递减至0时,数码管显示“00”,同时发出声光报警信号。

3 程序设计

3.1 分频电路模块设计

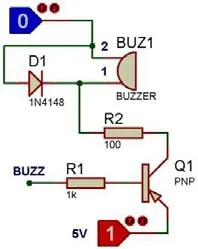

假设整个系统的输入端输入频率为40MHz的脉冲信号,分频电路模块的输出端输出频率为1Hz的脉冲信号(周期为1s),那么需要将频率分为原来的分频电路模块的输出端与递减计数器电路模块的时钟输入端相连,保证了数码管显示的数字每秒减1。分频电路模块的AHDL语言程序如下:

3.2 递减计数器电路模块设计

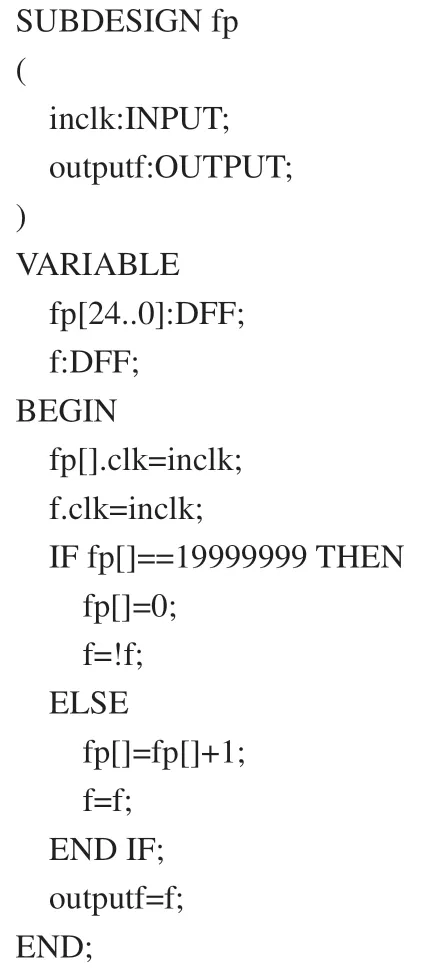

图2:蜂鸣器电路

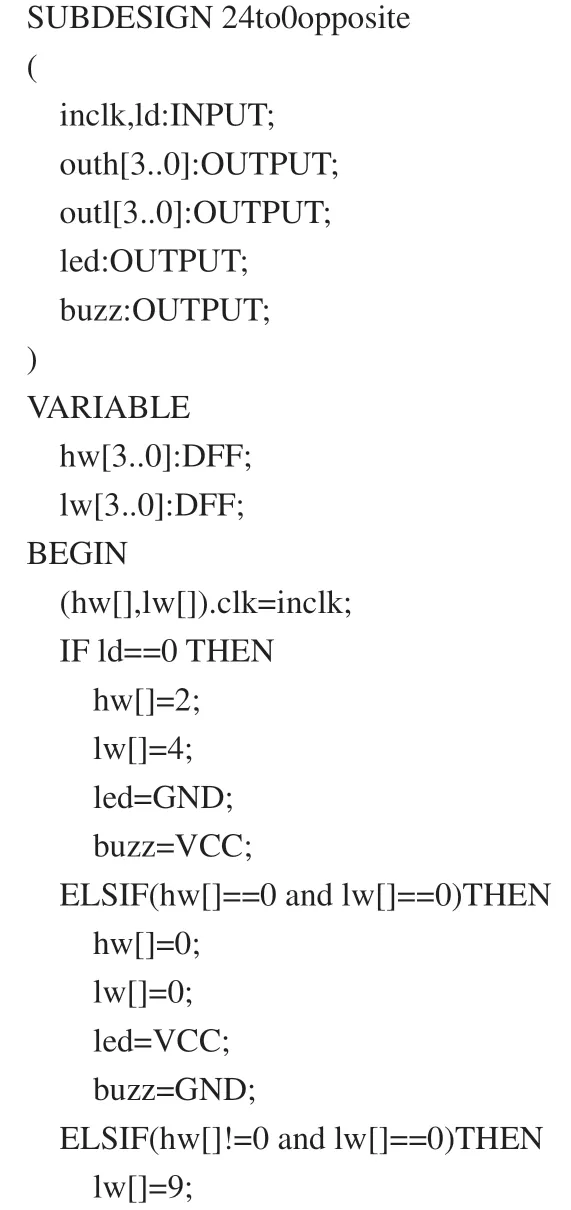

该递减计数器由24递减至0,有两个输入端,它们分别是时钟输入端和置数输入端。时钟输入端与分频电路模块的输出端相连,输入频率为1Hz的脉冲信号。置数输入端是通过人为控制的,当输入低电平时,递减计数器置数为24,当输入高电平时,递减计数器正常工作。递减计数器电路模块的一个输出端led与发光二极管相连,另一个输出端buzz用来控制蜂鸣器(如图2所示),其余的输出端与两个译码电路模块的输入端相连。递减至0之前,发光二极管不亮,蜂鸣器不响;递减至0以后,发光二极管变亮,蜂鸣器发出声音,即发出声光报警信号。递减计数器电路模块的AHDL语言程序如下:

3.3 译码电路模块设计

译码电路模块的输入端与递减计数器电路模块的输出端相连,输出端与数码管动态扫描驱动电路模块的输入端相连。译码电路模块的AHDL语言程序如下:

3.4 数码管动态扫描驱动电路模块设计

所谓数码管的动态驱动,就是把每个数码管的“段”对应并联,这样所有数码管的“段驱动”只使用7根驱动线。同时用输出扫描脉冲控制每个数码管的COM端,在一个瞬时只让一个数码管被点亮,且每个数码管轮流被点亮(一个数码管一般点亮时间为1-5ms)。如此循环不断。由于人眼有视觉残留效应,若各数码管循环点亮的速度足够快,则人眼看到的是多个数码管都被点亮了起来。数码管动态扫描驱动电路模块的输入端与两个译码电路模块的输出端和40MHz的时钟脉冲信号相连。将时钟脉冲信号分频,得到频率为1KHz的脉冲信号,即周期为1ms的脉冲信号,所以每个数码管被点亮的时间为1ms。与数码管的静态驱动相比,数码管的动态驱动使用的引脚较少,电路功耗较低。数码管动态扫描驱动电路模块的AHDL语言程序如下:

4 结果分析

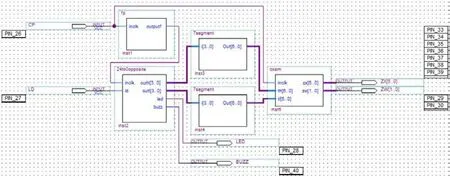

在Quartus Ⅱ软件中,创建4个扩展名为.tdf的文件并完成AHDL语言程序设计。创建1个扩展名为.bdf的文件(原理图输入文件),为4个tdf文件创建符号文件,即在bdf文件的元件库中生成相应的可调用的元器件,通过调用这些元器件生成如图3所示的电路,并进行引脚分配。确定编译无误后,将扩展名为.pof的文件下载到CPLD中,选用的CPLD型号为MAX Ⅱ EPM240T100C5。按照定义好的引脚连接好电路,并增加一个独立按键电路来控制引脚LD输入的高低电平,如图4所示。按下按键,引脚LD端为低电平,此时数码管显示数字24,负责报警的发光二极管不亮,蜂鸣器不发出声音。再松开按键,引脚LD端为高电平,此时数码管显示的数字开始倒计时,即每隔1秒,数码管数字减1。当数码管显示的数字为00时,数码管显示的数字不变,负责报警的发光二极管由不亮变为亮,蜂鸣器发出声音。在任意情况下,按下按键,引脚LD端为低电平,都会使数码管显示的数字重置为24。这样的篮球赛24秒倒计时器可以应用到篮球比赛中,帮助裁判判断参赛者是否24秒违例。

图3:倒计时器电路图

5 结束语

在本文提出的篮球赛24秒倒计时器总体方案基础上,采用AHDL语言详细设计了分频电路模块、递减计数器电路模块、译码电路模块和数码管动态扫描驱动电路模块,分析了电路的工作原理。在Quartus Ⅱ软件中完成24秒倒计时器设计,将扩展名为.pof的文件下载到CPLD中,并完成实物的电路连接,实现了24秒倒计时、随时置数、自动报警等功能,达到了预期的设计效果。