基于FPGA的1090ES ADS-B信号发生器设计

2019-04-12王婷琦卢起斌

王婷琦,卢起斌

(中国传媒大学 广播电视数字化教育部工程研究中心,北京 100024)

1 概述

ADS-B(Automatic Dependent Surveillance-Broadcast,广播式自动相关监视)是一种基于全球卫星定位系统(GNSS)和空-空、地-空数据链通信的航空器运行监视技术[1]。ADS-B发射系统能从机载的卫星导航设备获取当前的位置信息,连同本机的身份编码、气压高度、航速、航向、航行意图等信息一起,以数据链的形式,实时、自发、周期性的对外广播。地面监视设备通过地-空数据链通信的方式获得该航空器的相关信息,达到空域监视的目的。

1090ES(1090MHz Extended Squitter)由美国麻省理工学院林肯实验室研究提出,是一种基于S模式扩展应答机的技术。S模式应答机采用脉冲位置编码(Pulse Position Modulation,PPM),下行频率1090MHz,传输速率可以达到1Mbps,提供空-空、地-空数据链,适合高速率数据的传送。

2 总体设计

从功能处理划分,ADS-B发射系统由GPS接收模块、基带信号生成模块、射频调制模块和放大滤波模块四部分组成,其组成框图如图1所示。

图1 ADS-B发射系统的组成框图

GPS接收模块接收GPS信号,获取该信号发生器自身的位置信息、速度信息和精确的时间信息等定位数据;基带信号生成模块是信号发生器的核心,它提取GPS接收的定位信息和自身的身份、状态等信息进行格式分解、编码、组装等处理,按照标准数据帧的格式生成ADS-B基带信号,并以特定的速率发送给射频调制模块;基带信号在射频调制模块进行ASK调制到1090MHz载波上;在放大滤波模块将射频信号进行带通滤波、功率放大等处理,由全向天线以广播的形式向周边空域进行信息发送。

本设计根据模块化设计、方便灵活应用的设计原则,只完成图1框中三部分内容,放大滤波模块不在设计范围之内。

3 硬件电路设计

3.1 GPS接收模块

GPS接收部分使用第三方GPS模块,用于获取ADS-B信号发生器自身的定位数据。本设计选择u-blox公司的NEO-7N模块,其性能指标如表1[2]所示,该芯片具备出色的定位精度与锁定时间性能,同时功耗低,外形尺寸小,适用于本设计需求。

表1 NEO-7N的性能指标

GPS接收模块通过UART串口与基带信号生成模块进行通信。上电后,FPGA首先配置GPS模块,使其输出数据转换为UBX格式,并只输出位置、速度、时间(PVT)三种数据包,便于Nios II软核处理器接收处理。

3.2 基带信号生成模块

基带信号生成模块的功能由FPGA完成,本设计选用的型号为EP4CE10E22。

3.2.1 ADS-B的帧格式和消息结构

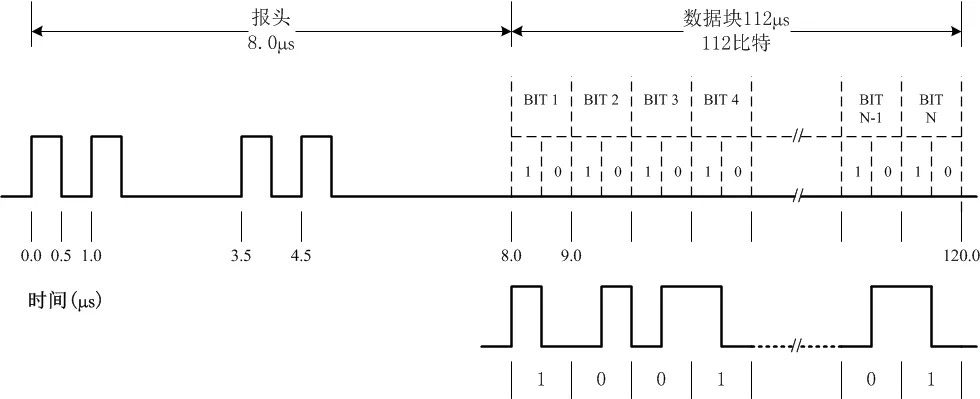

ADS-B基带信号的帧格式如图2所示,每帧由8us报头和112us数据块组成,共120us。数据块由112个比特组成,每个比特持续1us。ADS-B消息采用PPM调制:当脉冲出现在比特的前半部分时,该数据比特为“1”,否则为“0”[3]。

图2 ADS-B基带信号帧格式

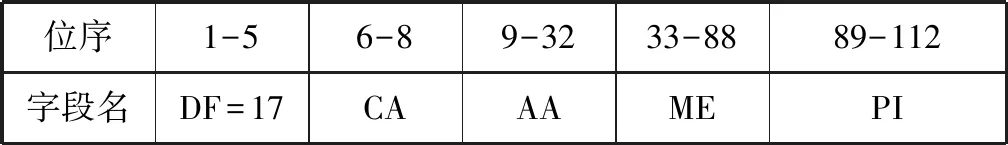

ADS-B的消息结构如表2所示,本设计采用DF=17的下行链路分配方式,每个1090ES信号包含112比特,其中56比特(位33-位88,ME字段)为ADS-B消息域,包含经纬度、高度、方位、速度等ADS-B数据消息。其余56比特分别为:5比特下行链路格式(DF:Downlink Format),3比特设备能力标示(CA:Capability),24比特ICAO地址(AA:Announced Address),以及24比特校验信息(PI:Parity/Identify)。由于消息格式简单,承载信息能力较弱,所以一个消息帧只能传输一种特定类型的信息[4]。对于不同类型的消息,其更新速率也有所不同。

表2 ADS-B消息结构

3.2.2 基带信号生成模块的搭建

基带信号生成模块是由FPGA的RTL电路和Nios II软核处理器搭建而成,如图3所示,具体实现步骤如下:

第一步:先将板载GPS模块发送的PVT数据包通过Avalon总线的UART串口读入到Nios II软核kernel内,再在kernel中将PVT信息及信号发生器的其他数据信息进行编码,组装成112比特的标准数据帧格式,按照特定速率发送给帧序列生成部分。

第二步:在帧序列生成部分,将UART串口接收到的一帧消息按字段拆分存入相应寄存器内。按照消息帧输出的时序要求,先输出固定的4脉冲报头,再依次输出DF、CA、AA、ME和PI字段。在按位取出各字段的数据比特时,进行脉冲位置编码,由计数器生成单个比特1/0对应的时序波形,产生120us的ADS-B基带信号。

图3 基带信号生成模块RTL图

3.3 射频调制模块

本设计选用ADF4351产生1090MHz的本振信号,选用射频开关HMC435AMS8G完成基带信号和本振信号的2ASK调制。

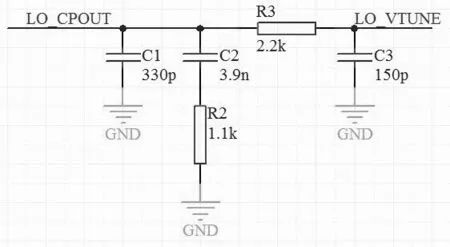

ADF4351是ADI公司推出的一款内置低相位噪声VCO的宽带频率合成器,输出频率范围为35MHz~4400MHz[5-6]。该芯片尺寸仅有5×5mm,内部集成鉴相器和VCO,外围只需再设计一个环路滤波器即可完成锁相环结构,不仅降低电路设计复杂度,也大大减少该模块的占用面积,原理图如图4所示。此外片内所有寄存器通过DATA,CLOCK,LE三线串行接口控制,简单且易于编程,本设计通过FPGA配置寄存器,可得到1090MHz的本振信号。

图4 环路滤波器原理图

HMC435AMS8G是HITTITE公司的单刀双掷开关芯片,工作带宽为DC-4 GHz,当控制端A、B分别为0V、+5V时,RF1通道输出;反之,RF2通道输出。图5是调制电路原理图,当TARGET的逻辑电平为“1”时(电平值约为+3.3V),高电平经双路反相器转换后得到0V和+5V两路电平信号,分别接通开关芯片的A、B通道,此时信号通过RF1通道输出;反之,接通RF2通道,即RF_OUT输出为零。

图5 2ASK调制电路原理图

4 系统软件设计

4.1 主程序设计流程

本文设计实现三种ADS-B消息的编码和发送:空中位置消息、空中速度消息以及身份识别和类

型消息,主程序设计流程如图6所示。

初始化内容包括:UART串口1、2初始化,分别用于Nios II与GPS、RTL的通信;ADF4351的寄存器配置初始化;CRC查找表初始化,预先计算出每个字节CRC编码的中间结果,提高运算效率;TIMER中断初始化,用于控制ADS-B消息的发送速率;消息发送缓存初始化。

图6 主程序设计流程

4.2 CRC校验编码

ADS-B帧的最后24比特为校验位PI,采取CRC校验编码,为之前的88比特信息提供检错与纠错能力。CRC的生成多项式如式(1)所示,对应的二进制表示为0xFFF409(不含最高位)。

G(x)=x24+x23+x22+x21+x20+x19+x18+x17+x16+x15+x14+x13+x12+x10+x3+1

(1)

本设计在编码时,采用单字节查表法,即以字节为单位,将每个字节的CRC校验码计算出来放入一个表中。编码时每次只处理一个字节,从表中查找对应的值后再进行下一字节的处理,直至将所有字节处理完,此时CRC寄存器存放的数据就是校验码。采用查表法可以大大提高运算效率。

设要进行CRC编码的数据流为D(i)(i=1,2n,单字节为单位),对应CRC码为R(i),余数初始值R(0),结果异或值XOR。编码步骤为:

(1)初始化查找表crcTable,便于第(3)步查表。

(2)设置CRC寄存器R,并赋初始余数值R(0)。

(3)将D(i)与R(i-1)的高8位异或,并进行查表。其中,初始i=1。

(4)将R(i-1)左移8位并与第(3)步查表得到的24位校验码进行异或运算,得到第i个字节的CRC码R(i)。

(5)重复第(3)(4)步,直到n个字节全部处理完成。

(6)最终的校验码PI由R(n)与XOR进行异或得到。

4.3 消息速率控制

ADS-B消息的最大发射频率不会超过每秒6.2个消息,即平均每秒2个空中位置、2个空中速度、0.2个身份及2个事件驱动消息,每个消息的发射是独立的且与其他消息无关[3][7]。

设计时,在Qsys中添加一个TIMER用作定时器中断,定时器节拍TIMER_TICK为200次/秒。对于不同类型消息的广播速率,以速度消息为例,要求以0.4s~0.6s范围的随机间隔进行发送,则所需定时器节拍的个数为80~120,此范围内的随机数rand可通过调用rand()函数产生,即rand = 80 + rand()% 40。当定时器节拍计数tick达到rand时,速度消息发送标志flag置1,发送空中速度消息,从而相邻两个空中速度消息的发送间隔为rand *5 ms。采用随机间隔而不是一个固定值广播发送,可以有效减少ADS-B信号之间的同步串扰,大大降低信号混叠的概率[8]。定时器中断函数流程图如图7所示。

图7 定时器中断函数流程图

5 电路实物和测试结果

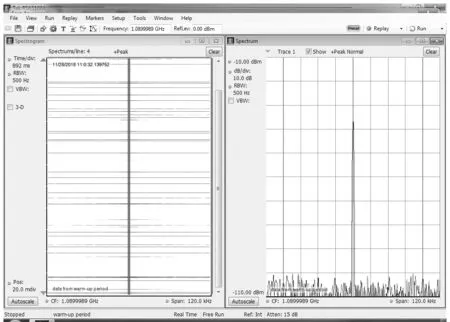

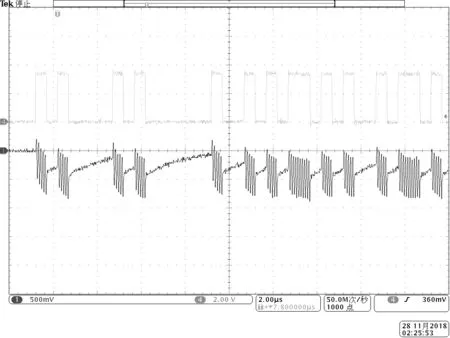

ADS-B信号发生器的电路实物如图8所示,大小仅为7.7×4.9cm;图9为射频信号的频谱图和瀑布图;图10为调制信号和射频输出波形图,均满足规范要求。使用第三方的ADS-B接收设备可正确接收和解析该ADS-B信号发生器广播的报文。

图8 电路实物图

图9 输出频谱图(右)和瀑布图(左)

图10 调制信号和射频输出波形

6 结论

本文设计的ADS-B信号发生器,可通过GPS模块获取定位数据,对外发送不同类型消息的1090ES ADS-B报文,发送速率和帧格式满足RTCA DO-260A标准要求;在结构上采用FPGA和Nios II软核架构,具有成本低、功耗低、小巧紧凑、方便集成等特点,配以相应的滤波和功放模块,即可部署在各种类型的航空飞行器上,有效助力空域安全与监管。