一种基于高速电流舵DAC的射频DDFS电路

2019-04-02于宗光张甘英苏小波

张 涛,于宗光,张甘英,苏小波,邱 丹

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

0 引 言

直接式数字频率合成器(DDFS)是一种采用全数字方式频率、相位波形合成技术的器件,它具有直接处理器控制、高速可编程配置、精密跳频与微调、稳定性好等特点,在相对带宽、频率转换时间、相位连续性和集成化等方面对比模拟信号源具有较大优势[1-3]。正是由于其频率、相位变化的连续性、配置灵活及快速可调等特性,广泛应用于相位及频率调制、频率捷变和扩频等子系统中[4],是数字雷达、电子对抗、宽带通讯、测试设备等领域的重要组成部件[5]。国内从2000年开始相继开展了DDFS器件相关技术研究,形成了速率覆盖几十MHz到2.5 GHz等几十款DDFS产品,但在高端产品方面与国外仍存在较大差距。

本设计内核采用四路数据交织架构,降低了单通路数字内核的实现难度,内部集成了电流舵DAC、LC锁相环、时钟分配电路等模块,电路采用SMIC 65nm 1P8M数模混合CMOS工艺设计制造,在时钟3.6 GHz下模拟输出频率可达1.44 GHz,单音模式下电路功耗约1.6 W,电路经测试及整机系统试用,各项技术指标达到预期目标,性能稳定。

1 总体架构

DDFS电路主要由数字内核和高速DAC构成,数字内核用于产生频率、相位、幅度可调的数字正弦信号,DAC则将数字正弦转换为模拟信号输出。传统方式多采用多级流水单路或双路输出方式,对于本设计而言该方式需要一个以3.6 GHz为时钟频率的相位累加器和相位幅度转换电路,以当下工艺水平的标准数字单元实现难度较大。

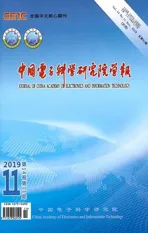

本电路采用了32级流水4路数据的交织架构方式,将3.6 GHz时钟频率的单路数字内核分解为32个子核各自独立进行相幅转换,系统以1/32fCLK频率生成相位间隔为Δθ的32路相位数据分别进行相位幅度转换。如图1 DDS相位轮所示,由相位补偿电路生成31个从支路数据,各支路与主路之间的相位差为Δθ,合成器把32路相幅转换后的数据合成四路并行数据,并输入至DAC模块。

图1 相位轮

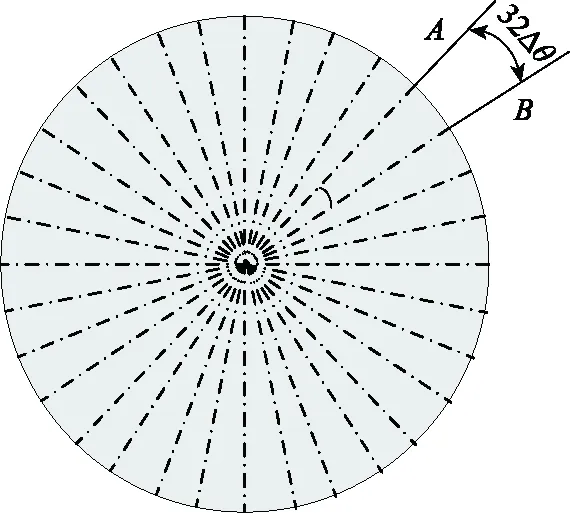

相位轮中主路和从支路的相位相互间隔构成完整的相位分辨率为Δθ的相位数据,该结构减小了时钟偏移对电路的影响并降低了硬件消耗和电路难度。同时配合四路交织数据输出, 集成了14位高速电流舵DAC进行数据合成及转换,DAC采用低10位二进制码高4位温度计码方式,译码后共25组开关信号用于控制电流源阵列,四路数据在DAC内部进行模拟方式合成,最终转换为差分输出的模拟电流,电路总体架构见图2。

图2 电路总体架构

2 DDS内核

由于以单一通路实现3.6 GHz的相位累加及转换的设计难度巨大,本设计中DDS内核采用了32个相位子核分别进行相位累加及相幅转换,每级最高转换速率只需112.5 MHz,大大降低了系统复杂度和实现难度。相位累加器采用超前进位流水线方式,累加器内部精度为48位,累加到N时刻的相位值如下式:

φN=φ0+32*FTW*N

1≤N≤248-1

(1)

其中φ0是由16位相位字POW控制的初始相位值,FTW为48位频率控制字,初始相位值由以下公式给出:

(2)

相位偏移量的单位为弧度,从式2可以看出,对于给定处于0~2π之前的任意相位偏移均可通过计算POW得到。在实际电路工作时,累加器工作到N时刻其相位值φN分解为32个连续相位关系的子相位向量,其相位值依次为φ0+32*FTW*N,φ0+31*FTW*N…φ0+1*FTW*N,并各自独立传递给后级PAC进行相位幅度转换。

相幅转换器采用的是改进的差分CODIC算法结构,该算法是目前科学计算工程主流算法之一,应用包括三角函数计算、对数和基本超越函数、复数的乘法、特征值计算及单值分解等。差分CODIC算法是一种快速有效的冗余计算算法,由H.Dawid 和H. Meyr[6]提出,保持了传统算法的精度和收敛性,可实现旋转模式和向量模式两种工作方式。但该算法需进行冗余表示法与二进制表示法之间的转换,一定程度的影响了迭代速度,本设计中差分CODIC采用混合算法结构[7-8],先采用差分CORDIC迭代完成旋转的三分之二,剩下部分再采用传统CORDIC迭代来完成,原始迭代等式如下:

gi+1=gi-uitan-1(2-1)

(3)

数据通路中的中间变量:

(4)

叠加到原始迭代等式后可得到:

(5)

数字内核在相幅转换后得到32组连续信号,并经过两级MUX后得到多路交织信号数据,由于目标速率较高,如采用传统的双路或单路传输方式[9-10]其单通路数据率将达到1.8 GSPS,无论在数字合成实现或高频相位对齐均存在很大设计难度。为解决该设计瓶颈,本电路中四路交织信号直接传输给DAC处理,同时传输的还有DCI0和DCI180两组数据时钟信号,用于DAC端的数据同步接收。

3 DAC设计

不同于常规高速电流舵DAC采用的单路或双路数据架构[11-12],本电路中为配合DDS数字内核架构,设计了一种四路交织信号传输架构,其中内嵌DAC架构及编码控制设计等是本电路的设计关键,电路DAC结构见图3所示。

图3 DAC电路结构图

DAC由输入级、译码器、相位检测及调整、混合编码器、开关及电流阵列等模块组成,采用了分段电流舵架构,编码采用了低10位二进制码和高4位温度计码的混合方式,采用了全差分结构开关电流源,输出为差分电流对。

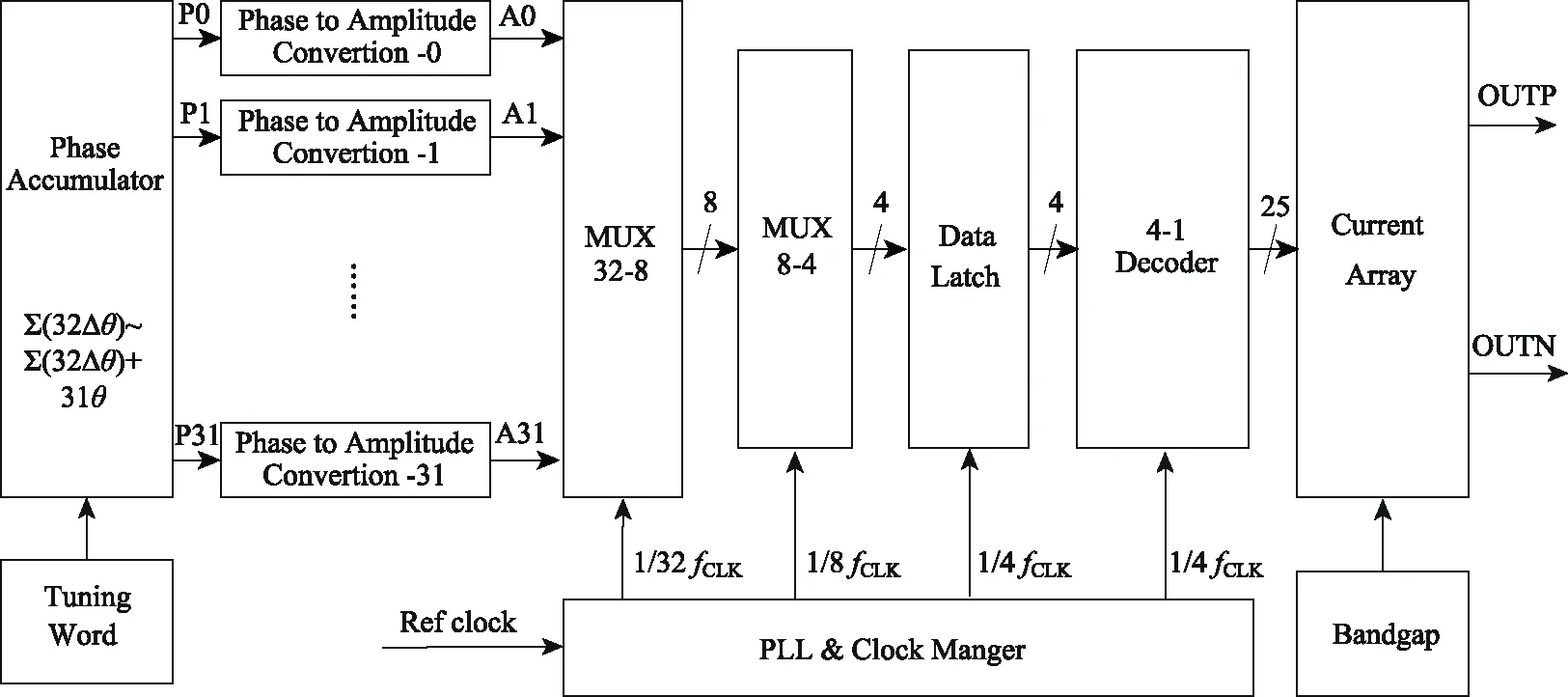

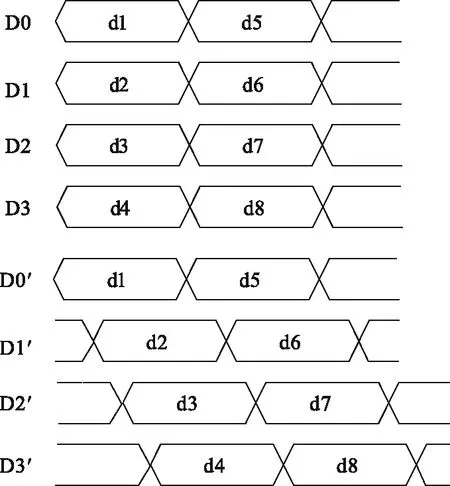

为配合DDS内核输出的四路交织信号,输入级采用的是三级采样方式,利用了DCI0、DCI180和1/4fCLK三组时钟,并利用1/4fCLK采样时钟完成了四路信号的相位偏移,具体结构见图4。

图4 DAC输入级

其中,第一级缓存寄存器时钟由数字内核提供的DCI180完成,与内核输出数据的相位差为180度,该级主要用于同步输入信号,消除传输引起的四路数据间传输失配;第二级数据D0、D1时钟采用DCI180,数据D2、D3时钟采用DCI0,这一级用于完成1,2组和3,4组数据间的180度相移;第三级四路数据分别采用由时钟管理电路提供的相位差分别为90度的四分频时钟,最终产生了90度相位差的四路数据提供给后级采样合成,输入级和最终输出信号时序如图5所示,同时加入了相位检测和延迟模块用于补偿数字时钟和模拟时钟的相位差,保证信号正确采样。

图5 输入级信号时序

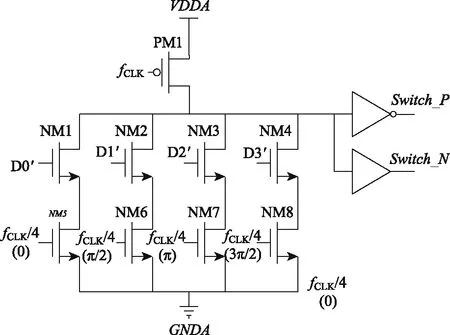

图6 MUX4-1混合编码器

由于信号频率较高,用数字方式实现困难,最终设计上采用了模拟混合编码方式来实现,结构见图6所示,D0~D3为相位错开的四路开关信号,时钟采用相位与之对应的1/4fCLK,PM1控制栅为3.6 GHz系统时钟fCLK,最终合成并为3.6 GHz的差分开关信号提供给后级的开关阵列。

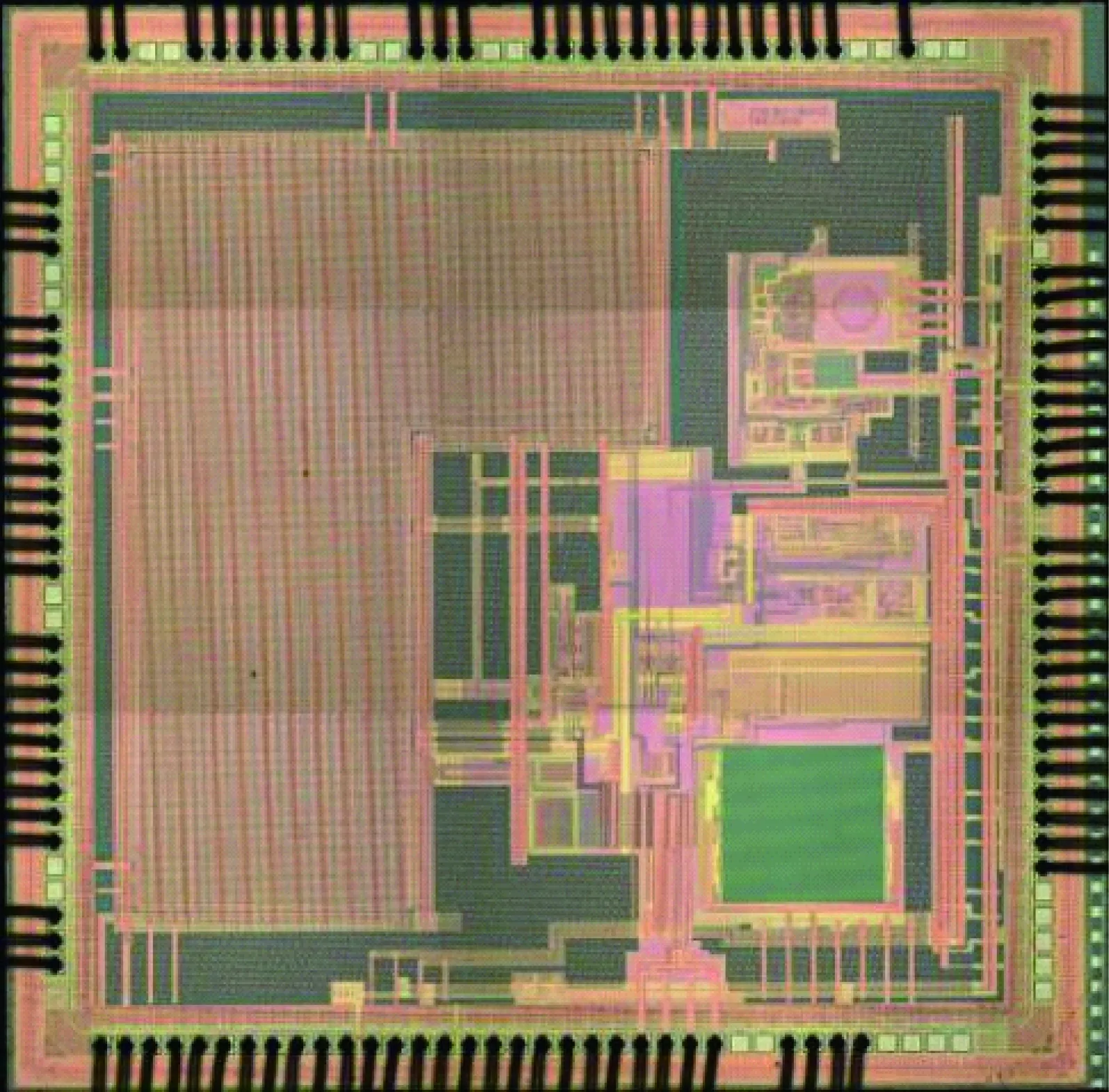

3 设计实现

电路设计实现基于SMIC公司单层多晶硅、八层金属的65 nm数模混合CMOS工艺,内核工作电压1.2 V,IO工作电压3.3 V,芯片最高工作频率3.6 GHz。图7为实物芯片照片,芯片面积为4.85×4.85 mm2,主要包括数字内核、数模转换器、锁相环等关键模块。

图7 实物芯片照片

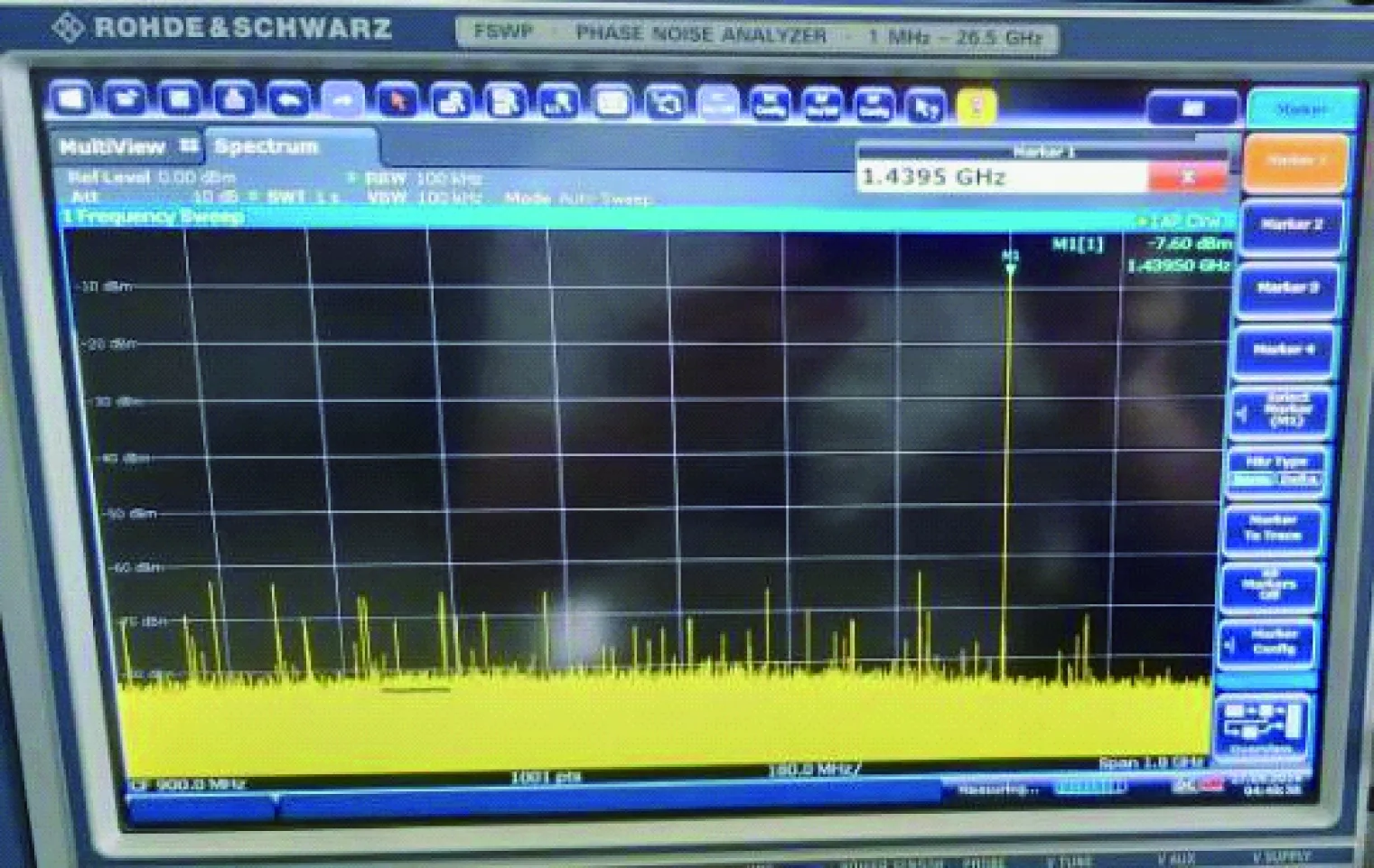

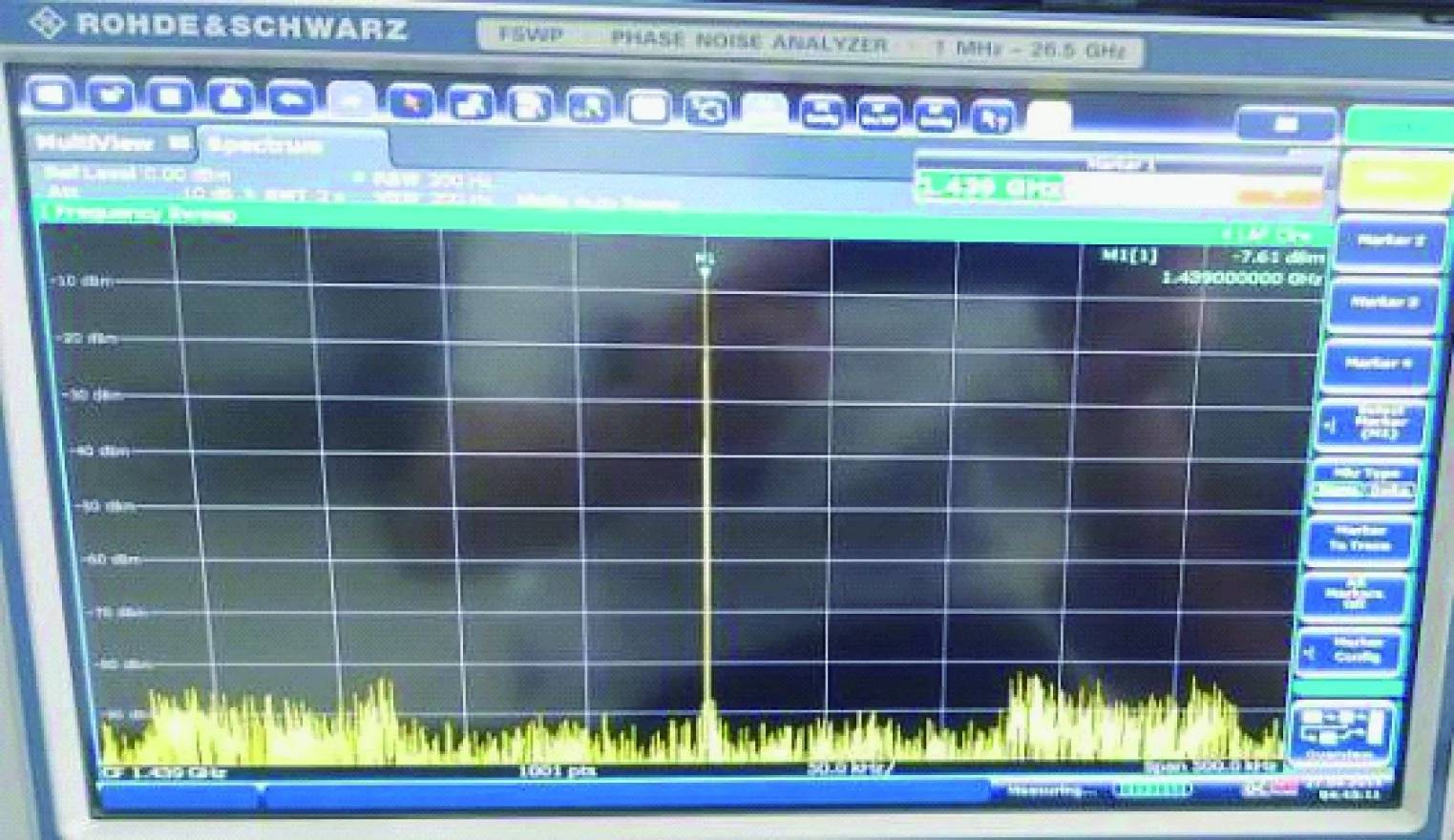

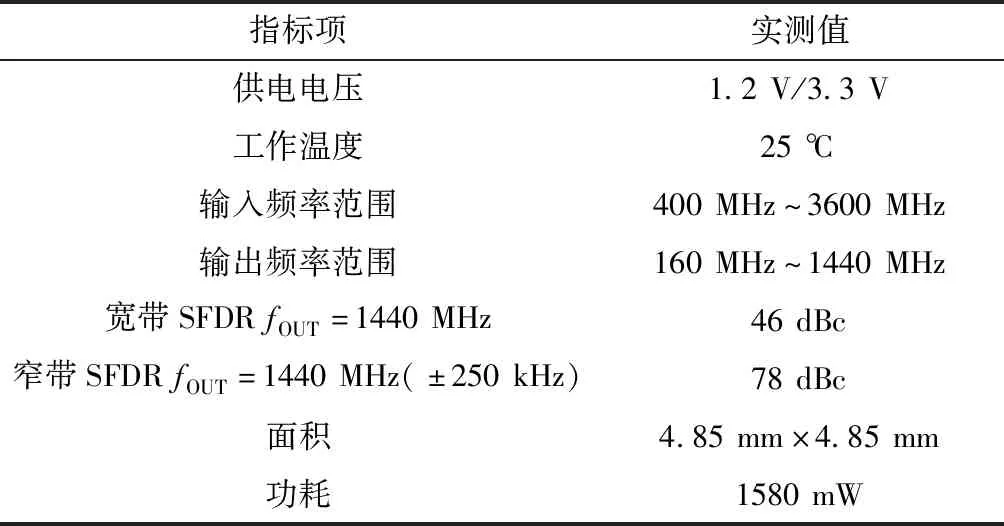

电路基于Advantest V93000 ATE测试平台完成,芯片供电及配置由测试机提供,时钟由外挂R&S SMA100A信号源提供,输出信号由R&S FSWP信号源分析仪进行频谱分析。经实际测试,在时钟采样频率3.6GHz,输出频率1.44 GHz时,宽带SFDR为46 dBc,窄带SFDR为78 dBc,图8、图9分别为FSWP下宽带SFDR和窄带SFDR的测试结果。

图8 宽带SFDR

图9 窄带SFDR

表1 电路主要参数实测值

5 结 语

本文创新的提出了一种四路交织架构,在接收级引入多相时钟,并应用相位检测模块保证高速数据与时钟的不交叠,降低了系统复杂度及数字内核的可实现性,并基于此设计了一款采用标准CMOS工艺的高性能DDFS电路,内嵌了14位高速电流舵DAC,工作电压1.2 V/3.3 V,经流片及系统试验测试验证,电路频率输出可达1.44 GHz以上,动态指标良好,具有广阔的市场应用前景。