基于VPX总线的波控系统闭环测试台

2019-03-18肖文光姚佰栋

肖文光, 姚佰栋

(1.中国电子科技集团公司第三十八研究所, 安徽 合肥 230088; 2.孔径阵列与空间探测安徽省重点实验室, 安徽 合肥 230088)

从无源相控阵雷达到有源相控阵雷达,从一维相控阵雷达到二维相控阵雷达,雷达性能日益提高,可实现功能也更强大。相应的,作为相控阵雷达关键单元的波控设备,其数量也成倍增加。波控系统通常包括波束控制计算机、波控单机、末级T/R组件等设备,分别实现控制码计算、转发、执行等功能。即使各波控单机测试没有问题,但整机装配联试过程中,由于某单个设备故障、操作失误、电缆装配不到位等原因,都可能导致雷达整个波控系统工作不正常。由于牵扯分系统过多,出了问题常常不得不整个系统逐一排查,耗时耗力,定位故障的准确性和排除故障的效率都不能满足项目开发进度的要求。

在现有雷达相关测试系统中,文献[1-2]给出了基于CPCI总线的设计方案,但由于CPCI总线最多扩展为8个槽位1725对外围I/O信号,数据带宽最大只有132 MB/s,有限的可扩展性和低数据带宽使得CPCI总线无法满足相控阵雷达波控系统闭环测试要求[3]。常用的测试总线技术中还有文献[4-5]提出的基于PXI总线的设计方案,但PXI总线具有并行总线的通病,即数据带宽和扩展能力不足。在工作频率大于133 MHz时,PXI总线可扩展槽位最多只有2个,同样无法满足相控阵雷达波控系统闭环测试要求。

本文以某相控阵雷达波控系统为测试对象,基于VPX总线I/O口丰富、可扩展性强、传输速率高等多重技术优势,采用基于RapidIO交换的高速互连技术,提出了一种基于6U-VPX总线架构的波控系统闭环测试台设计方案。

1 VPX总线特点

VPX总线是基于高速串行总线的新一代总线标准,VPX标准的具体内容在VITA 46系列技术规范中作了详细定义[6],这些技术规范及主要内容见表1所示。

表1 VITA 46系列技术规范

为获得尽可能多的对外控制引脚和更高的数据传输率,VPX总线标准采用了专为高速差分信号设计的Multi-Gig RT2连接器。Multi-Gig RT2连接器不仅连接紧密坚固,而且特性阻抗可控,插入损耗低,信号串扰小。在一个典型的6U-VPX板卡上使用了1个8列7行56引脚的RT2连接器和6个16列7行112引脚的RT2连接器,这些连接器依次被定义为P0连接器、P1连接器、P2连接器、P3连接器、P4连接器、P5连接器和P6连接器。其中,P0为公共连接器,用于传输功率、测试总线和维护总线等信号;P1为差分信号连接器,包含有40个地、32个差分对信号和8个单端信号;P2~P6既可以作为差分连接器使用,也可以作为单端连接器使用。当作为差分连接器使用时,包含有40个地、32个差分对信号和8个单端信号;当作为单端连接器使用时,包含有32个地和80个单端信号,是目前提供对外信号接口数量最多的总线。

VPX总线引入了基于RapidIO的高速串行交换结构,所使用的RT2连接器的每对金属端子支持最大10 Gbps通信数据率,所以单路数据率为1.25 Gbps、2.5 Gbps、3.125 Gbps的RapidIO信号很容易被分配到VPX的差分连接器上,构建成以串行RapidIO协议互连和交换为基础的高速底板互联结构;可以根据需要灵活地将P1的16个晶片、32对差分信号线配置成数量不同的1x RapidIO、2x RapidIO和4x RapidIO使用,其中,4x RapidIO包括4对发送差分线和4对接收差分线,可形成双向最大10Gbps的数据传输能力[7]。这种配置方式同样可以应用在P2~P6连接器上,给设计师设计大网孔拓扑结构带来极大灵活性。

2 测试台架构设计

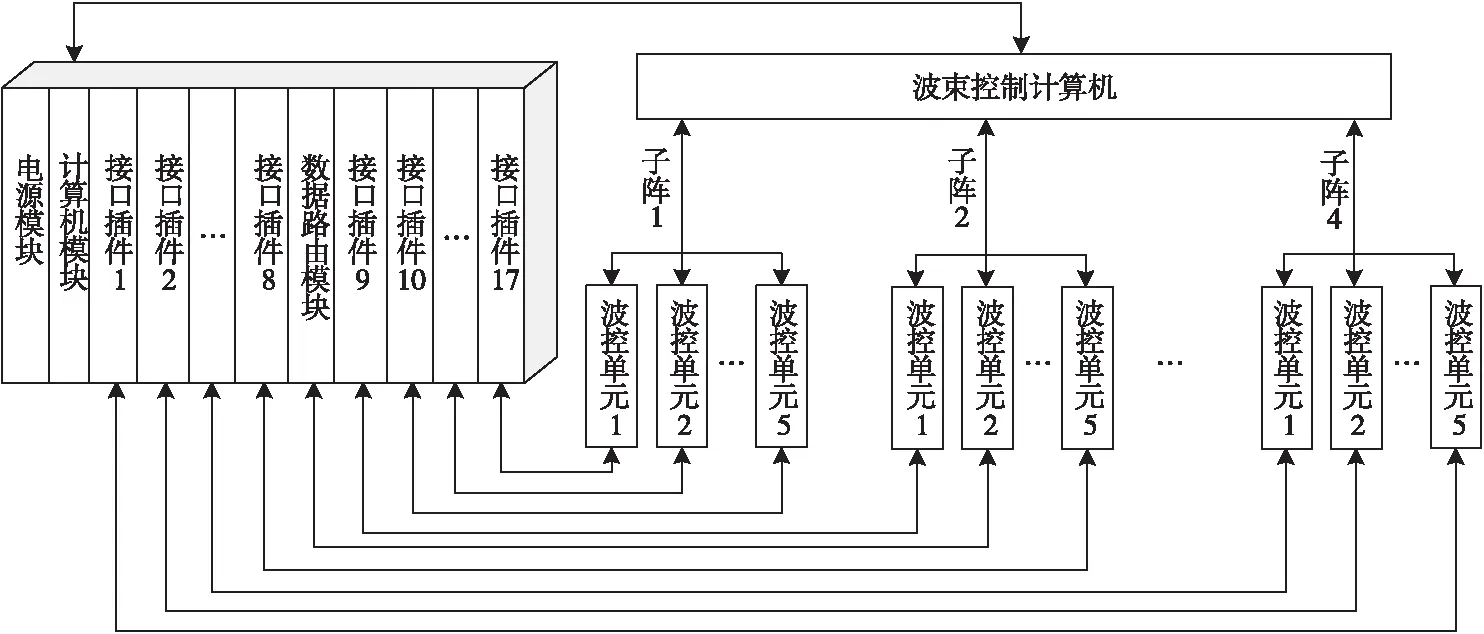

某相控阵雷达波控系统闭环测试台架构如图1所示。该波控系统主要由1个波束控制计算机和20个波控单元组成。波束控制计算机通过4路RS422串行总线与波控单元通信,采用“一拖五”总线结构。每个波控单元通过9对差分线(8对差分控制线加1对差分BITE遥测信号线)控制18个单通道T/R组件,所以可算出波控单元与接口插件后出板共有3240对差分信号相连接。

在本设计中,波控系统闭环测试台主要由符合6U-VPX模块标准的1个电源模块、1个数据路由模块及后出板、1个计算机模块、17个接口插件及后出板、1个6U高速VPX背板组成。根据peer-to-peer交换原则,数据路由模块槽位在17个接口插件槽位的中间位置。

测试台的电源模块采用交流220 V/50 Hz输入,通过内部变压转换成+12 V主电源、+5 V主电源以及+3.3 V辅助电源给其余19个模块供电。另外,还可提供一路+24 V动力电源给风扇,用于给测试台内各板卡或模块风冷散热降温,输出电源总功率为1000 W。数据路由模块用于其余板卡数据的RapidIO交换,具体数据来源包括自身后出板和17个接口插件。数据路由模块通过底板1xRapidIO通道与每个接口插件进行高速通信,传输速率为2.5 Gbps[8]。数据路由模块的后出板通过4个J30J-100TJW连接器与波控单元连接,所有的控制信号和BITE遥测信号均采用RS422差分方式。测试台中的计算机模块基于windows 7操作系统开发并安装了波控系统专用测试软件。计算机模块的主要功能包括根据用户参数设置产生对应波控参数、打码值与时序逻辑比对判断、产生BIT管理测试和错误模拟测试指令等。计算机模块与波束控制计算机通过RS422串口双向收发,最大传输速率为10 Mbps[9]。由于计算机模块与数据路由模块之间的数据传输比较集中,为避免等待保证实时传输,所以设计中采用了4xRapidIO高速通道,传输速率为10 Gbps。测试台的接口插件数量最多,其设计完全相同,方便维修替换。每个接口插件通过1x RapidIO与数据路由模块建立通信链路,对外接口通过其后出板出线,后出板安装方式与接口形式跟数据路由模块后出板完全相同,也是通过4个J30J-100TJW连接器与波控单元连接,所有的控制信号和BITE遥测信号均采用RS422差分方式。

除了和数据路由模块通信的一对RapidIO信号外,每个接口插件实际可对外连接190对差分信号。除了8对4x RapidIO差分信号和17对1x RapidIO差分信号,数据路由模块有150对差分信号可用于对外接口,所以该测试平台对外扩展接口共有3380对差分信号,满足该相控阵雷达波控系统闭环测试需要3240对差分信号的要求。

图1 波控系统闭环测试架构示意图

3 测试过程

波控系统测试台通过自闭环收发完成对波控系统的遥控和遥测,并通过数据比对自动定位故障点。具体测试过程包括前向测试和后向测试两种,前向测试属于遥控功能测试,后向测试属于遥测功能测试,下面分别阐述这两种测试的具体过程。

3.1 前向测试过程

前向测试的主要目是根据设定参数进行打码测试或控制时序测试。前向测试开始时,由计算机模块通过RS422串口发参数给波束控制计算机,具体测试过程如下:

1)给电源模块通电,计算机模块通过RS422串口将重频、方位角度、俯仰角度等波束指向控制值发送给波束控制计算机,参数设置界面如图2所示;

2)波束控制计算机收到上述参数值后计算全阵各T/R通道打码值,或产生正确的控制时序,然后将全部打码值或控制时序通过4路RS422总线同时发送给20个波控单元,传输速率为5 Mbps;

3)20个波控单元对自身接收到的打码值分别进行校验,或对控制时序的逻辑相关性、时间宽度等指标进行验证,若没有错误则根据T/R组件数据格式要求将打码值按顺序截断分包,并通过RS422同步串口发送给17个接口插件和数据路由模块;若打码值有错误则记录错误标志,时序错误则强制转换为正确的时序;

4)17个接口插件模拟末级T/R组件接收打码值或控制时序,然后分别通过1x RapidIO通道再发给数据路由模块进行上传;数据路由模块自带RapidIO交换芯片可实现多路RapidIO通道自由交换,并将数据路由模块自身接收到的数据和17路1xRapidIO数据通过1路4xRapidIO发给计算机模块[6];

5)根据设定的门限判据,计算机模块将接收到的打码值与所发送打码值进行对比,或将接收到的控制时序与发送时序进行逻辑和宽度判断,对比和判断结果在测试软件上直观显示,从而完成相控阵雷达波控系统的故障自动定位。

图2 参数设置界面

3.2 后向测试过程

后向测试的主要目的是波控系统的状态遥测。这里的状态遥测包括错误模拟和BIT管理两种。为检测全阵波控对错误信息的判断和控制能力,需要在装机之前对其进行错误模拟测试。通常需要模拟的错误有数据校验错误、收发时序逻辑错误和发射触发脉冲过宽错误等。为监视全阵波控和对下级T/R组件故障状态的检测能力,需要在装机之前对其进行BIT管理测试。后向测试开始时,由计算机模块通过RS422串口发送错误模拟指令给波束控制计算机,具体测试过程如下:

1)在测试平台软件里设定或选择错误指令类型,并和其他参数一起由计算机模块发送给波束控制计算机,通信方式为RS422串口;

2)波束控制计算机解析错误指令和波束参数,计算各T/R通道打码值或产生所需要的控制时序逻辑,并通过4路“一拖五”RS422总线同时发送给下一级20个波控单元;

3)这里T/R组件的BIT信号为高电平表示其发生故障,计算机模块模拟全部T/R通道或部分T/R通道故障,即通过4xRapidIO通道向数据路由模块发送包含360个由“0”、“1”组成的错误位的数据包;数据路由模块依据不同波控单元的地址编号将收到的大数据包分成18个小数据段;其中17个数据段分别通过17路1x RapidIO通道发送给各接口插件,再由接口插件后出板发送给所对应的19个波控单元,还有1个数据段是通过其自身后出板发送给对应波控单元;

4)通过上位机测试软件发送BIT管理测试指令,计算机模块会通过RS422串口向波束控制计算机发送BIT测试命令帧;

5)波束控制计算机收到BIT测试指令,通过4路“一拖五”RS422总线同时向20个波控单元发送读数据时序,读操作以读使能信号STROBE下降沿开始,读数据期间保持低电平,上升沿结束读操作;20个波控单元根据读操作时序将处理过的打码值错误(例如数据校验错误)、收发时序错误(例如收发时序组合错误、发射触发脉冲过宽错误等)、T/R组件故障等BIT信息一起组成遥测数据帧回送给波束控制计算机[10];

6)波束控制计算机收到全部BIT数据信息后通过RS422串口发送给计算机模块进行判断,判断结果自动在测试软件上显示并存档,从而完成波控全阵错误模拟和BIT管理测试,图3给出了某一个波控单元的故障或错误测试显示界面。

图3 故障显示界面

4 性能分析

本文的波控系统由1个波束控制计算机、20个波控单元、360个末级波控组件以及若干互联电缆组成。单机的测试是在基于CPCI总线的测试台上完成的。依据各单机调试时间统计结果,波束控制计算机的平均调试时间为0.5小时,单个波控单元的平均调试时间为0.3小时,末级波控和组件射频功能一起进行调试,其平均调试时间为0.2小时,则波控系统调试时间合计为78.5小时。忽略互联电缆故障,按照每天调试10小时计算,则完成波控系统故障排查需要7.85天。在本设计所述测试台中,前向测试和后向测试都是由计算机自动完成的,并且自动给出各单元设备的故障信息和位置,所以故障定位的时间可忽略不计。找到故障位置后,排除故障的时间取决于单机的调试时间,发生故障的单机设备种类和数量不同,排除故障所需时间也不同。根据该闭环测试台实际使用经验,总体上波控系统的调试时间已缩短到一天以内完成,波控系统的调试效率得到显著提高。表1给出了对波控单元1及其所控制的18个组件进行错误模拟和BIT测试的后向测试数据。

表2 后向测试结果

5 结论

基于VPX总线的波控系统闭环测试台已在实际项目中得到应用,并在多个产品中得到借鉴使用。与传统的基于CPCI总线的测试台相比,该测试台在数据传输带宽、对外接口数量、可扩展性等方法都具有明显优势,不但满足了电路输入输出信号的自动控制和测试要求,而且大幅降低了系统的测试时间,节约了大量人力资源。该测试台可根据测试电路需求对后出板接口形式进行调整和扩充更新,非常适合不同雷达波控系统的试验测试,便于设计师快速构建适合自己项目的测试系统。